计算机基础知识——计算机概述

1、计算机的发展史

1.1、第一代计算机

第一代计算机——电子管计算机(1945年~1957年)。

说到电子管计算机就不得不提到二极管的诞生。在初中或高中的时候,我们就接触过电流、电压、电阻等相关知识。在了解二极管之前,我们先了解几个基本概念。

1.1.1、电流、电压、电阻

话说,很早的时候牛顿发现了万有引力,在1687年出版的《自然哲学的数学原理》一书中首先提出的。不过在他的著作中从来没有提及引力产生的原因。

引力是由有质量的物质产生,物质又是由原子组成的,原子是组成物质所有元素的基本单位,原子又是由原子核(质子、中子)以及环绕其高速旋转的电子(带负电)组成。

电流,是电荷(带正/负电的粒子,异性相吸,同性相斥)的定向移动产生的。电荷运动产生的能量场的叫库伦电场(变化的磁场产生的叫感生电场)。就像我们日常生活中的电池,电池的两端分别聚集了大量的正负电荷(正(电势高)->负(电势低),这种电势差,也称为电压),他们的电场(电势差)就是推动电荷移动的这股神秘力量。处于这个电场的物质中的电子就会形成电流。

那为什么不同的物质导电性不同呢?比如金属和木头,这是由于不同物质的原子核对核外电子的束缚不同。只要在金属两端稍加电场力,电子就会轻易挣脱原子核的约束形成稳定的电流。原子核对电流的阻力,就是我们说的电阻。

安培定律:是一个电磁定律,它表示电流和电流激发磁场的磁感线方向间关系,也叫右手螺旋定则。

欧姆定律:德国物理学家乔治·西蒙·欧姆1826年4月发表的《金属导电定律的测定》论文提出的。在同一电路中,通过某一导体的电流跟这段导体两端的电压成正比,跟这段导体的电阻成反比(I=\frac{U}{R} )。

焦耳定律:电流通过导体所产生的热量与电流的平方成正比,与导体的电阻成正比,与通电时间成正比(Q={I^2Rt} )。这也是为什么短路会发热甚至起火的原因,电流越大发热越明显。

1.1.2、电子管诞生

在1877年,爱迪生发明碳丝电灯之后,因为碳丝难耐电火高温,使得碳丝电灯的使用寿命并不长。爱迪生千方百计设法改进,1883年他突发奇想:在真空灯泡中放置一个铜片,也许可以阻止碳丝蒸发,延长灯泡寿命,但是发现一个很奇怪的现象,铜片没有直接接入电路但是产生了电流。这是一件不可思议的事情,敏感的爱迪生肯定这是一项新的发现,并想到根据这一发现也许可以制成电流计、电压计等实用电器。为此他申请了专利,命名为“爱迪生效应”,便没有再去进行深入研究了。

1884年,爱迪生向一个英国物理学家弗莱明展示了“爱迪生效益”,然而这一切都被弗莱明看在眼里。

1896年,马可尼无线电报公司成立,弗莱明被聘为顾问。在研究改进无线电报接收机,出现了爱迪生效应,他接过爱迪生的接力棒,仔细研究了这个现象,发现爱迪生效益其实很简单,灯泡通电后,灯丝发光发热,进入白炽状态,此时灯丝上的电子及其活跃,加热灯丝向周围空间发射出热蒸发电子,从而在灯丝与金属片(带正电,阳极电位高于阴级)间形成电流。

如果金属片带负电(异性相斥),电子受阻,则不会产生电流。在交流电通过这个装置时被变成了直流电(只能单向流)。弗莱明把这种装有两个电极的管子叫作真空二极管,于是世界上第一个二极管就此诞生。并于1904年11月16日在英国取得专利。

再后来也就是“无线电之父”——李·德弗雷斯特,将Z型导线装入真空管内之后,只要把一个微弱的变化电压加在它的身上,就能在金属屏板上接收到更大的变化电流,其变化的规律完全一致——德弗雷斯特发现的正是电子管的“放大”作用。

接着,他又把导线改用像栅栏形式的金属网,于是,他的电子管就有了三个“极”——丝极、屏极和栅级,其中那个栅极承担着控制放大电信号的任务,无线电就能实现更远距离的传输。1907年,德弗雷斯特向美国专利局申报了真空三极管(电子管)的发明专利。

二战期间,美国和德国都需要精密的计算工具来计算弹道和破解电报获取情报,但是这个计算非常复杂,耗时又耗力,在战争期间,时间就是胜利,在当时的大环境下以及美军的资助下,宾夕法尼亚大学的William Mauchley和他的学生J.Presper Eckert建造了ENIAC,1946年2月,世界上第一台通用电子数字计算机“埃尼阿克”(ENIAC)在美国研制成功。将计算弹道的时间缩短至30秒内,它由17468个电子个电子管组成,是一台又大又笨重的机器,体重达30多吨,占地有两三间教室般大。ENIAC是通过用真空三极管让计算机通过控制栅极电流,效率是机电计算机的上千倍。

第一代电子管计算机(真空电子管计算机),主要用于军事研究和科学计算,但存在很多的毛病,但凡有一个真空管烧坏了机器就不能运行,必须人为的把烧坏的真空管找出来,所以制造、维护、使用都非常困难。

1.2、第二代计算机

第二代计算机——晶体管和大型机(1958年~1963年)。

由于电子管体型较大,且功耗极高,电子管容易烧毁而失效。终不能适应微电子信息化发展,于是就出现了晶体管。

1945年,肖克利开始用半导体来开发一种新的电子放大器。半导体材料的导电性不足以让它成为导体,但又不够绝缘也不属于绝缘体(硅、锗以及氮化镓[硅以外的新一代半导体材料],最外层电子有四个)。聪明但又冷漠的肖克利选择在家办公,让同事沃特·布拉顿与约翰·巴丁在新泽西州的贝尔实验室自由地开展实验。

1946年,著名的计算机先驱格雷斯赫柏,以一种有趣的方式在日志中使用这个词,操作员在使用MarkII和MarkIII 计算机时,因为一只飞蛾卡在继电器中而出现错误,于是就用到了bug(虫子),bug(特指故障、程序错误)一词就已经是工程方面的行话了。

1947年11月,布拉顿的一次偶然发现,让理论物理学家巴丁对电流在半导体表面的行为有了关键性的新理解。布拉顿用塑料、金箔和半导体锗拼凑出了一件放大器,并进行了测试。这个放大器成功了,能用很小的输入电压来控制庞大的电流。这是史上首个晶体管。

但直到1951年肖克利改进了这个设计,人们才意识到它的重要性,后来又出现了三极管NPN。

1954年,美国贝尔实验室研制出了第一台使用晶体管线路的计算机,取名为“崔迪克”(TRADIC),装有800个晶体管。

之后在20世纪50年代和60年代里,诞生了更多晶体管计算机。晶体管计算机的一个关键优势是体积小,比真空管计算机要更紧凑。

1956年,肖克利、巴丁和布拉顿共同获得了诺贝尔物理学奖。

1958年,IBM公司制成了第一台全部使用晶体管的计算机RCA501型。第二代计算机才算是正式登上了舞台,相较于电子管,晶体管体积更小,且工作电压很低,寿命更长、效率更高。

二代计算机主要用于科学和工程计算,如解偏微积分方程,大多是使用FORTRAN语言和汇编语言和IBSYS系统。

1.3、第三代计算机

第三代计算机——集成电路(IC)和小型机(1964年~1970年)。

1958年,德州仪器与仙童公司先后研制出集成电路IC,就是采用一定的工艺技术把一个电路中所需的晶体管、二极管、电阻、电容和电感等元件及布线互连在一起(封装),这是一个巨大的进步。

随着半导体微芯片(即硅片)的发明,以及集成电路的快速发展,也推动了第三代电子计算机的诞生。

1964年,美国IBM公司推出采用了集成电路的IBM-360型计算机,标志着第三代计算机问世。采用中、小规模集成电路制造的第三代电子计算机开始出现。

第三代计算机中使用的最早的集成电路尽管集成了几十个三极管、电阻等元件,即使是LSI(大规模集成电路)也只能集成1000个左右,但是相比第二代计算机10cm左右的印刷电路板相比,只需要1毫米就能实现相同的功能。

1965年,为了让更多人用上计算机,麻省理工学院,贝尔实验室和通用电气公司共同研发分时多任务操作系统 Multics(UNIX的前身),后因Multics难度太大,项目进展缓慢。

1.4、第四代计算机

第四代计算机——个人计算机和移动终端(VLSI-超大规模集成电路,1971年~至今)。

1971年Intel研制出了MCS-4微型计算机——CPU为4040的四位机。随后,Intel又推出了MCS-80型——CPU为8080的八位机。

1978年到1983年,十六位微型计算机开始蓬勃发展,这一时期的顶峰产品是APPLE公司的Macintosh和IBM公司的PC/AT286微型计算机。

在Goug Engelbart发明图形用户界面后,Apple公司发现GUI有潜在价值,于是就设计带有GUI的苹果计算机,但由于Apple公司封闭的市场策略,与其它PC不兼容。这使得Apple公司错过了一次一统全球PC的好机会。

1981年,IBM设计了IBM PC找到Bill Gates,希望Bill Gates能提供操作系统(Bill Gates购买了DOS系统),IBM PC配合Intel CPU和DOS在市场中得到广泛应用。

1985年,微软推出了第一版的Microsoft Windows;

1995年,发布了Windows 95,是一个混合的16位/32位Windows系统。

1998年,Windows 98发行,底层仍大量使用16位的Intel汇编语言。

2000年,Windows NT和Windows 2000的失败让微软发布了Windows 98的另一个版本,名为Windows Me。

2001年,微软发布了Windows 2000的一个升级版称为Windows XP,基本替代了Windows所有的原先版本。

2007年,Windows Vista于1月30日正式发行,这是Windows版本历史上间隔时间最久的一次发布。

2009年,Windows 7发布,该操作系统就受到了外界的一致好评。

2012年,Windows 8正式推出,然而,由于Windows 8的用户界面过于复杂受到了外界不少的批评。

2015年,微软发布Windows 10正式版。

2021年,6月24日,微软发布了Windows 11,并且在10月5日正式发行;

2、计算机的体系结构

2.1、冯·诺伊曼体系结构

2.1.1、冯·诺伊曼精彩的一生

冯·诺依曼,计算机科学家、物理学家,20世纪最重要的数学家之一。他在现代计算机、博弈论、核武器和生化武器等领域内的科学全才之一,被后人称为“现代计算机之父”、“博弈论之父”。

他从小就在数学领域有着惊人的天赋。六岁时,就能心算做八位数除法,八岁时掌握微积分。十二岁就读懂领会了波莱尔的大作《函数论》要义。在17岁那年,他发表了第一篇数学论文。

但是,他的父母觉得研究数学,并不赚钱,于是希望冯·诺依曼放弃数学(因为那个时候,化学领域比较挣钱,当时的诺贝尔家族便是如此)。后来冯·诺依曼与父母达成了一个协议,就是同时注册三所大学,完成三所大学的学业。于是他开始在苏黎世联邦理工学院学习化学工程,同时每天晚上还完成柏林大学数学专业的作业。

1926年,年仅22岁的他获得苏黎世联邦工业大学化学学位,还通过了布达佩斯大学大卫-希尔伯特坐镇的数学博士答辩。

1927-1929年冯·诺依曼相继在柏林大学和汉堡大学担任数学讲师,从此到美国定居,期间运用数学知识为量子力学提供数学模型,又使他在理论物理学领域占据了突出的地位;

1930年接受了普林斯顿大学客座教授的职位;

1931年,他成为普林斯顿大学终身教授;

1933年,转入普林斯顿高等研究院,和爱因斯坦、数学家维布伦、数学家亚历山大一起成了高等研究院最初任命的四位教授(冯·诺依曼是教授里最年轻的一位),并在这里工作了一生。

后来有个人叫图灵,他想象着一种虚构的“图灵机”来证明希尔伯特的第三个命题。他的导师推荐图灵去普林斯顿大学,做阿隆佐·邱奇的博士生。

1936年9月,图灵应邀来到普林斯顿高等研究院学习。图灵的论文一发表,敏锐的冯·诺伊曼已经嗅到了图灵机广阔的远景。后来他的研究重点有两项,一是“精细内存”,二是“二进制”。他把存储程序当成数学来对待。

1944年,戈德斯坦偶遇冯·诺依曼,并向他透露摩尔工程学院电子计算机课题及研究进展。

在ENIAC(电子数字积分和计算机)尚未投入运行前,冯·诺依曼被ENIAC项目吸引,意识到了大幅提高计算能力的必要性,就已开始准备对这台电子计算机进行脱胎换的改造。在短短10个月里,冯·诺依曼迅速把概念变成了方案。新机器方案命名为“离散变量自动电子计算机”,英文缩写EDVAC。

1945年6月,冯·诺伊曼与戈德斯坦、勃克斯等人,联名发表了一篇长达101页的报告,即计算机史上著名的“101页报告”,这就是著名的“关于EDVAC(离散变量自动电子计算机)的报告草案”。这份报告是现代计算机科学发展史上具有里程碑意义的文献。其明确规定用二进制替代十进制运算,报告提到了二进制的优点,并预言,二进制的采用将大大简化机器的逻辑线路。并将计算机分成五大组件(运算器、逻辑控制装置、存储器、输入和输出设备),这一卓越的思想为电子计算机的逻辑结构设计奠定了基础。

这里你可能会问,为什么采用二进制?非二进制不可吗?

并非是非二进制不可的,不同的电压确实可以表示不同的数字。一个设备随着使用次数的增加,以及受外界噪声等环境的影响,电压存储的精度会变差,可能会出现模棱两可的电压,使得结果会出现偏差。而二进制,只有两个结果,通、断,从稳定性和复杂性上就决定了二进制的优势。

1946年2月14日,世界上第一台通用计算机ENIAC(十进制,程序与计算两分离的计算机,宾夕法尼亚大学摩尔工程学院的莫奇利和艾克特研制)于宾夕法尼亚大学正式公布。

其继任者EDVAC采用二进制和冯·诺伊曼结构的计算机设计。(EDVAC于1949年8月才交付给弹道研究实验室,直到1951年EDVAC才开始运行,延迟的原因是因为莫奇利和艾克特从宾夕法尼亚大学离职,开始组建电子计算机公司并带走了大部分高级工程师。EDVAC效率比ENIAC提高数百倍,只用了3563个电子管和1万只晶体二极管,以及1024个水银延迟线来储存程序和数据,消耗电力和占地面积亦只有ENIAC的三分之一。)

后来出现了很多冯·诺伊曼结构的计算机,包括洛斯阿拉莫斯国家实验室研制的MANIAC(数学分析数值积分计算机)、伊利诺斯大学制造的ILLAC等等。

并且冯·诺伊曼受聘担任IBM公司的科学顾问,帮助该公司催生出第一台存储程序的电脑IBM 701,1952正式对外发布,它是 IBM 第一台商用科学计算机。

2.1.2、冯·诺伊曼体系结构概述

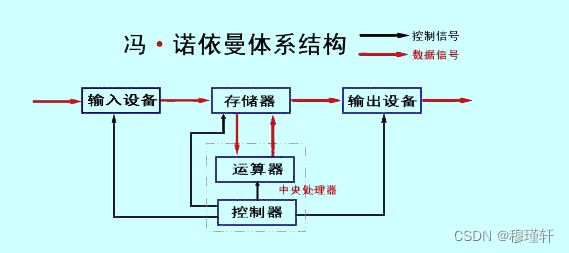

冯·诺伊曼体系结构,将计算机重新构想成三个独立的系统,用于存储数据和指令的存储器,用于解码和执行指令的中央处理单元,以及一组输入和输出接口,包含了五大组件:运算器、控制器、存储器、输入和输出设备。

1)输入设备:接收用户输入的原始数据和程序,并并转为二进制存入内存;(I:input)

2)存储器:主要用来存放数据和程序;(M:memory)

3)输出设备:将存放在内存中的数据转变为易于被人理解的表现形式;(O:output)

4)运算器:算数运算+逻辑运算;(ALU:Arithmetic And Logic Unit)

5)控制器:计算机的指挥中心。(CU:Control Unit)

冯诺依曼这一架构,将处理信息的单元(CPU)与存储信息的单元(即内存)相互分开,并允许以相同的方式在内存中存储数据和指令以及寻址。

该架构还引入了指令周期的概念:CPU从内存中取出一条指令并执行这条指令的时间总和。而周期时间的倒数——1秒钟能进行的工作次数称为时钟频率。计算机之所以能自动的完成工作,是因为CPU能从内存中周而复始的取指令、执行指令构成了一个闭环(获取指令、解码指令、执行指令、取下一条指令)。

在取指令阶段,指令是放在寄存器中的,实际上通过PC寄存器和指令寄存器取出指令的过程,是由控制器操作的,指令的解码过程也是控制器操作的。一旦到了执行指令阶段,无论是算术操作、逻辑操作的R型指令,还是进行数据传输、条件分支的I型指令,都是由算术逻辑单元操作的,也就是由运算器处理。

随着计算机技术的不断发展,现代计算机与早期冯·诺伊曼型计算机相比,在结构上有了很多的改进,但当前计算机主要还是基于冯诺依曼体系结构设计的。(关于计算机结构体系还有哈佛结构)

3、计算机系统概述

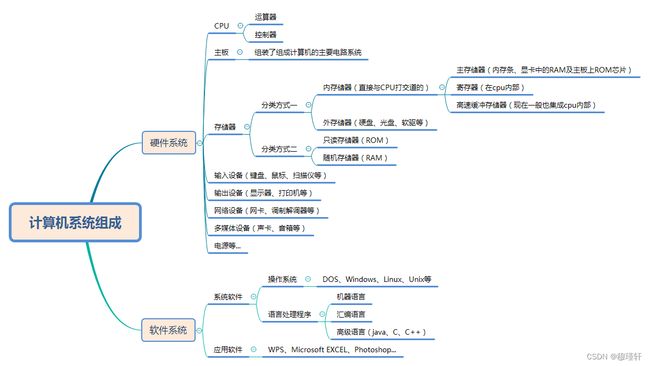

3.1、计算机系统的组成概述

我们知道计算机系统由两大部分组成:硬件系统和软件系统;

硬件系统:是指手能摸得着的实物。如:一台电脑的必要硬件包括:主板、CPU、内存条、显卡、电源,重要硬件包括:CPU散热器、硬盘等;

软件系统:由各类特殊功能的程序(是用户与硬件之间的接口)组成的软件。软件系统又分为系统软件和应用软件;

1)系统软件:控制和协调计算机及外部设备,支持应用软件开发和运行的系统,主要功能是调度,监控和维护计算机系统。

2)应用软件:为了某种特定的用途而被开发的软件。

3.2、CPU

3.2.1、什么是CPU

CPU(Central Processing Unit),即中央处理器,由运算器和控制器组成(当然还包括若干寄存器、高速缓冲存储器、以及实现它们之间联系的数据、控制及状态的总线)。是信息处理、程序运行的最终执行单元,在一定范围上控制并管理着其他硬件。简单的说,就是按照我们的指示或者编程进行操作,通过解析计算机指令来处理计算机软件中的数据。

其中,控制器的功能是负责协调并控制计算机各部件执行程序的指令序列,包括取指令、分析指令和执行指令;运算器的功能是对数据进行加工。

3.2.2、CPU的起源

1971年1月Intel公司的工程师霍夫发明了世界上第一款商用计算机微处理器4004,使得Intel成为了一家微处理器公司。这款4位微处理器虽然只有45条指令,每秒也只能执行5万条指令,频率只有108KHz,甚至比不上世界第一台计算机ENIAC。但它的集成度却要高很多,集成晶体管2300只,一块4004的重量还不到一盅司(28.350克)。采用4004芯片后,再配用一块程序存储器,数据存储器,移位寄存器,再加上键盘和数码管,就构成了一台完整的微型计算机。但是这款芯片的反响确不是很大,可能因为处理能力有限。

1972年,Intel公司又推出了8008微处理器,英特尔在这款微处理器上还首次采用了处理器的指令技术,使得8008的性能是4004的两倍,但频率依旧保守地定在200-800KHz之间,使用10微米工艺制造的8008的性能并没有打动消费者们。

1974年,发布8080处理器,8080有幸成为了第一款个人计算机Altair的大脑,数月内,Altair的销售量达到数万台。

1978年,英特尔推出了首款16位微处理器----8086,这款处理器是x86架构的鼻祖。同一年推出了性能更出色的8088处理器,8088的大获成功使英特尔顺利跻身财富500强之列。

1982年,发布了80286处理器,它的地址总线扩展到了24位,也是英特尔的最后一块16位处理器。

1985年,Intel发布第一款32位X86处理器80386,集成了27万5千只晶体管,其中最关键的特性就是采用了32位地址总线最大支持4GB内存。

1989年,Intel发布了80486处理器,集成了125万个晶体管,80486最初的频率50MHz。80486上第一次出现了一级缓存,早期的80486封装了8KB缓存,使用1000nm制程。Intel还整合了FPU(浮点运算单元)。

1993年,Intel发布了Pentium(奔腾)CPU,Pentium采用了P5架构,尽管全面超越了80486,但最突出的进步是改进了FPU。一级缓存的大小提升到16KB。

1995年,Intel发布了Pentium Pro(奔腾 Pro)。

1997年,Intel发布了Pentium II(奔腾II)。AMD和Cyrix公司也推出了同档次的AMD K6-2和Cyrix MII处理器。

1999年,Intel发布了Celeron(赛扬)处理器(初期)和Pentium III(奔腾III)处理器。

2000年,AMD率先推出了1GHz的Athlon(速龙 K7)微处理器,其性能超Pentium III。而Intel在11月,发布了Pentium 4处理器,采用全新的Socket 423架构。

2003年,Intel发布了Pentium M处理器。而AMD发布了桌面64位Athlon 64处理器(K8架构)

2004年,AMD推出了Sempron(闪龙)处理器,采用Socket A接口。

2005年,Intel丢掉了手机业务,发布了桌面64位处理器,并冠以6XX系列名称,即Pentium 4 6XX。同年4月,又发布了双核处理器Pentium D(不支持超线程技术)和Pentium E(支持超线程技术)。而AMD也发布了双核速龙Athlon 64 X2。

2006年,7月Intel发布了新一代的全新的微架构桌面处理器Core 2 duo(酷睿2),其能效比最出色的英特尔奔腾处理器高出40%,且功耗反而降低40%。

2007年,11月AMD发布了基于全新K10架构的Phenom(羿龙)处理器系列。

2008-2009年,还是酷睿一代时期,Core i7 920作为第一代经典产品;2009年,Intel推出了采用LGA1156接口的i7/i5/i3处理器 ,开始首次将GPU与CPU封装进同一颗芯片之中,比如:i3-530。而AMD则发布双核(Sermpron)闪龙,在锐龙发布前这段时间,AMD始终在追赶Intel;

2011年,Intel使用32nm工艺采用了i3、i5和i7的产品分级架构,其中i3主攻低端市场,采用双核处理器架构,约2MB二级缓存,i5处理器主攻主流市场,采用四核处理器架构,4MB二级缓存,i7主攻高端市场,采用四核八线程或六核十二线程架构,二级缓存不少于8MB,此时核芯显卡进入市场。而amd 发布基于Fusion(融聚)架构的APU(CPU+GPU)产品,A4,A6,A8(俗称推土机)。

2012年,Intel发布了第三代Core i系列处理器,内部包含了图形核心、内存控制器、图形通道控制器和输入输出总线控制器,此时北桥也被集成到芯片,主板只有南桥,没有北桥。

2013年,Intel进入第四代智能酷睿处理器,此时内存还是使用的DDR3;

2015年,Intel进入第五代智能酷睿处理器、第六代酷睿桌面处理器,此时DDR4上市;

2016年-第七代酷睿桌面处理器,开始了挤牙膏之旅,主要是对主频、核心数及线程数的提升;

2017年-第八代酷睿桌面处理器;AMD发布了自己的锐龙系列;

2018年-第九代酷睿桌面处理器;

2020年-第十代酷睿桌面处理器;直到10月,AMD发布了锐龙5000系列,才逐渐扳回一点局面;

2021年-第十一代酷睿桌面处理器;直到11月发布十二代酷睿桌面处理器有了较大的改善,支持DDR5;

3.1.3、CPU的组成概述

当布尔代数在数字逻辑电路的分析和设计中得到了广泛的运用时,所有的电子元件被设计成只有两种状态开(1)、关(0),这大大简化了电路的设计。

前面我们说过晶体管的诞生,就是这个小东西的发明让三个人(约翰·巴丁、威廉·肖克利、沃尔特·布拉顿)获得了诺贝尔物理学奖。有了晶体管,也就有了开关,也就是可以设计出逻辑门(与、或、非)电路,用离散数学的说法,就是有了一个逻辑的完备集。

整个芯片设计是化零为整的过程,首先是很多个晶体管先组成逻辑门,几个逻辑门在组成寄存器和组合电路,很多的寄存器和组合电路在再组成运算电路、控制电路、存储电路等等,然后很多这种电路再组成通信计算等模块,这些模块最终组成CPU芯片。

20世纪90年代后期,电子科学和技术取得了飞速的发展,尤其是电子计算机和集成电路的广泛应用,CPU的体积也越来越小,CPU上集成的晶体管越多,其处理效率、运算速度也越快。从英特尔1971年发布的4004处理器集成了2300个晶体管,到如今苹果推出的M系列芯片(M1 Max)晶体管数量达到570亿个。

CPU的主要功能就是完成取指令和执行指令的功能,这些操作主要由运算器、控制器来承担。

当然,不同时期不同厂家的CPU实现会有所不同,主要差异体现在指令集体系结构、数据通路、以及对应CPU控制器的实现方式上,但他们的设计并不是仅仅追求性能上的极致,而是在性能和成本上的折中与权衡。

3.1.4、CPU的组成-运算器

运算器是计算机的处理中心,主要由算术逻辑单元(ALU)/浮点运算单元(FPU)+通用寄存器组(ACC-累加器、MQ为乘商寄存器、X为操作数寄存器)+专用寄存器(PSW-状态寄存器)组成。

-

算术逻辑单元(ALU)

它是以全加器为基础,辅之以位移寄存器及相应控制逻辑组合而成的电路,在控制信号的作用下可以完成二进制数据的定点算术运算(加减乘除)、逻辑运算(与或非、异或)及各种位移操作。

-

浮点运算单元(FPU)

主要负责浮点运算和高精度整数运算。

-

通用寄存器

用来保存参加运算的操作数和运算的中间结果。

ACC(Accumulator,累加器):是一个通用寄存器,为ALU提供一个工作区,可以为ALU暂时保存一个操作数或运算结果。

MQ(Multiplier-Quotient Register)为乘商寄存器;

X为操作数寄存器;

-

状态寄存器(PSW)

在不同的机器中可能有不同的规定,PSW通常用来存放两类信息,一类是当前指令执行结果的各种状态信息,如有无进位(CF位),有无溢出(OF位),结果正负(SF位),结果是否为零(ZF位),奇偶标志位(PF位)等;另一类是存放控制信息,如允许中断(IF位),跟踪标志(TF位)等。

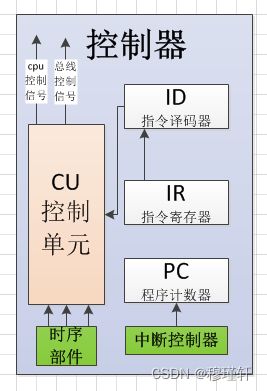

3.1.5、CPU的组成-控制器

控制器是整个CPU的指挥控制中心,决定了计算机运算过程的自动化。它不仅要保证程序的正确执行,而且要能够处理异常事件。控制器一般包括程序计数器(PC)、指令寄存器(IR)、指令译码器(ID)、时序控制器、总线控制器、中断控制器等几个部分组成。

-

程序计数器(PC)

程序计数器(Program Counter,PC)用来指出下一条指令在主存储器中的地址,当执行一条指令时,处理器首先需要从PC中取出指令在内存中的地址,通过地址总线寻址获取。当执行指令时,CPU能自动递增PC的内容,若为单字长指令,则(PC)+1,若为双字长指令,则(PC)+2。

-

指令寄存器(IR)

指令寄存器(Instruction Register,IR)用来保存当前正在执行的一条指令。

-

指令译码器(ID)

指令译码器(Instruction Decoder,ID)就是对指令寄存器的操作码部分进行译码,以产生指令所要求操作的控制电位,并将其送到微操作控制线路上,在时序部件定时信号的作用下,产生具体的操作控制信号。

-

指令控制器

主要完成取指令、分析指令和执行指令的操作。

-

时序控制器

时序控制器,主要是为每条指令按时间顺序提供应有的控制信号。

时序控制器包括时钟发生器和倍频定义单元。其中时钟发生器由石英晶体振荡器发出稳定的脉冲信号,即CPU的主频;而倍频定义单元则定义CPU主频是存储器频率(或总线频率)的几倍。早期,CPU同内存速度差异不大,所以CPU周期通常和存储器存取周期相同。后来,随着CPU的发展,速度远高于存储器,于是常将CPU周期定义为存储器存取周期的几分之一。

-

总线控制器

总线控制器就是管理总线的使用,包括总线上设备的管理和设备使用总线的过程管理。就CPU而言一般分为内部总线和CPU对外联系的外部总线。外部总线又叫系统总线,包括地址总线、数据总线、控制总线等。

-

中断控制器

计算机由于异常事件,或随机发生需立即外理事件,引起CPU暂时停止当前执行,转向另一服务程序以外处理当前事件,处理完成后返回原始程序的过程。

注:机器内部产生的中断,称为陷阱(内部中断),由外部设备引起的中断叫外部中断。

3.1.6、CPU的组成-寄存器

除了前面介绍的累加寄存器(ACC)、状态寄存器(PSW)、程序计数器(PC)、指令寄存器(IR),还有地址寄存器(AR)、数据寄存器(DR)。

-

地址寄存器(AR)

地址寄存器(Address Register,AR)用来保存CPU当前所访问的主存单元的地址。

由于在主存和CPU之间存在操作速度上的差异,所以必须使用地址寄存器来暂时保存主存的地址信息,直到主存的存取操作完成为止。

-

数据寄存器(DR)

数据寄存器(Data Register,DR)又称数据缓冲寄存器,用来暂时存放由主存储器读出的一条指令或一个数据字;反之,当向主存存入一条指令或一个数据字时,也将它们暂时存放在数据寄存器中。

其主要功能是作为CPU和主存、外设之间信息传输的中转站,用以弥补CPU和主存、外设之间操作速度上的差异。

注:需要了解CPU的整体运行过程,还有很多需要学习的,比如指令的构成(CISC和RISC指令系统)、指令以及数据的寻址方式、指令的周期、指令流水线、汇编语言等知识。

3.1.7、CPU的组成-总线

总线实际上是一组导线,是连接各个部件的信息传输线,用于作为电脑各组成部分信息传输共同使用的通路。

3.1.7.1、总线的分类

总线按其位置及功能可分为:

1)片内总线

它是位于芯片内部各单元电路之间的总线,作为这些单元电路之间的信息通道。如CPU内部ALU、寄存器组、控制器等部件之间的总线。

常见的片内总线有:AMBA总线-(Advanced Microcontroller Bus Architecture-高级微控制器总线架构)、IBM公司的CoreConnect总线等。

2)系统总线

又叫板级总线,指CPU、主存、I/O设备(通过I/O接口)各部件之间的信息传输线。我们常说的计算机总线就是指系统总线,系统总线是多处理器系统及高性能超级计算机系统中连接各插件板的信息通道,用来支持多个CPU并行处理。系统总线按功能可分为的:数据总线、地址总线、控制总线。

数据总线:用来传输数据信息;

地址总线:用于传输CPU发出的地址信息;

控制总线:传输控制信号、时序信号和状态信息等。

3)局部总线

局部总线是指在印制电路板上连接主板各个主要模块的公共通路。计算机系统主板上都有并排的多个插槽,这就是局部总线扩展槽。

目前已实施的局部总线可分为专用局部总线,VESA局部总线和PCI局部总线。

4)外部总线

又称为通信总线,用于计算机系统与系统;计算机系统与外部设备,例如打印机,磁盘设备;计算机系统与仪器仪表之间的通信。

常见的有USB(Universal Serial Bus-通用串行总线),SATA(Serial Advanced Technology Attachment-串行高级技术附件),SPI(Serial Peripheral Interface-串行外设接口),I2C(Inter-Integrated Circuit-两线式串行总线),UART(Universal Asynchronous Receiver/Transmitter-通用异步收发传输器)。

3.1.7.2、总线的性能指标

在了解总线的性能指标前,我们先了解一下什么叫时钟频率、时钟周期、机器周期和指令周期。

-

时钟频率

当代计算机中通常使用石英晶体振荡器(简称晶振,通常由主板来决定),将我们的交流电转换为精准、稳定的时钟信号,而我们的时钟频率就是晶振一秒钟震荡的次数,通常以MHz或者GHz为单位。

-

时钟周期

时钟周期为主频的倒数,有时也称之为节拍(pulse),即一个脉冲表示一个时钟周期。它是计算机中最基本的、最小的时间单位,在一个时钟周期内计算机仅能完成一个“微操作”或若干相容的微操作。

比如:1GHz的时钟周期f=1/1GHz=1ns,则睿频3.2GHz,则时钟周期为0.3125ns。

-

机器周期

在计算机中,为了便于管理,常把一条指令的执行过程划分为若干个阶段(如取指、译码、执行等),每一阶段完成一个基本操作。完成一个基本操作所需要的时间称为机器周期。一般情况下,一个机器周期由若干个时钟周期组成(机器周期是人为规定的,实际上是对一条指令执行过程阶段的划分)。

-

指令周期

执行一条指令所需的全部时间。

1)总线的传输周期

一次总线操作所需的时间,而这个时间可能是N个时钟周期。

2)总线的工作频率

总线的工作频率为总线周期的倒数。即总线的工作频率=时钟频率/N。

3)总线宽度

总线宽度,又叫总线的位宽,它是总线上同时能够传输的数据位数,即所谓的8位,16位,32位或64位等数据信号个数。

4)总线带宽

总线带宽是指总线的数据传输率,即单位时间内总线上可传输数据的位数,通常用每秒传送信息的字节数来衡量,单位可用(B/s)表示。总线带宽=总线工作频率×(总线宽度/8) 。

注:之所以除8,是因为带宽的单位用了(B/s)表示,“B”代表Byte-字节,1Byte=8bit位。

例如:假设某系统总线在一个总线周期中并行传输4字节信息,一个总线周期占用2个时钟周期,总线时钟频率为20MHz,则总线带宽是?

总线的传输周期=

总线带宽=总线工作频率×(总线宽度/8)=![]()

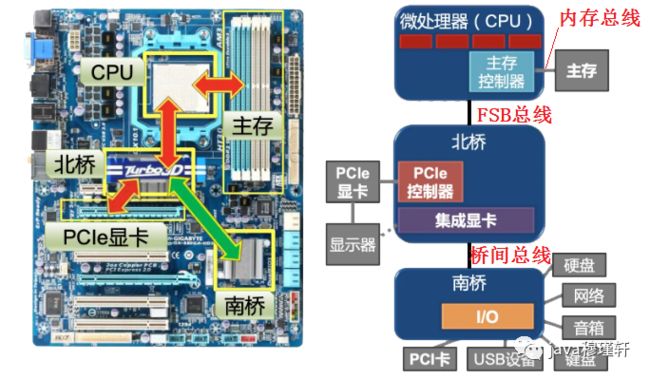

3.3、主板

3.3.1、什么是主板

主板是计算机最基本的同时也是最重要的部件之一。主板一般为矩形PCB印刷电路板,上面安装了组成计算机的主要电路系统,一般有BIOS芯片、I/O控制芯片、(键盘、COM、USB、MIDI、IDE、SATA等)接口、指示灯插接件、扩充插槽(内存插槽、PCI插槽、AGP插槽)等元件,主板的质量,决定了硬件系统的稳定性。

主板的核心是主板芯片组,它决定了主板的规格、性能和大致功能。

英特尔芯片组:H系列(低端入门级主板)、B系列(中端)、Z系列(高端);

AMD芯片组:A系列(低端)、B系列(中端)、X系列(高端)、TRX40(顶级);

3.3.2、芯片组结构简介-芯片组的起源

前面我们了解了CPU的发展史,在早期的4004处理器时代,处理器的功能比较单一,主要为了扩充处理器的基本计算功能;

1972年,Intel公司又推出了8008微处理器,英特尔在这款微处理器上配备了非常丰富的芯片,包括8228/8238系统控制器、8257可编程DMA控制器、8259中断控制器等一系列芯片组,还首次采用了处理器的指令技术;

1978年,英特尔推出了首款16位微处理器----8086,这款处理器是x86架构的鼻祖;后来,在80186处理器中,英特尔将DMA控制器等集成在了处理器内部;

1982年,发布了80286处理器,它的地址总线扩展到了24位;

1985年,Intel发布第一款32位X86处理器80386,其中最关键的特性就是采用了32位地址总线最大支持4GB内存;

1989年,Intel发布了80486处理器,芯片组与处理器一同在硬件设计逻辑上发生了非常大的变化;80486上第一次出现了一级缓存,Intel还整合了FPU(浮点运算单元);

随着486时代的开启,Intel开始进驻芯片组领域后,发布了Intel的历史上第一款芯片组,即Intel 420系列,它的首款产品叫做420TX,也是英特尔提供的首款支持PCI技术的芯片组,与处理器相连的总线为FSB(前端总线),频率为33MHz。支持FPM(Fast Page Mode,快页模式)内存,最大支持容量为128MB。与其搭配的南桥芯片为SIO(Super I/O),为主板提供更多的端口,这个时候还没有正式形成完整的“南北桥”结构。直到1993年,英特尔Pentium的横空出世,让英特尔意识到了,尽管处理器的性能非常强,但没有好的芯片组一样不行,也正是因为这样,也催生出了一代传奇般的芯片组:430系列芯片组。

在430系列芯片组中,首当其冲的就是桥芯片变成了两颗,分别为82349HX北桥和82371SB南桥。至此,芯片组算是正式有了南北桥这一概念。北桥主要负责主存、CPU、显卡之间的高速数据传输;而南桥则负责磁盘、USB、PCI等低速设备之间的数据传输。

3.3.3、芯片组结构简介-南北桥架构的演进

1997年,Intel发布了Pentium II(奔腾II),并为其配备了Intel 440系列芯片组,南北桥芯片要规范很多。

1999年,在Pentium III的时代,英特尔也正式发布了Intel 810芯片组,首次将Intel i752集成显卡装进了北桥内,同时也在南桥内首次集成了网卡和AC97声卡模块。

2000年,Pentium 4南桥芯片升级到了ICH4,北桥的内存控制器也支持DDR内存;在Pentium 4后期ICH6系列南桥芯片支持SATA技术;

2006年,英特尔推出了Core 2系列处理器后,英特尔正式抛弃了DDR内存,使其只支持DDR2内存,此时英特尔处理器的内存控制器依旧在北桥芯片中;这也是这个时期开始流行的显卡插槽标准,可以让显卡拥有更快的数据传输速度;

2008年,英特尔推出了X48芯片组,前端总线正式支持1600MT/s的速率,而内存支持方面也能到DDR3 1600,南桥方面这一代的芯片组再次升级到ICH10,支持6个SATA 3Gb/s接口及12个USB 2.0接口,这也可以看做是ICH系列南桥芯片的最终版本;

2009年,酷睿i系列处理器问世,北桥也随之被整合进CPU内,原来南桥也改名为PCH(平台控制器)。

3.4、存储器

3.4.1、什么是存储器

存储器是用来存储计算机信息的。

存储器按照工作方式来分:可以分为只读存储器(ROM)和随机存储器(RAM)。

存储器按照作用来分:可以分为内存储器和外存储器;

3.4.2、只读存储器ROM-简介

早期的ROM是一种只能读出事先所存数据的固态半导体存储器,因为技术不成熟所以无法擦写,出厂后就只能读数据,所以叫只读存储器。大部分只读存储器用金属—氧化物—半导体MOS(浮栅场)效应管制成的,即使在断电的情况下,也能长期的保留电子,理论上可以长达十年或者更久。常用于电脑中的开机启动(打开计算机时,CPU得到电能并开始准备执行指令,可是由于刚刚开机, RAM中还是空的,并没有那些需要执行的指令,所以就需要ROM中保存一个称之为BIOS小型指令集合,它告诉操作系统如何访问磁盘驱动器)。

早期,我们主要的存储介质都是磁性存储,也就是磁盘,分为软盘、光盘(以激光照射光盘上的铝膜刻蚀)和(机械)硬盘。它们都是以一种相异的状态来存储信息的,比如:硬盘的有无磁场,光盘的有无刻蚀标记来记录0和1的。

软盘(Floppy Disk):是个人计算机(PC)中最早使用的移动介质,软盘的读写是通过软盘驱动器完成的,它曾经盛极一时,如今还能在某东上搜到它,一般3.5寸的软驱能够存储1.44MB的内容,更早的还是5.25寸的,但如今我们并不常用。这也是为什么我们现在看到的操作系统都是将C盘作为硬盘分区的开始。

光盘(Optical disc):于1965年由美国发明家詹姆斯·拉塞尔发明的,可以存放各种文字、声音、图形、图像和动画等多媒体数字信息。分不可擦写光盘,如CD-ROM、DVD-ROM等;和可擦写光盘,如CD-RW、DVD-RAM等。1片12cm的光盘大约能存放680MB的资料。

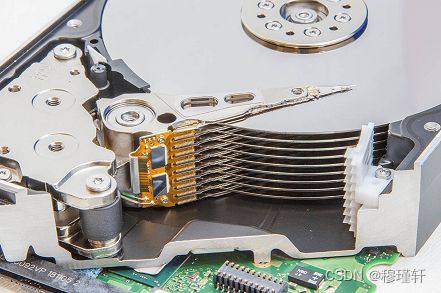

(机械)硬盘(Hard Disk Drive,简称HDD):全名温彻斯特式硬盘,由一个或者多个铝制或者玻璃制的碟片组成,这些碟片外覆盖有铁磁性材料。

早期的ROM,按照写入方式的不同,主要有:

a)掩模式ROM:算是早期的只读存储器,在芯片的生产过程中直接写入的,后续无法修改;

b)PROM(一次可编程ROM):有且仅有一次写入机会,一旦写入后无法修改;

后来随着技术的发展,在ROM的基础上出现了新的半导体存储介质,如:

c)EPROM(可擦除可编程ROM):既可以读出,也可以写入。其擦除方式有UVEPROM(紫外线擦除)和E2PROM(电气式来进行擦除);

d)闪速存储器(Flash Memory):一种快擦写型存储器。目前,大多数微型计算机的主板采用闪速存储器来存储BIOS程序。我们常见的固态硬盘(SSD)、SD卡、U盘等。

EPROM和闪存都是可以擦除的,这就不符合ROM的命名,但是由于是在ROM的技术上衍变出来的,所以延用了一部分原来的叫法。

3.4.3、机械硬盘和固态硬盘的区别

机械硬盘并不是闪存,它是采用磁性碟片来存储数据的。就像我们在电视剧里看到的老式的留声机上使用的唱片,只不过留声机只有一个磁头,而硬盘是上下双磁头,盘片在两个磁头中间高速旋转。而固态硬盘是利用闪存颗粒进行数据存储的。

-

机械硬盘

硬盘早期由IBM开发,1980年,两位IBM前员工创立公司,并开发出5.25英寸规格的5MB硬盘,这个公司就是希捷(Seagate)。

机械硬盘主要由磁盘盘片、磁头、主轴与传动轴等组成,数据就存放在磁盘盘片中。

磁盘面(Side):磁盘是由一叠磁盘片叠加组合构成,每个磁盘片由两个盘面,上下盘面都会有一个磁头负责读写;

磁道(Track):每个盘面会围绕圆心划分出多个同心圆圈,这些同心圆轨迹叫做磁道;磁道从外向内从0开始顺序编号,硬盘的每一个盘面有300~1 024个磁道,磁道是“看”不见的,只是盘面上以特殊形式磁化了的一些磁化区,在磁盘格式化时就已规划完毕。

柱面(Cylinders):所有盘片上的同一位置的磁道组成的立体圆柱叫做一个柱面,因此柱面数与磁道数是相等的。

扇区(Sector):在磁盘上每个同心圆是磁道,将每个磁道等分为若干弧段,每个弧段就是一个扇区。每个扇区的大小是固定的,为 512Byte。扇区也是磁盘的最小存储单位。

簇(Cluster):将物理相邻的若干个扇区称为了一个簇。操作系统读写磁盘的基本单位是扇区,而文件系统的基本单位是簇。簇一般有这几类大小 4K,8K,16K,32K,64K等。簇越大存储性能越好,但空间浪费严重。NTFS格式的文件系统簇的大小为4K。

例如:如下文件,实际大小为8.75KB,占用空间12.0KB,也就是三个簇。

磁盘容量的计算公式:容量=盘面数×扇区(柱面)数×扇区的字节数(512字节);

Disk /dev/sda: 299.0 GB, 298999349248 bytes

255 heads, 63 sectors/track, 36351 cylinders

Units = cylinders of 16065 * 512 = 8225280 bytes

注:255 heads(磁头)就有255个盘面

容量=255*36351*63*512=36351*8225280=298999349248,即299GB

机械硬盘通过接口与计算机主板进行连接,常见的机械硬盘接口有:

1)IDE接口(Integrated Drive Electronics,电子集成驱动器)

IDE 硬盘接口也称作 "ATA硬盘" 或 "PATA硬盘",是早期机械硬盘的主要接口,ATA本身支持串行和并行。最快并行ATA/133所能达到的理论速度133MB/s。不过现在市场上几乎没有这种接口的硬盘了,速度慢且不支持热插拔。

2)SATA接口(Serial ATA,串行ATA)

SATA速度比IDE接口更快,SATA不依赖与系统总线的带宽,而是内置时钟频率,支持热插拔。SATA3.0接口理论传输带宽6Gbps。目前,市场上大部分的机械硬盘接口都是SATA。

3)SCSI 接口(Small Computer System Interface,小型计算机系统接口)

SCSI广泛应用在服务器上,具有应用范围广、多任务、带宽大、CPU 占用率低及热插拔等优点,理论传输速度达到 320MB/s。

4)SAS接口(Serial Attached SCSI,串行SCSI)

SAS是新一代的SCSI技术,和现在流行的Serial ATA(SATA)硬盘相同,都是采用串行技术以获得更高的传输速度。

-

固态硬盘

固态硬盘(Solid State Disk)是用固态电子存储芯片阵列而制成的硬盘,固态硬盘的存储介质分为两种,一种是采用闪存(FLASH芯片)作为存储介质,另外一种是采用DRAM作为存储介质。目前使用较多的主要是采用闪存作为存储介质的固态硬盘。

普通SATA3.0固态硬盘速度约为500MB/S,而现阶段的机械硬盘的读取性能大多徘徊在100MB/S-200MB/S之间,而采用NVMe协议的M.2固态硬盘,最大读取性能则能够达到3000MB/S以上。

注:U盘,全称USB闪存盘,英文名“USB flash disk”。

U盘的称呼最早来源于朗科科技生产的一种新型存储设备,名曰“优盘”,使用USB接口进行连接。而之后生产的类似技术的设备由于朗科已进行专利注册,而不能再称之为“优盘”,而改称谐音的“U盘”。

那有人会有疑问,我们的平时用的U盘怎么感觉比机械硬盘还慢?U盘虽然用的闪存颗粒,但往往仅有两条闪存通道,U盘接口在数据吞吐量方面还是有差距的。

3.4.4、随机存储器RAM-简介

随机存储器RAM:是指随机存取存储器(random access memory,RAM),它与CPU直接交换数据的内部存储器,它可以随时读写,而且速度很快,通常作为操作系统或其他正在运行中的程序的短时间临时数据存储媒介。计算机首先从硬盘中将用户请求的程序或文档加载到内存,然后从内存中访问信息。随机存储器,是根据地址访问数据的,而不是顺序访问数据,主要是解决CPU和硬盘速度不匹配的问题。

随机存储器按制造工艺可以分为:双极型RAM和MOS RAM。

注:在逻辑电路中会接触到MOS管,MOS管相比三极管在低功率器件上更为实用。三极管用电流控制,耐高压大电流,而MOS管属于电压控制,功耗小。双极型RAM常见电路:TTL逻辑、ECL逻辑、I2L逻辑。

-

静态RAM(SRAM)

SRAM:静态RAM用由6个MOS管构成的触发器作为基本电路,集成度适中,功耗适中,速度较快,不需要刷新电路,只有断电信息才会丢失;

-

动态RAM(DRAM)

DRAM:动态RAM由MOS管栅极电容是否充有电荷来存储信息,基本单元电路一般由四管、三管和单管组成,以三管和单管较为常用。但由于这种电路存在漏电流,使栅极电容上的电荷经过一定的时间就会泄放,所以需要刷新电路(每隔1ms-3ms定时充电),但其集成度高,功耗低,成本比 SRAM低。通常用于制造内存条中的存储芯片。

DRAM主要有以下几种类型:

1)同步DRAM(SDRAM):DRAM的频率与CPU总线的频率同步,这大幅提升了数据的传输效率,所以称之为同步DRAM。

SDRAM内存有以下几种:PC66/100/133150/166,核心频率(或等效频率)分别为66MHz,100Mz,133MHz,150MHz,166MHz。

单根SDRAM内存数据传输带宽最高为 166MHz × 64bit ÷ 8 = 1.3GB/s。

2)Rambus DRAM(RDRAM):在狭窄的CPU内存总线上使用各种加速机制提供非常高的数据传输速率。RDRAM运行于串行电路上,意味着所有内存插槽都必须插满电路才能闭合,才可以访问内存。

3)双倍数据速率SDRAM(DDR SDRAM):SDRAM是在每个系统时钟的上升沿执行读/写功能的,而双倍速率同步动态随机存储器(Double data Rate SDRAM,简称DDR内存)则是在每个系统时钟的上升和下降沿都执行读/写功能,从而使内存性能有效地翻了一番,并大幅提高了整体性能。

谈及内存技术,首先就会提到DDR,它是广泛的应用于台式机、笔记本、服务器等系统中的一种主流内存技术。目前主流的DDR内存为:DDR3和DDR4。

4)高速缓存DRAM(CDRAM):一种特殊的DRAM存储器,带有片上高速缓存存储器(SRAM)和DRAM的高速缓冲区,也就是我们常说的Cache DRAM 。当CPU向内存中写入或读出数据时,这个数据也被存储进高速缓冲存储器中。当CPU再次需要这些数据时,CPU就从高速缓冲存储器读取数据,而不是访问较慢的内存。

Cache DRAM:一级缓存(L1 Cache)、二级缓存(L2 Cache)、三级缓存(L3 Cache)。

高速缓冲存储器(Cache):是数据交换的缓冲区,当某一硬件要读取数据时,会首先从缓存中查找需要的数据,如果找到了则直接执行,找不到的话则从内存中找。缓存的运行速度比内存快得多,主要是解决CPU与主存之间速度不匹配的问题。

高速缓冲存储器目前分为:L1缓存、L2缓存、L3缓存,每层速度按数量级递减、容量也越来越大。

每核心都有一个自己的L1缓存,L1缓存分两种:L1指令缓存(L1-icache)和L1数据缓存(L1-dcache)。L1指令缓存用来存放已解码指令,L1数据缓存用来放访问非常频繁的数据;

L2缓存用来存放近期使用过的内存数据。更严格地说,存放的是很可能将来会被CPU使用的数据;

多数多核CPU的各核都各自拥有一个L2缓存,但也有多核共享L2缓存的设计。无论如何,L1是各核私有的(但对某核内的多线程是共享的)。

3.4.5、DDR内存的发展历程

1961年,IBM在纽约州成立了以半导体为方向的托马斯·沃森研究中心,仙童当时是IBM的半导体器件供应商,仙童公司的戈登·摩尔预言:集成电路上可容纳的晶体管数量,约每隔18个月便会增加一倍,性能也将提升一倍。这就是著名的摩尔定律;

1966年,IBM托马斯·沃森研究中心,时年34岁的罗伯特·登纳德博士,提出了用金属氧化物半导体(MOS)晶体管,来制作存储器芯片的设想。原理是利用电容是否存储电荷来存储信息,每1bit都只需要一个晶体管和一个电容,并且这种做法一直沿用至今;

随着德州仪器、摩托罗拉等半导体公司的迅速崛起,由罗伯特·诺伊斯在1957年创办仙童半导体公司,因各种原因,其地位逐减被德州仪器所取代;

直到1968年8月,仙童罗伯特·诺伊斯拉着研发部门负责人戈登·摩尔辞职,并成立了新公司,起初把公司取名“摩尔-诺伊斯电子公司”,但是觉得别扭,就把名字改成了英特尔(Intel)。

1969年4月,英特尔公司就推出了64bit容量的静态随机存储器(SRAM)芯片C3101,只能存储8个英文字母。

不久,仙童公司的董事之一杰瑞·桑德斯也离开了公司,与另外7个人一起创立了AMD公司(Advanced Micro Devices,超微半导体)。而德州仪器半导体中心的首席工程师L.J.Sevin(MOS场效应管专家),拉着一帮同事辞职,成立了莫斯泰克(Mostek)公司。

1969年7月,英特尔公司推出了256bit容量的静态随机存储器芯片C1101,这是世界第一个大容量SRAM存储器。

1970年10月,推出了第一个动态随机存储器(DRAM)芯片C1103,容量只有1Kb;

1973年,莫斯泰克公司研制出16针脚的MK4096芯片,容量提高到4K,当时德州仪器、英特尔和摩托罗拉制造的内存是22针脚的;

虽然1974年,英特尔占据了全球82.9%的DRAM市场份额,但是很快被莫斯泰克公司超越,而英特尔此时将精力放在开发8080处理器上,在微型计算机市场取得巨大成功;

1978年四个莫斯泰克的离职员工在一间昏暗的地下室里创立了美国美光;

1980年,由富士通、日立、三菱、日电、东芝共同组建的“VLSI”项目,取得突破性进展。采用紫外线、X射线、电子束的各型制版复印装置、干式蚀刻装置等实现了DRAM量产,由于日本廉价DRAM的大量倾销,美光被迫裁员,就连英特尔也陷入巨额亏损,被迫宣布退出DRAM市场;

1982年,日本成为全球最大的DRAM生产国;此刻美国的半导体市场被日本击溃。最终,美光还是将64KDRAM的技术授权给了韩国三星;而后德州仪器为降低制造成本,也与韩国现代签订OEM协议,由德州仪器提供64K DRAM的工艺流程;

1990年,三星建立了26个研发中心,两年后三星率先攻破技术壁垒,推出世界第一个64M DRAM产品;

1996年,三星又开发出世界第一个1GB DRAM居世界第一,而现代电子位居第三;

1999 年,排名第三的韩国现代半导体与LG合并;同年,英飞凌科技公司在德国慕尼黑正式成立,其前身是西门子集团的半导体部门;

2001年,现代集团完成拆分,将公司名改为海力士(Hynix Semiconductor Inc),同年美光完成收购德州仪器DRAM业务;此时韩国三星、美国美光、韩国海力士和德国英飞凌4家DRAM市场占用超80%;同年,韩国三星电子开发出了DDR2内存;

2004年,DDR2内存条才开始量产逐渐进入大家的视野;

2005年,韩国三星电子宣布已经开发出世界上第一条DDR3内存;

2006年,DDR3内存条开始发售;

2008年,英飞凌也因世界金融危机退出了DRAM市场;此时三星、美光、海力士三大供应商几乎包揽全球DRAM市场绝大部分份额;

2011年1月,韩国三星电子宣布完成DDR4 DRAM模块的制造和测试;

2012年,韩国第三大财阀SK集团宣布收购海力士21.05%的股份,并将海力士更名为SK海力士(SK Hynix);

2014年,DDR4才开始进入市场;

2017年,新成立氮化镓 (GaN) 和碳化硅 (SiC)小组委员会;

2020年7月,JEDEC协会正式公布了DDR5标准;同年10月,SK海力士宣布,正式发布全球第一款DDR5内存;

2021年,三星DRAM市场占有率43.6%、SK海力士市场占有率27.7%、美国美光市场占有率22.8,仅三家巨头就占据了全球DRAM市场96.1%的市场份额。

2022年,DDR5开始逐渐进入市场。

3.4.6、DDR系列内存简介

下图是我2012年上大学时买的笔记本内存条的参数,至今还是一个强劲的战斗机。

在了解DDR内存条前,我们先来了解几个相关的概念:

-

DDR的核心频率

DDR核心频率是内存Cell阵列(Memory Cell Array,即内部电容)的刷新频率,它是内存的真实运行频率。受物理材料的极限限制,核心频率一直在133-200MHz间徘徊。

-

DDR的工作频率

由于DDR内存可以在脉冲的上升和下降沿都传输数据,所以DDR的工作频率是核心频率的双倍。

核心频率即为内存Cell阵列(Memory Cell Array,即内部电容)的刷新频率,它是内存的真实运行频率;时钟频率即I/O Buffer(输入/输出缓冲)的传输频率;而有效数据传输频率就是指数据传送的频率(即等效频率)

-

DDR的等效频率

等效频率与标称频率是一个概念,由于预取技术的应用,且上升、下降沿都进行数据传输,等效到单沿传输的情况下,等效频率(标称频率)=核心频率 × 倍增系数。

我们平时看到的内存条命名都是以DDR的标称频率为基准的。

注:倍增系数将在后面解释。

-

内存时序

1)CL-内存列寻址脉冲反应时间(延迟时间);

2)tRCD-内存行地址传输到列地址的延迟时间;

3)tRP-内存行地址选通脉冲预充电需要的时间;

4)tRAS-内存行地址选通延迟;

比如:

我们来计算一下DDR1~4的CL延迟时间:

DDR-400 3-3-3-8:3*2/400=15 ns

DDR2-800 6-6-6-18:6*2/800=15 ns

DDR3-1333 9-9-9-24:9*2/1333=13.5 ns

DDR4-2133 15-15-15-35:15*2/2133=14 ns

注:乘2的原因是DDR内存一个时钟周期内传输两次数据,即可得出每次时钟周期的一个延迟时间。

寻址一行一列必有交点,能唯一的确定一个内存地址。一般同频率下,CL值越小内存条性能越好(越容易超频),不同频率下内存频率越高性能越好。

-

双通道

在介绍双通道前,我们先看下如何计算内存的带宽。内存带宽计算公式:

内存带宽 = 内存核心频率 × 倍增系数 × ( 内存总线位数 / 8 ) = 标称频率×位宽。

前面我们说到,DDR采用时钟脉冲上升、下降沿各传一次数据,这个技术叫预取(Prefech,每次传输2bit),使得1个时钟信号可以传输2倍SDRAM的数据,所以又称为双倍速率SDRAM,它的倍增系数就是2。而DDR2采用则在这个预期机制上再次翻倍,预取4bit,所以DDR2的倍增系数为2X2=4;DDR3作为DDR2的升级版,这次预取增至8bit,它的倍增系数是2X2X2=8。

根据内存带宽的公式,我们发现在标称频率一定的情况下,如果能提高位宽,也就是提升内存的数据传输能力。于是Intel又发明了双通道来提升位宽。

普通的单通道内存系统具有一个内存控制器,而内存双通道就是在芯片中设计两个内存控制器(北桥的消失,Intel把内存控制器-MCH集成到了CPU中),这两个内存控制器可相互独立工作,每个控制器控制一个内存通道,两个内存通道CPU可分别寻址、读取数据,在双通道模式下具有128bit的内存位宽,理论上把内存带宽提高一倍。

1)DDR内存

JEDEC(固态技术协会是微电子产业的领导标准机构)制定的DDR标准

| 规格 | 针脚数(单面) | 电压 | 核心频率 | I/O频率 | 等效频率 | Prefech | 带宽 |

|---|---|---|---|---|---|---|---|

| SDR-133 | 168(84) | 3.3V | 133 MHz | 133 MHz | 133 MHz | 1 bit | 1.0 GB/S |

| DDR-200 | 184(92) | 2.5V | 100 MHz | 100 MHz | 200 MHz | 2 bit | 1.6 GB/S |

| DDR-266 | 184(92) | 2.5V | 133 MHz | 133 MHz | 266 MHz | 2 bit | 2.1 GB/s |

| DDR-333 | 184(92) | 2.5V | 166 MHz | 166 MHz | 333 MHz | 2 bit | 2.6 GB/s |

| DDR-400 | 184(92) | 2.5V | 200 MHz | 200 MHz | 400 MHz | 2 bit | 3.2 GB/s |

笔记本的针脚数为180。事实上厂商增强的一代DDR还有DDR-500,DDR-600,DDR-700,其等效频率分别为500 MHz、600 MHz、700 MHz。

单根DDR-500内存数据传输带宽最高为500 MHz×64 bit ÷ 8 = 4GB/s。

2)DDR2

JEDEC制定的DDR2标准

| 规格 | 针脚数(单面) | 电压 | 核心频率 | I/O频率 | 等效频率 | Prefech | 带宽 |

|---|---|---|---|---|---|---|---|

| DDR2-400 | 240(120) | 1.8V | 100 MHz | 200 MHz | 400 MHz | 4 bit | 3.2 GB/S |

| DDR2-533 | 240(120) | 1.8V | 133 MHz | 266 MHz | 533 MHz | 4 bit | 4.3 GB/s |

| DDR2-667 | 240(120) | 1.8V | 166 MHz | 333 MHz | 667 MHz | 4 bit | 5.3 GB/s |

| DDR2-800 | 240(120) | 1.8V | 200 MHz | 400 MHz | 800 MHz | 4 bit | 6.4 GB/s |

笔记本的针脚数为200。同样厂商增强的DDR2标准,还有DDR2-1066,其等效频率为1066 MHz。

单根DDR2-1066内存数据传输带宽最高为1066 MHz×64 bit ÷ 8 = 8.53GB/s。

3)DDR3

JEDEC制定的DDR3标准

| 规格 | 针脚数(单面) | 电压 | 核心频率 | I/O频率 | 等效频率 | Prefech | 带宽 |

|---|---|---|---|---|---|---|---|

| DDR3-800 | 240(120) | 1.5V | 100 MHz | 400 MHz | 800 MHz | 8 bit | 6.4 GB/S |

| DDR3-1066 | 240(120) | 1.5V | 133 MHz | 533 MHz | 1066 MHz | 8 bit | 8.5 GB/s |

| DDR3-1333 | 240(120) | 1.5V | 166 MHz | 667 MHz | 1333 MHz | 8 bit | 10.6 GB/s |

| DDR3-1600 | 240(120) | 1.5V | 200 MHz | 800 MHz | 1600 MHz | 8 bit | 12.8 GB/s |

| DDR3-1866 | 240(120) | 1.65V | 233 MHz | 933 MHz | 1866 MHz | 8 bit | 14.9 GB/s |

| DDR3-2133 | 240(120) | 1.65V | 266 MHz | 1066 MHz | 2133 MHz | 8 bit | 17.0 GB/s |

笔记本的针脚数为204。DDR3-1866和DDR3-2133是在后期才推出的,甚至还出现了DDR3-2400;同时也发布了低压版的DDR3,电压为1.35V。

DDR3的内存架构:

由于大多数的内存颗粒的位宽是8bit的,所以经常使用8个chip组成一个rank。

4)DDR4

JEDEC制定的DDR4标准

| 规格 | 针脚数(单面) | 电压 | 核心频率 | I/O频率 | 等效频率 | Prefech | 带宽 |

|---|---|---|---|---|---|---|---|

| DDR4-1600 | 288(144) | 1.2V | 100 MHz | 800 MHz | 1600 MHz | 8 bit | 12.8 GB/S |

| DDR4-1866 | 288(144) | 1.2V | 133 MHz | 933 MHz | 1866 MHz | 8 bit | 14.9 GB/s |

| DDR4-2133 | 288(144) | 1.2V | 166 MHz | 1066 MHz | 2133 MHz | 8 bit | 17.2 GB/s |

| DDR4-2400 | 288(144) | 1.2V | 200 MHz | 1200 MHz | 2400 MHz | 8 bit | 19.2 GB/s |

| DDR4-2666 | 288(144) | 1.2V | 233 MHz | 1333 MHz | 2666 MHz | 8 bit | 21.3 GB/s |

| DDR4-3200 | 288(144) | 1.35V | 266 MHz | 1600 MHz | 3200 MHz | 8 bit | 25.6 GB/s |

注:DDR4-1600和DDR4-1866一般应用在特殊领域,零售领域从2133起售。

我们发现DDR4的Prefech并没有变(由于预提取的提升已经十分困难),在原DDR3的内存架构上又新增了一个BANK GROUP的概念,将两个bank组装进一个BANK GROUP中,相当于提升了Prefech为16bit。

2)DDR5

JEDEC制定的DDR5标准预计最高达DDR5-6400,并且Prefech提升至16 bit。

4、需要了解的一些基础知识

4.1、关于CPU的知识拓展

4.1.1、CPU主流厂商品牌

目前CPU主流厂商有,英特尔和AMD。

-

英特尔的CPU

常见的系列有:赛扬、奔腾、酷睿、至强,定位从低到高。

其中赛扬、奔腾定位为家用低端办公平台,性能偏弱,常见的以G命名。

酷睿则定位为高性能的游戏平台,常见的以i开头,比如i5、i7、i9,一般命名规则为ix xxxx(F/K/X/XE/S),其中F代表无核显(可配独立显卡),K代表该处理器是不锁倍频,即可超频CPU(性能可以更强),X和XE即至尊级,S代表低功耗版。而目前绝大部分的笔记本都采用的是BGA封装的CPU,一般这种封装的需要专业的机器才能更换。所以,我们常见的笔记本的CPU通常有X(高性能处理器)、H(高电压且不可拆卸处理器)、HQ(带核显的,可媲美中端独立显卡)、M(标准电压处理器)、U(低电压处理器)、Y(超低电压处理器)等结尾。

而至强系列的定位为服务器平台。

-

AMD的CPU

常见的系列有:羿龙、速龙(K开头)、闪龙、推土机(FX)、锐龙(Ryzen)。当然还有一些中间系列,比如毒龙等。

我们比较常见的就是锐龙系列了。2017年发布,主要是为了取代推土机系列。锐龙以R开头,比如R5、R7、R9,一般命名规则为Rx xxxx(G/X),其中G代表核显系列、X代表自动超频系列。

4.1.2、什么是CPU主频、外频、倍频

-

主频

CPU主频,即CPU内核工作的时钟频率( CPU Clock Speed),CPU的时钟频率发生器也在主板上,它是利用电流刺激石英震荡来形成稳定的脉冲信号。CPU的主频和CPU的运行速度并不是一个线性的关系,但提高主频对于提高CPU运算速度至关重要。

主频率越高,表示处理速度越快。频率目前仅能用来比较同款 CPU 的速度。

最早的4004芯片他的核心频率740kHz,即1秒钟能脉冲74万次,2004年的奔腾4最高主频就达到了3.4GHz,之后的十多年里的主频变化也不是很大(主要还是受功耗及发热的影响),到2022年最新的十二代酷睿i9 12900HX,主频的范围为2.3GHz-5GHz,最高1秒钟能脉冲50亿次。

注:以前我们看CPU的主频可能会有一个范围2.3GHz-5GHz,表示处理器的主频为2.3GHz,最高可达5GHz,但是以前想要达到最高频率,需要人为的去设置,但是现在我们发现都开始展示睿频了,最高睿频5GHz,表示处理器时钟频率可以睿频至5GHz,不需要人为设置。

-

外频

外频即CPU外部的频率,是CPU与主板之间同步运行的速度,也是整个计算机系统的基准频率。(大多数的频率都是在外频的基础上,乘以一定的倍数来实现的)

可以理解为CPU的外频直接与内存相连通,实现两者间的同步运行状态,与外频有关的是内存和主板芯片集,外频可以超频但不稳定。

为什么会有外频的概念?

最具经典的80486(外频33MHz)处理器的出现,为芯片组的奠定了基础,Intel 420系列就有了芯片组的概念,而外频的概念就是建立在这个基础之上的,是指CPU到芯片组之间的总线速度,总线是多个部件间的公共连线,用于在各个部件之间传输信息,同时把CPU连接到北桥芯片的总线称之为FSB(Front Side Bus,前端总线),CPU就是通过北桥芯片和内存、显卡交换数据的。奔腾4之前,由于CPU与内存的速度相差不大,CPU的外频与主板间内存的速度相同,也就是说CPU的外频和前端总线的速度是相同的(频率相同有利于系统稳定)。

后来CPU的工作速率不断的提升,同时CPU的外频从原来的33MHz、66MHz也逐步提升,目前有100MHz、133MHz、166MHz、200MHz、300MHz等等。而内存方面由于电气结构的关系,跟不上CPU的速率,这严重影响了我们对速率追求的执念。数据带宽=(总线频率×数据位宽)÷8,前端总线频率越大,代表着CPU与北桥芯片之间的数据传输能力越大,如果没足够快的前端总线,再强的CPU也不能明显提高计算机整体速度。

intel为了提升内存的工作频率,可谓绞尽脑汁。为了缓解这种局面,奔腾4对整体的CPU和芯片组架构有了较大的改变,奔腾4采用了quad pumped(4倍并发)技术,这项技术使得系统总线一个时钟周期能传输4次数据,相当于用了4条原来的前端总线和内存交互。

对于133MHz的外频,此时前端总线的速度达到了133 x 4 = 533MHz。那时候还是2000年,Pentium 4南桥芯片升级到了ICH4,北桥的内存控制器也支持DDR内存,而在这个阶段的DDR内存还是一代的DDR(二代DDR在2004年才量产),DDR266无法达到前端总线的速率,于是有了双通道的概念,起初就在北桥芯片里设计了两个内存控制器(MCH),后来随着北桥的消失内存控制器(MCH)也集成到了CPU内部。

CPUZ的检测:

注:这里总线的速度就是指的外频。

-

倍频

全称是倍频系数,CPU的核心工作频率与外频之间存在的一个比值关系,这个比值就是倍频系数,简称倍频。

当外频不变时,提高倍频,CPU主频也就越高。原先并没有倍频概念,CPU的主频和系统总线的速度是一样的,但CPU的速度越来越快,倍频技术也就应运而生。它可使系统总线工作在相对较低的频率上,而CPU速度可以通过倍频来无限提升。一个CPU默认的倍频只有一个,主板必须能支持这个倍频。因此在选购主板和CPU时必须注意这点,如果两者不匹配,系统就无法工作。

CPU工作频率=倍频*外频。

4.1.3、什么是集显、独显

-

集显

集显分两种:

一种是在主板上集成的(在北桥芯片中或直接焊在主板上)。使用这种主板就可以不需要独立显卡就能满足普通的显示功能。

另一种集成在CPU中,Intel叫核芯显卡,AMD叫APU(Accelerated Processing Units,加速处理器)。依托CPU强大的运算能力和智能能效调节设计,在更低功耗下实现同样出色的图形处理性能和流畅的应用体验。

现在基本上集显都是核显,集成在主板上的已经比较少见了。

-

独显

独显即独立显卡,在主板上提供了一个额外的显卡接口,如果觉得集显无法满足自己的要求,可使用独显,它的性能更出色的。

-

集显和独显的区别

1)显存不同

独立显卡具备单独的显存,不占用系统内存,拥有单独的图形处理核心和独立的显存,能够满足复杂庞大的图形处理需求,有其是大型3D游戏。

核显是将图形核心整合在CPU中,可以独立加速或降频,并共享三级高速缓存,进一步加强了图形处理的效率。

2)功耗不同

独立显卡的高于核显。

低功耗、性价比是核显的最主要优势,高效的处理性能核和大幅度缩减的运算时间,进一步减少了核显的功耗。

4.1.4、超线程技术

我们在买电脑的时候,经常会看CPU的参数,对CPU的描述有这几种:“双核”、“双核四线程”、“四核”、“四核四线程”、“四核8线程”......

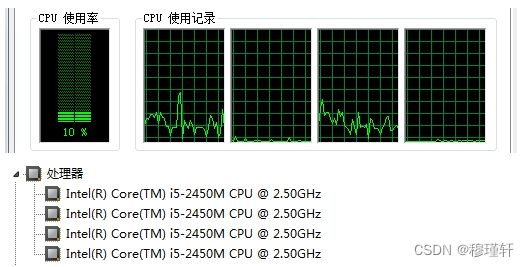

充满好奇心的猫,赶紧打开了任务管理器,准备一探究竟:

这是真4核还是4线程?吓得我赶紧用CPUZ检测了一下我的电脑:是一个双核四线程。

这就是Intel于2002年发布的一种技术,叫超线程(HT, Hyper-Threading)。

没有CPUZ的可以使用dos命令

Win+R,输入wmic

分别输入

cpu get Name CPU名称/CPU个数(物理硬件上的CPU的个数)

cpu get NumberOfCores CPU核心数(CPU核心单元组个数)

cpu get NumberOfLogicalProcessors 线程数(一个核心最少对应一个线程,但通过超线程技术,一个核心可以对应两个线程)

4.1.4.1、什么是进程、线程

-

进程

在操作系统没有引入进程之前,由于CPU一次只能执行一个程序,所以多个程序只能顺序执行,而CPU的速度很快,磁盘、网路等IO的速度很慢,造成CPU会有大量空闲的时间,此时CPU的利用率很低,为了解决CPU的利用率低的问题,操作系统引入了进程(20世纪60年代提出的)以及中断处理,实现了在同一时间段内,多个程序的并发执行,大大提高了CPU的利用率。

进程(Process):是操作系统进行资源分配的最小单位。一个进程是一个程序的一次执行过程,每启动一个进程,操作系统就会为它分配一块独立的内存空间,用于存储PCB、数据段、程序段等资源,即每个进程占据一块独立的内存空间。

-

线程

60年代在操作系统中能拥有资源和独立运行的基本单位是进程,然而随着计算机技术的发展,进程出现了很多弊端,一是由于进程是资源拥有者,创建、撤消与切换存在较大的时空开销,需要引入一种轻型进程,因此到了20世纪80年代中期,在操作系统领域,提出了比进程更小的能独立运行的基本单位——线程。

线程(Thread):轻量级进程,是操作系统进行调度的最小单位。一个线程是一个任务(一个程序段)的一次执行过程,线程不占有内存空间,它包括在进程的内存空间中。在同一个进程内,多个线程共享进程的资源,一个进程至少有一个线程。

4.1.4.2、超线程技术概述

我们追求速度(性能)的心从未停止,不榨干CPU的空闲时间誓不罢休。于是在2002年2月,超线程技术第一次在Xeon服务器处理中亮相,同年11月发布的桌面版Pentium 4处理器也集成了超线程技术。

超线程允许单个处理器在同一时刻并行地抓取和执行两个独立的代码流,也就是说用单个CPU模拟双CPU来平衡程序运行的性能,使得应用程序的多个线程,能同时再一个处理器上被执行。

4.2、计算机软件系统概述

计算机系统它具有层次性,从宏观层面来说分为硬件系统和软件系统。前面主要从宏观层面介绍了计算机硬件方面的一些知识,接下来我们主要从微观层面介绍软件方面的一些知识。

4.2.1、计算机系统层次概述

我们从下往上说,在硬件系统层面:

数字逻辑层:它是最底层的机器硬件,是由数字逻辑电路构成的一些电子元件;

微体系结构层:它是数字逻辑层的上级,它是一些微程序,它发出的微指令可以被机器硬件识别;

指令系统层:它是微体系结构的上级,也叫机器语言级,它是能被微程序解释的机器指令;

在软件系统层面:

操作系统层:它由操作系统程序实现,这些操作系统由机器指令和广义指令组成,这些广义指令是操作系统定义和解释的软件指令,它是衔接硬件和软件的载体。

汇编语言层:它给程序员提供一种符号形式的语言替代机器语言,以减少程序编写的复杂性;

高级语言层:它由各种高级语言组成,它简化了符号形式语言的复杂性,高级语言最终还是会编译成汇编语言程序。

4.2.2、计算机软件系统的发展

-

第一代软件(1946-1953)

电子管时代,第一代软件是用机器语言编写的,机器语言是内置在计算机电路中的指令,由0和1组成。最初的指令系统只有十几到几十条。

程序员们将用0, 1数字编成的程序代码打在纸带或卡片上,1打孔,0不打孔,再将程序通过纸带机或卡片机输入计算机,进行运算。这样的机器语言由纯粹的0和1构成,十分复杂,不方便阅读和修改,也容易产生错误。

-

第二代软件(1954-1964)

晶体管时代,当硬件变得更强大时,就需要更强大的软件工具更有效地使用计算机。汇编语言的出现解决了这个问题,汇编指令是机器指令便于记忆的书写格式,用助记符(Mnemonics)代替机器指令的操作码,用地址符号(Symbol)或标号(Label)代替指令或操作数的地址,但是程序员还是必须记住很多汇编指令。

注:汇编语言在今天的实际应用中,它通常被应用在底层。驱动程序、嵌入式操作系统和实时运行程序都需要汇编语言。

-

第三代软件(1965-1970)

集成电路的出现,使得处理器的运算速度得到了大幅度的提升,因此我们需要一个更有效的方式来控制计算机中的各个硬件来协调工作,于是引入了操作系统的概念。

-

第四代软件(1971-1989)

微处理器的出现,为了方便修改和维护程序,20世纪70年代出现了结构化程序设计技术,Pascal语言和Modula-2语言都是采用结构化程序设计规则制定的,Basic这种为第三代计算机设计的语言也被升级为具有结构化的版本,此外,还出现了灵活且功能强大的C语言。

-

第五代软件(1990-至今)

在计算机软件业具有主导地位的Microsoft公司的崛起、面向对象的程序设计方法的出现、以及万维网(World Wide Web)的普及,加速了现代信息化的飞速发展。

而我们要学的正是这些高级语言。