HDLBits练习——Count clock

Create a set of counters suitable for use as a 12-hour clock (with am/pm indicator). Your counters are clocked by a fast-running clk, with a pulse on ena whenever your clock should increment (i.e., once per second).

reset resets the clock to 12:00 AM. pm is 0 for AM and 1 for PM. hh, mm, and ss are two BCD (Binary-Coded Decimal) digits each for hours (01-12), minutes (00-59), and seconds (00-59). Reset has higher priority than enable, and can occur even when not enabled.

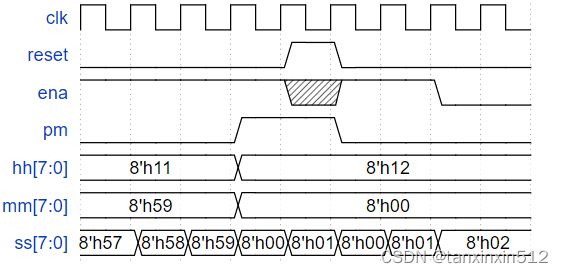

The following timing diagram shows the rollover behaviour from 11:59:59 AM to 12:00:00 PM and the synchronous reset and enable behaviour.

前言

三个输入,包括一个时钟clk,一个高电平有效的同步置位信号reset,一个使能信号ena;四个输出,包括一个判断信号pm,三个计时信号hh、mm和ss。

代码

module top_module(

input clk,

input reset,

input ena,

output pm,

output [7:0] hh,

output [7:0] mm,

output [7:0] ss);

wire ena_s,ena_m,ena_h;

assign {ena_s,ena_m,ena_h}={ena,ena&ss==8'h59,ena&ss==8'h59&mm==8'h59};

cout60 instance1(clk,reset,ena_s,ss);

cout60 instance2(clk,reset,ena_m,mm);

cout12 instance3(clk,reset,ena_h,hh);

always@(posedge clk)begin

if(reset) pm<=1'b0;

else if(ena&hh==8'h11&ss==8'h59&mm==8'h59) pm<=~pm;

else pm<=pm;

end

endmodule

module cout60(input clk,reset,ena,output [7:0]q);

reg [3:0] q2,q1;

assign q={q2,q1};

always@(posedge clk)begin

if(reset) begin

q1<=4'h0;

q2<=4'h0;

end

else if(ena)begin

q1<=(q1<4'h9)?(q1+1'b1):4'h0;

q2<=(q1<4'h9)?q2:(q2<4'h5)?(q2+1'b1):4'h0;

end

else {q2,q1}<={q2,q1};

end

endmodule

module cout12(input clk,reset,ena,output [7:0]q);

always@(posedge clk) begin

if(reset) q<=8'h12;

else if(ena) begin

if(q==8'h12) q<=8'h01;

else if (q[7:4]==4'h0&q[3:0]<4'h9) q<={4'h0,q[3:0]+1'b1};

else if (q==8'h09) q<=8'h10;

else if (q[7:4]==4'h1&q[3:0]<4'h2) q<={4'h1,q[3:0]+1'b1};

else q<=8'h12;

end

else q<=q;

end

endmodule

总结

对于12小时的钟表计时,需要构建两种计数器,一种是0→59的60制计数,即模块cout60,一种是1→12的12制计数,即模块cout12,两个模块的代码风格不一样是因为12进制的循坏节点较多不适宜复用判断语句;对于输出的判断信号pm,其只有三种状态,一是有效置时,pm等于初始值1’b0,二是在使能状态下,当计时为11:59:59时,pm状态发生翻转,三是不满足上述条件时,pm保持原值。