记:sx1278芯片

目录

lora数字接口

静态配置寄存器

状态寄存器

lora模式FIFO数据缓存

数字IO引脚映射

FIFO操作原理

lora调制解调器操作模式

LoRa调制解调器状态机序列

数据发送序列

数据接收序列

单一接收操作模式

连续接收操作模式

从FIFO数据缓存提取有效负载数据

基于前导码起始的数据包过滤

lora数字接口

lora调制解调器有三种数字接口,静态配置寄存器、状态寄存器和一个FIFO缓存。

静态配置寄存器

静态配置寄存器在任何设备模式下(包括睡眠模式)均可读,但仅在睡眠模式和待机模式下可写。

注意:lora模式下,自动顶级定序器(TLS模式)不可用。lora配置寄存器的内容在FSK/OOK模式下是保持的。

状态寄存器

状态寄存器在接收机运行过程中提供状态信息。

lora模式FIFO数据缓存

SX1276/77/78配备了256字节的RAM数据缓存(作为FIFO),该缓存仅能通过(lora模式,SPI接口)进行访问。

除睡眠模式外,其他模式下均可读。

数字IO引脚映射

SX1276/77/78的6个通用IO引脚在LoRa模式下均可用。它们的映射关系取决于RegDioMapping1和RegDioMapping2这两个寄存器的配置。

| DIOx映射 | DIO5 | DIO4 | DIO3 | DIO2 | DIO1 | DIO0 |

| 00 | ModeReady | CadDetected | CadDone | FhssChangeChannel | RxTimeout | RxDone |

| 01 | ClkOut | PllLock | ValidHeader | FhssChangeChannel | FhssChangeChannel | TxDone |

| 10 | ClkOut | PllLock | PayloadCrcError | FhssChangeChannel | CadDetected | CadDone |

| 11 | - | - | - | - | - | - |

FIFO操作原理

FIFO数据缓存拥有双端口配置,因此可以在缓存内同时存储将要发送和接收的信息。

RegFifoTxBaseAddr寄存器记录将要发送信息的起始位置,RegFifoRxBaseAddr寄存器记录接收操作中写入缓存的起始位置。

默认情况下,器件上电后,以保证一半的可用内存用于Rx(RegFifoRxBaseAddr寄存器被初始化至地址0x00),另一半的可用内存用于Tx(RegFifoTxBaseAddr寄存器被初始化至地址0x80)。

然而,鉴于FIFO数据缓存固有的毗连特性,Tx的Rx的基址可以在256字节的内存区内进行设置。每个指针均可在FIFO中任意独立设置。

为了充分利用FIFO数据缓存内存将要发送或接收数据的空间,可以将RegFifoTxBaseAddr寄存器或RegFifoRxBaseAddr寄存器设置为0x00,从而使整个FIFO数据缓存仅在发送或接收模式下使用。

器件被设置为睡眠模式时,FIFO数据缓存被清空。因此,在睡眠模式下无法访问FIFO数据缓存。

然而,当器件切换到lora的其他操作模式时,FIFO数据缓存中的数据则保持不变,因此接收的数据包在控制器经过最简单的数据处理后可以被重发出去。

当一组新数据被写入已被占用的缓存单元时,只是覆盖掉旧数据(不会自行清空,除非设置为睡眠模式)。

通过SPI接口读取或写入当前数据的FIFO数据缓存单元由RegFifoAddrPtr地址指针定义。因此在进行任何读取或写入操作前,必须先将该指针初始化为对应的基地址。

从FIFO数据缓存(RegFifo寄存器)读取数据或FIFO数据缓存写入数据后,RegFifoAddrPtr地址指针将自动增值。

在成功完成数据接收操作时,RegRxNbBytes寄存器会定义待写入数据的所占缓存单元的大小。

RegPayloadLength寄存器则显示待发送数据所占用的缓存单元大小。

RegFifoRxCurrentAddr寄存器显示最后接收的数据包在FIFO数据缓存中的存储位置。

因此通过将RegFifoAddrPtr地址指针指向RegFifoRxCurrentAddr寄存器,即可轻松读取该数据包。

在隐式报头模式下,RegRxNbBytes寄存器是无效的,因为此时有效负载字节数必须是已知的。而在显式报头模式下,接收缓存区的初始空间与所要接收的报头携带的数据包长度一致。

注意:即使CRC无效,所有接收到的数据也都会写入FIFO数据缓存,这样可以让用户按照自定义的方式对损坏的数据进行后续操作;另外,接收数据包时,如果数据包大小超过分配给Rx的缓存空间,它会覆盖掉缓存内储存的部分发送数据。

lora调制解调器操作模式

启动lora模式后(即设置RegOpMode寄存器的LongRangeMode位),就可以查看lora调制解调器的操作模式。

通过改变RegOpMode寄存器的值,可以从任意一种模式切换到另一种模式。

| 操作模式 | 描述 |

| 睡眠模式 | 低功耗模式。在这种模式下,仅SPI和配置寄存器可以访问,不能访问LoRa FIFO。 这是唯一允许FSK/OOK模式与LoRa模式切换的操作模式。 |

| 待机模式 | 晶体振荡器和LoRa基带模块被开启,而射频部分和PLL则被关闭 |

| FSTx模式 | 这是一种用于发射的频率合成模式。选定的发射PLL处于锁定状态,并在发送频率上保持活跃。射频部分被关闭。 |

| FSRx模式 | 这是一种用于发射的频率合成模式。选定的发射PLL处于锁定状态,并在接收频率上保持活跃。射频部分被关闭。 |

| Tx模式 | 这种模式被激活后,SX1276/77/78将打开发送所需的所有模块、打开功率放大器(PA)、发送数据包,并切换回待机模式。 |

| Rx连续模式 | 这种模式被激活后,SX1276/77/78将打开接收所需的所有模块、处理所有接收到的数据,直到客户请求改变操作模式 |

| Rx单一模式 | 这种模式被激活后,SX1276/77/78将打开接收所需的所有模块、在收到有效数据包前保持此状态、随后切换回待机模式 |

| CAD模式 | 在CAD模式下,设备将检测已知信道,以检测LoRa前导码信号 |

LoRa调制解调器状态机序列

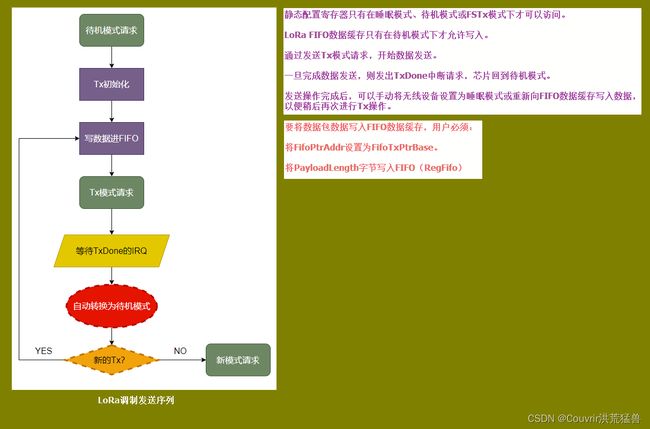

数据发送序列

在发送模式下,仅在需要发送数据包数据时才会启动射频模块、PLL模块及PA模块,这样可以优化功率消耗率。

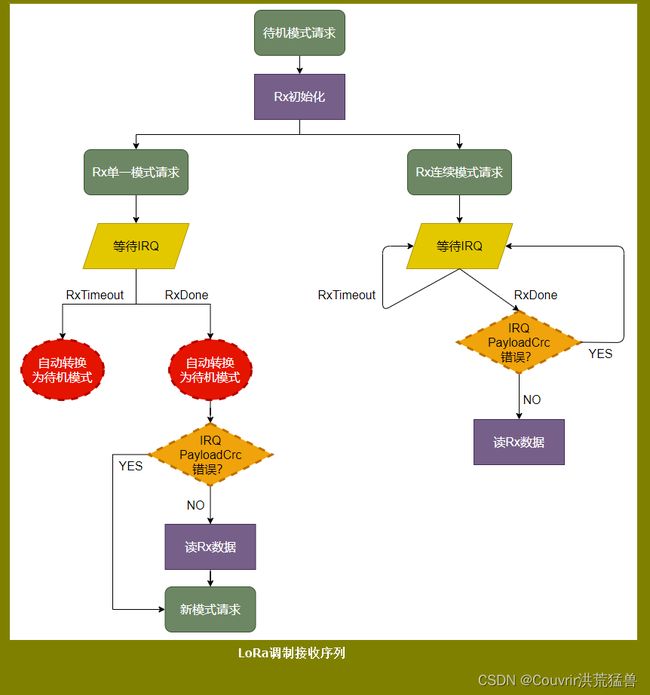

数据接收序列

单一接收操作模式

在这种模式下,调制解调器在给定的时间窗口内搜索前导码。如果在该时间窗口结束时还未找到前导码,则芯片会产生RxTimeout中断信号并切换回待机模式。

时间窗口长度由RegSymbTimeout寄存器定义,必须为4~1023个符号。调制解调器获取前导码锁的最短时间为4个符号,缺省值为5个符号。

在有效负载结束时,如果负载CRC无效,则会产生RxDone中断信号和PayloadCrcError中断信号。然而,即使CRC无效,仍然可以在FIFO数据缓存中写入数据,以便后续进行处理。RxDone中断产生后,芯片切换回待机模式。

当RxDone或RxTimeout中断信号产生时,调制解调器都会自动回到待机模式。因此,只有在数据包到达时间窗口为已知的情况下才会使用Rx单一接收模式。而在其他情况下,应使用Rx连续模式。

在Rx单一模式下,接收到数据包后,应立即关闭PLL和射频模块,以降低功耗。流程如下:

1. 将FifoAddrPtr设置为FifoRxBaseAddr。

2. 静态配置寄存器在睡眠模式、待机模式或FSRx模式下均可写入数据。

3. 通过选择Rx单一操作模式,可以启动单一数据包接收操作。

4. 接收机等待接收有效前导码。接收到有效前导码后,接收通路增益即刻被设定。随后将接收到由ValidHeader中断信号表示的有效显式报头后,开始数据包接收。数据包接收完毕后,产生RxDone中断信号。最后,芯片自动恢复到待机模式,以减少功耗。

5. 应检查接收机状态寄存器PayloadCrc,以保证数据包有效负载的完整性。

6. 如果接收到有效的数据包,则应该读取FIFO数据缓存中的数据。如果后续需要触发单一数据包接收过程,则应该重选Rx单一操作模式,以便再次启动接收程序(务必将SPI指针FifoAddrPtr重选调整到缓存的接收基地址FifoRxBaseAddr)。

连续接收操作模式

在连续接收模式下,调制解调器会持续扫描信道,以搜索前导码。每当检测到前导码时,调制解调器都会在收到数据包前对该前导码进行检测及跟踪,然后继续等待检测下一前导码。

如果前导码长度超过RegPreambleMsb和RegPreambleLsb寄存器设定的预计值(按照符号周期测量),则前导码会被丢弃,并重新开始前导码搜索。但在这种场景不会产生中断标志。

与单一Rx模式相反,在连续Rx模式下,当产生超时中断时,设备不会进入待机模式。这是,用户必须在设备继续等待有效前导码的同时直接清除中断信号。

注意:被解调字节是按照接收序列写入数据缓存区的。即新数据包的第一个字节会在上一个数据包的最后一个字节之后立即写入。在这种模式下,接收地址指针将不会重置。因此,关联微处理器MCU必须对地址指针进行处理,以保证FIFO数据缓存不会溢出。

在连续模式下,被接收数据包的处理序列如下:

1. 在睡眠或待机模式下,选择RXCONT模式。

2. 收到有效报头后,紧接着会产生RxDone中断。芯片一直处于RxCONT模式,等待下一个lora数据包。

3. 检查PayloadCrcError标志,以验证数据包完整性。

4. 如果数据包被正确接收,则可以读取FIFO数据缓存。

5. 接收过程(步骤2~4)可重复,或在需要的情况下可退出接收机操作模式。

在接收连续操作模式,仅可查看最后一个接收数据包对应的状态信息。即应在接收到下一个RxDone信号之前读取对应寄存器。

从FIFO数据缓存提取有效负载数据

为从FIFO数据缓存检索接收数据,用户必须保证状态寄存器RegIrqFlags的ValidHeader、PayloadCrcError、RxDone和RxTimeout等中断信号未意外生效,以确保数据包接收成功终止(即不应设置任何标志)。

如果发生错误,应跳过以下步骤,同时丢弃数据包。为从FIFO数据缓存检索到有效的接收数据,用户必须:

RegRxNbBytes:表示到现在为止已接收到的字节数。

RegFifoAddrPtr:精确标志了LoRa调制解调器接收数据写入位置的动态指针。

将RegFifoAddrPtr设置为RegFifoRxCurrentAddr:表示将FIFO指针指向FIFO数据缓存中最后接收的数据包的存储位置。可以通过RegRxNbBytes去读取RegFifo寄存器的数据,以提取数据包的有效负载数据。

或者,可以手动将RegFifoAddrPtr设置为RegFifoRxCurrentAddr减去RegRxNbBytes的值,使该指针从当前数据包开始,一直指向最后接收的数据包的存储位置。可以通过RegRxNbBytes去读取RegFifo寄存器的地址,以提取数据包的有效负载字节。

基于前导码起始的数据包过滤

数据包过滤的目的是确定数据包是否存在发往接收机的有效数据包。如果没有,则芯片将切换回睡眠模式,以便延长电池的使用寿命。

LoRa调制解调器会根据寻址自动过滤接收到的数据包。但SX1276/77/78却支持基于有效负载的前几个字节的内容对接收的数据包进行软件过滤。以下以4字节地址为例。地址长度可由设计人员确定。

软件数据包过滤的步骤如下:

每次接收到RxDone中断信号时,锁存start_address变量的RegFifoRxByteAddr[7:0]寄存器内容。SX1276/77/78的RegFifoRxByteAddr[7:0]寄存器实时显示由LoRa接收调制解调器写入数据缓存的最后一个字节的地址+1(或下一个字节将要写入的地址)。通过这种方式可以保证start_address变量总是包含下一个数据包的起始地址。

收到ValidHeader中断信号后,立即开始轮询RegFifoRxByteAddr[7:0]寄存器,直到该寄存器开始增值。该寄存器的增值速度取决于扩频因子、纠错码和调制带宽(隐式模式下仍然会产生该中断信号)。

只要RegFifoRxByteAddr[7:0]大于或等于起始地址+4,则前4个字节(地址)就会被存入FIFO数据缓存。可以通过读取和检测这些字节,来确定数据包是否发往该芯片,以及是否继续保持Rx模式以便接收剩下的数据包,或者在非Rx模式下,LoRa调制解调器是否恢复到睡眠模式等。