System Generator学习——使用 AXI 接口和 IP 集成器

文章目录

- 前言

- 一、目标

- 二、步骤

-

- 1、检查 AXI 接口

- 2、使用 System Generator IP 创建一个 Vivado 项目

- 3、创建 IP 集成设计(IPI)

- 4、实现设计

- 总结

前言

在本节中,将学习如何使用 System Generator 实现 AXI 接口。将以 IP 目录格式保存设计,并在 Vivado IP Integrator 环境中使用生成的 IP。然后,还将看到 IP Integrator 在使用 AXI 接口时如何通过提供连接辅助来提高我们的工作效率。

一、目标

完成本实验后,你将能够:

- 在你的设计中实现 AXI 接口

- 将你的设计作为 IP 添加到 Vivado IP 目录中

- 连接你的设计在 IP 集成器

二、步骤

这个练习有四个主要部分:

- 在第 1 步中,将回顾如何使用 System Generator 实现 AXI 接口

- 在第 2 步中,将为 System Generator IP 创建一个 Vivado 项目

- 在步骤 3 中,将使用 System Generator IP 在 IP Integrator 中创建一个设计

- 在步骤 4 中,将实现设计并生成 FPGA 比特流(用于对 FPGA 编程的文件)

1、检查 AXI 接口

在这一步中,我们将回顾如何定义和创建 AXI 接口

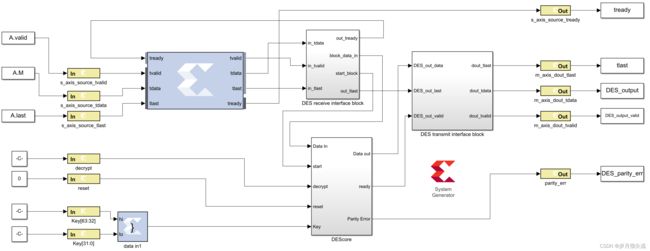

①、启动 System Generator 并打开 Simulink 将 Lab5\Lab5_1.slx 打开,如下图所示。这将打开如下图所示的设计。

这个复杂很多,是一个 DES 算法,用于数据加密/解密,由于本次设计只是为了使用 System Generator 实现 AXI 接口,并将涉及到出到 Vivado IP 的目录下以及在 Vivado 的工程中进行 IP 的使用,所以就不对设计文件进行具体分析,在模型文件中的空白区域有个英文的注释,对模型进行了详细的描述。

- 使用 AXI 接口允许导出到 Vivado IP 目录的设计有效地集成到使用 IP Integrator 的更大系统中

- 导出到 IP Catalog 的设计并不要求使用 AXI 接口

本设计使用以下 AXI 接口:

- 端口 s_axis_source_* 使用 AXI4-Stream 接口。所有网关输入和输出信号都以相同的名称(s_axis_source_)作为前缀,确保它们被分组到相同的接口中。所有端口的后缀都是有效的 AXI4-Stream 接口信号名称(tready、tvalid、tlast 和 tdata)

- 类似地,对 m_axis_dout_* 端口使用了一个 axis4-stream 接口

- 剩下的端口使用了一个 AXI4-Lite 接口。你可以使用以下步骤进行确认

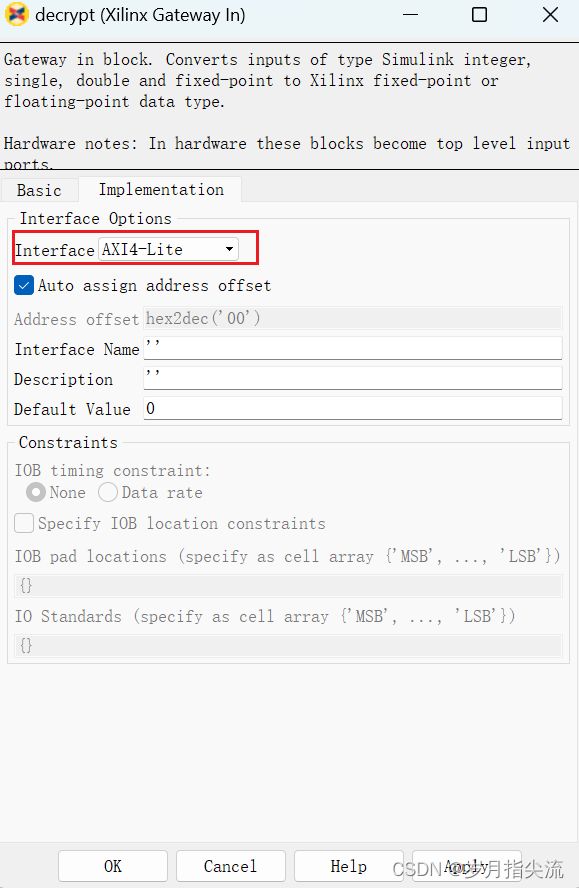

双击 Gateway In 的实例,decrypt(或者是其他的 reset,Keys[63:32],Keys[31:0] 以及 parity_err),在属性编辑界面选择 Implementation 这一项,Interface 选项设定的是否为 AXI4-Lite,依次将讲到的所有 Gate 实例都检查一遍,确保接口选择的是 AXI4-Lite。举例如下

点击 OK 保存并关闭

2、使用 System Generator IP 创建一个 Vivado 项目

在此步骤中,你将创建一个用于创建硬件设计的 Vivado 项目

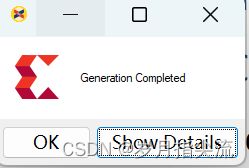

①、双击 System Generator 令牌以打开 Properties Editor,在属性编辑器中,确保为编译类型选择了 IP Catalog,单击 Generate 以 IP Catalog 格式生成设计

②、单击 OK 以关闭编译状态对话框

该设计以 IP Catalog 格式写入到 D:/Project/SystemGenerator_Prj/Lab5_1 目录中。现在,将把该 IP 导入到 Vivado IP Catalog 中,并在现有的示例项目中使用该 IP

③、开始创建 Vivado 工程

<1>、打开 Vivado 2017.4,打开后,点击 Create Project 创建新工程

<2>、点击 Next,将工程路径设置为刚刚 System Generaotr 导出文件对应的 D:/Project/SystemGenerator_Prj/Lab5_1 对应的目录路径,工程名字可默认,也可自行定义

<3>、点击 Next,选 RTL Project,把 Do not… 这个勾选上,然后 Next

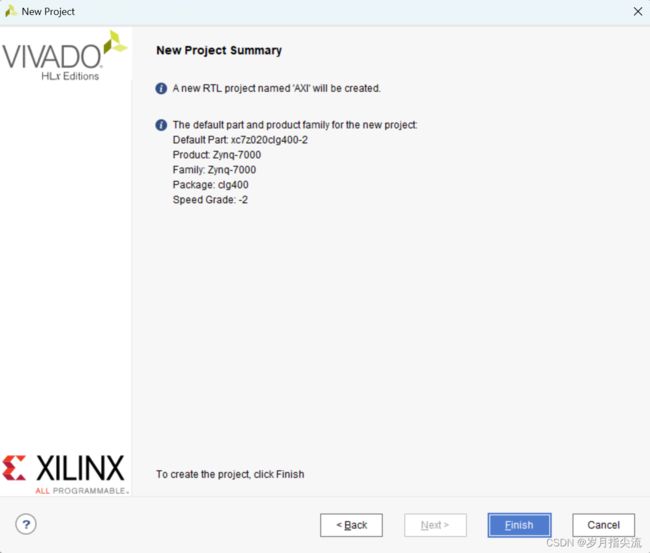

<4>、我这里选择我手头的一块 FPGA 板子,相关参数如下:

<5>、点击 Next,然后检查下总结,无误后点击 Finish。

3、创建 IP 集成设计(IPI)

在这一步中,将使用 System Generator IP 创建一个设计

①、单击 “Create Block Design” 窗格中的“创建块设计”

②、在 “Create Block Design” 对话框中,单击 “确定” 接受默认名称。你将首先为 System Generator IP 创建一个 IP 存储库,并将 IP 添加到存储库中,点击 OK

③、右键单击 Diagram 窗口并选择 IP Settings

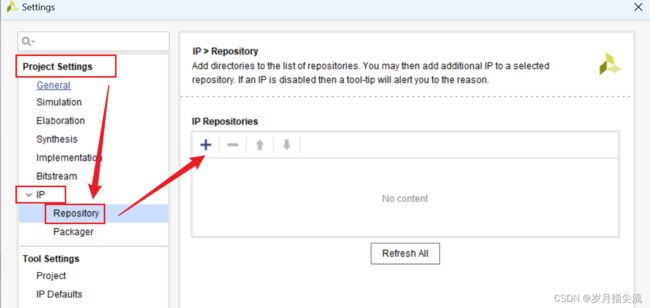

④、在 Settings 的界面下,依次找到 Project Settings -> IP -> Repository,然后在右边点击 “+”,添加相关的 IP 文件到存储库中

⑤、然后在弹出的文件选择界面,找到通过 System Generator 生成的 IP 文件,本设计的路径:D:\Project\SystemGenerator_Prj\Lab5_1\ip,选好 ip 后点击Select,然后再弹出的 Add Repository 对话框点 OK

这时候的 IP Repositories 界面就多了一项,点击 OK 保存并关闭

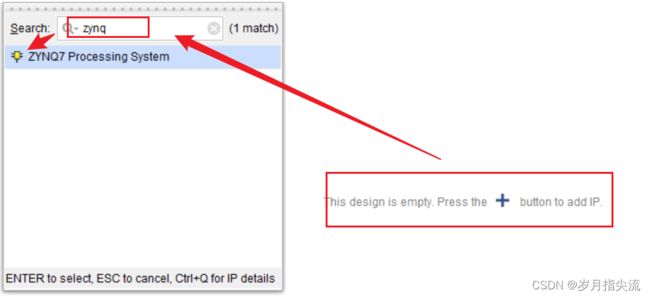

⑥、Diagram 界面中的中间有个 “+”,单击界面的“+”,然后再弹出的对话框,搜索 zynq,然后双击 ZYNQ7 Processing System,将其添加到设计中

⑦、添加成功后,点击 Diagram 下的 Run Block Automation

在出现的界面,确保 option 下的 Apply Board Preset 是选择的,然后保持默认配置,点击 OK

⑧、回到 Diagram 界面,在空白处右键单击,然后选择 Add IP

在对话框中输入 System Generaor 设计的文件名,本设计的名字为 Lab5_1,双击 Lab5_1

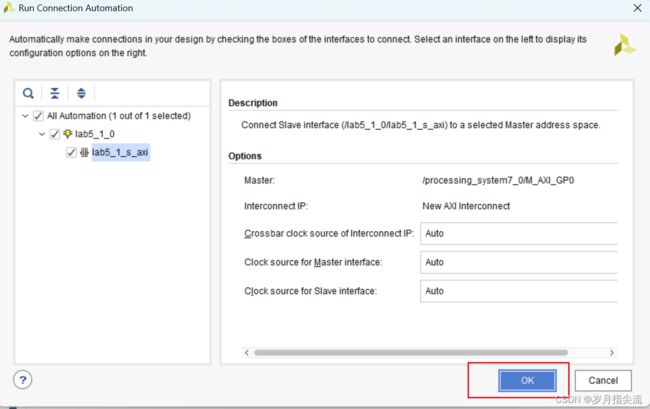

⑨、接下来就需要将 IP 连接到设计的其余部分,当使用 AXI 接口的时候,Vivado IP Integrator 提供了自动连接的功能,在 Diagram 的空白部分点一下,确保没选中 AXI 模块,然后点击 Run Connection Automation

在出现的对话框保持默认状态,然后按 OK 继续

等待一下会儿,连线完成,结果如下

⑩、双击 ZYNQ7 Processing System 以自定义 IP,在出现的界面点击 PS-PL Configuration,展开 HP Slave AXI Interface 然后选择 S AXI HP0 interface,将框框勾上,如下

点击 OK,将此端口添加到 ZYNQ7 Processing System

⑪、找到 AXI 模块的输入接口,s_axis_source,然后用鼠标拖到 processing_system7_0 的 S_AXI_HP0 接口,然后会出现绿色的勾

松开鼠标,弹出的对话框,直接点击 OK,让其自动连接

然后继续点击上方的 Run Connection Automation,出现的界面保持默认配置,点击 OK,使得其余的线连接完成,连接后的结果如下:

⑫、在 Diagram 的下方有个 Validate Design 的工具,使用它来进行设计的检查,确保无误

单击该按键,等待一会儿,出现检查结果,说明此时无误

点击 OK 关闭,此时已经相当于 System Generator 的设计已经成功的导入 IP Integrator 的设计中,存储库的 IP 可以在任何 Vivado 的项目中进行使用,只需要将存储库添加到项目中即可。

接下来将完成设计的最后一步,运行设计生成比特流数据。

4、实现设计

在这一步中,您将实现 IPI 设计并生成比特流

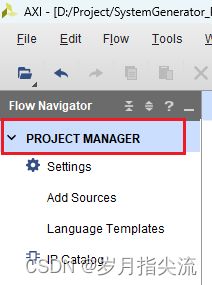

①、在 Flow Navigator 的界面下,点击 Project Manager,使其返回到工程管理的界面

②、Sources 的菜单下,对 Design Sources 下的设计即 design_1 右击,并单击 Generate Output Products

③、在 Generate Output Products 的对话框下,点击 Generate 开始启动以生成必要源文件的过程

④、等待生成完成后,再一次右击 design_1,选择 Create HDL Wrapper

⑤、保持默认的 Let Vivado manage wrapper and auto-update,然后点击 OK 退出窗口

⑥、这时候的 Design Sources 的源文件已经变成了 design_1_wrapper.v,这时的文件已经可以被用于综合,实现以及生成 FPGA下 载所需的比特流数据。

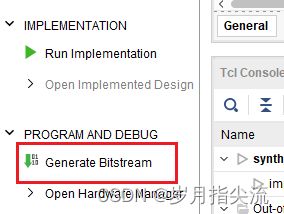

⑦、在 Flow Navigator 菜单下,点击 Generate Bitstream,用以启动其余部分

在弹出的界面点击 Yes,继续运行

出现 Launch Runs 的对话框,按 OK 开始运行

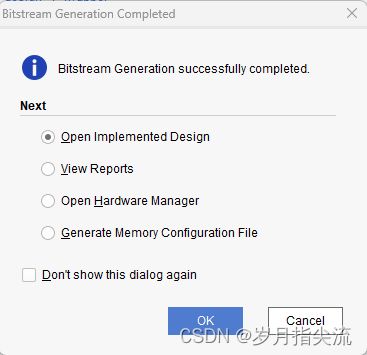

⑧、等待编译完成后,在出现的对话框中,选择 Open Implemented Design 并且点击 OK

⑨、观察此时已实现的设计,设计最后一步也到此结束,可以关闭 Vivado 了。

总结

在本实验中,你了解了如何将 AXI 接口添加到 System Generator 设计中,以及如何将 System Generator 设计保存为 IP Catalog 格式,合并到 Vivado IP Catalog 中,并在更大的设计中使用。还看到了在设计中使用 AXI 接口时, IP Integrator 如何通过连接自动化和提示大大提高生产率。

我的qq:2442391036,欢迎交流!