这两年“先进封装”被聊得很多。“封装”大概可以类比为对日用品打包装盒;保护电路芯片免受外界环境的不良影响。当然芯片封装还涉及到固定、散热增强,以及与外界的电气、信号互联等问题。而“先进封装”的核心还在“先进”二字上。

如果要量化,那么或许将bump pitch作为指标是比较合理的。所谓的bump pitch凸点间距,一般是用以形容芯片的数据I/O的,芯片需要更多的数据通讯“点”才能实现更高的传输效率。那么这些“点”之间的间距、密集程度,自然成为衡量数据通讯效率的关键。而先进封装就某个层面来看,也是bump pitch在缩小的过程。今年的《电子工程专辑》杂志将有一期封面故事是详谈先进封装的。本文不再对此多做赘述。

现在我们常说的“先进封装”更多的就是在指代die之间的3D堆叠或2.5D封装。而且这些封装方式也事实上实现了bump pitch相当程度的缩减。

一般的2.5D封装也就是指,将一大片die切成一个个小die(或叫chiplet),后将这些小die放在interposer(中介层)上(当然这只是2.5D封装的某一类方案)。这是在如今的die越做越大,大到良率低、成本过高之时的某种解决方案。

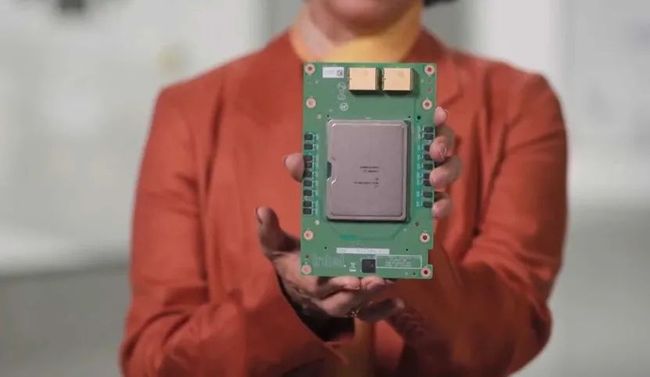

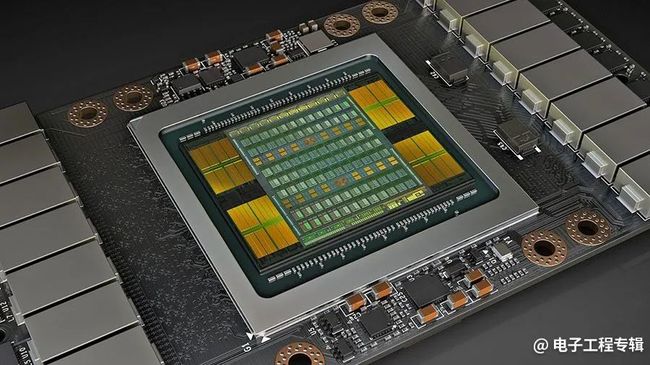

对die进行切分以后,整颗芯片就能做得非常非常大,而且利于做异构集成。去年的Intel Architecture Day上,Intel发布了面向数据中心的GPU芯片Ponte Vecchio,从照片看起来就相当巨大——这其中就有2.5D封装的功劳。虽然这颗芯片的2.5D封装并没有用interposer,而是另一种叫silicon bridge的方案。

Intel数据中心GPU,Ponte Vecchio

越做越大的interposer

此前在谈MCM GPU的时候,我们提到过一个词叫reticle limit,可理解为光刻机可处理的极限尺寸。也就是说即便不考虑良率和成本问题,以现有装置,一片die的尺寸再大也是有极限的。这个限制大约是858mm²。

当代常见芯片中的大die,以英伟达的GPU芯片Geforce RTX 3090为代表,其die size已经达到了628mm²。这其中虽然还有做大的空间,但显然一味的做大die已经不是个办法。所以将die切成chiplet,再封装起来的方案就变得很流行了。

台积电CoWoS封装,就如前文所述是将多个chiplet放在interposer上。这不就解决了reticle limit的尴尬了吗,虽然这其中还涉及到很多复杂的工程问题。

CoWoS技术发展至今也有些年头了,这项技术最早是从2012年就开始推行的。这是个2.5D晶圆级多芯片封装技术,能够实现比较高的互联密度和性能。其上的每个die(或chiplet)是通过micro-bump键合到interposer之上的。

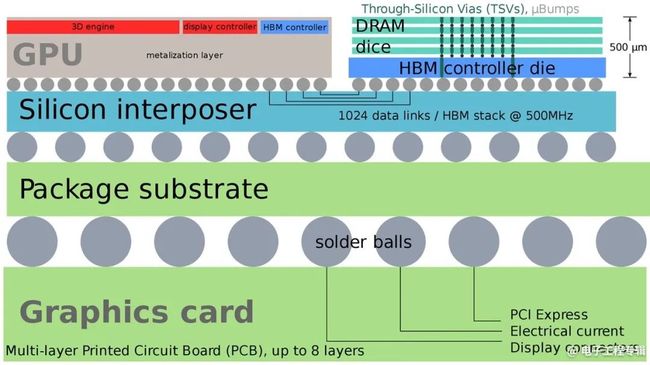

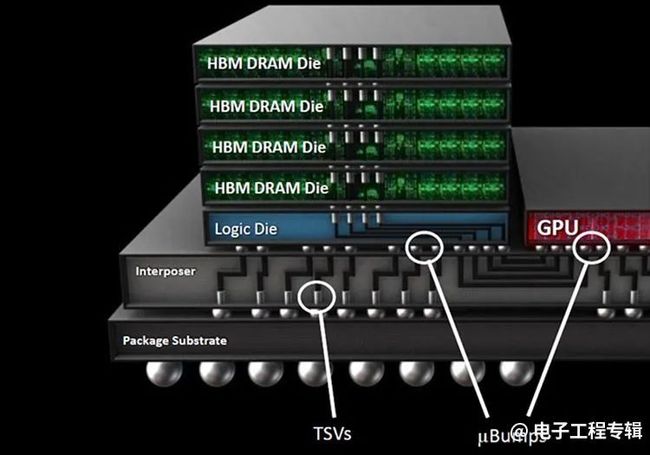

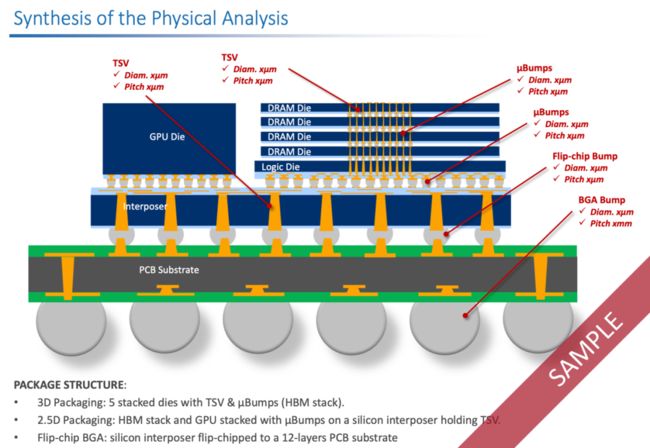

举个采用CoWoS封装颇具代表性的产品例子,Pascal架构的英伟达Tesla P100 GPU(2016年)。这款GPU芯片,主体部分是GP100图形计算die,与此同时周围有4颗HBM2存储堆栈(三星的HBM2颗粒),就是通过2.5D CoWoS技术共同封装于一片较大的silicon interposer之上的。

来源:System Plus Consulting

不过这其中也涉及到一个问题,interposer之上的die通过叠加自然可以让整个芯片做得很大,但这也意味着interposer本身需要做得很大才行。而interposer作为包含电路的层级,当然也会受到工艺的限制。台积电的第一代CoWoS-1,所用的interposer尺寸已经达到大约800mm²,十分接近reticle limit。

所以interposer自身的尺寸也成为一个必须解决的问题,尤其是在异构集成对芯片大小越来越贪婪的当下。

2500mm²的面积

台积电说基于CoWoS的芯片产品,已经应用在了不少超级计算机上——包括那些全球TOP 500超算。台积电表示,2020年TOP 500超算中有超过一半的算力,是来自于基于CoWoS-S封装技术的芯片。对于需要大规模堆砌算力、存储资源的芯片而言,HPC、AI等的确都是这类技术的重要应用场景。

经过数次迭代,去年台积电发布了第五代CoWoS封装技术CoWoS-S5(CoWoS-S系列为silicon interposer硅中介,有别于CoWoS-R),interposer的尺寸达到了2500mm²(注意这并非最终封装后的芯片尺寸),也就是三倍于reticle limit的面积。

台积电是在去年的ECTC(IEEE电子元件及技术会议)上展示的这项技术。CoWoS-S5的主要特性包括iCap(台积电的PDN供电网络)、新的互联堆栈、新的TSV(硅通孔)结构,以及更好的TIM(热界面材料)。

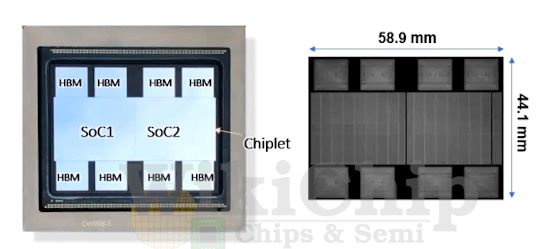

来源:Wikichip

在ECTC之上,台积电展示的是一枚由11个die组成的大型芯片。中间是两颗比较大的SoC,以及1颗较小的die(图片中最右侧的长条die);四周用了8个HBM2E存储堆栈(128GB?)。承载这些die的interposer尺寸达到了58.9x44.1mm(2597.49mm²)。

台积电表示,应用了HBM2E存储的版本已经进行了生产验证,而可应用HBM3的方案尚在开发中。

这代2.5D封装的一些改进

有在关注台积电CoWoS技术的读者应该知道,interposer要突破reticle limit的方式是采用全幅的mask拼接。两个mask组合,两者彼此会有一部分的重合——重合部分的RDL(redistribution layer)互联部分需要做到一致。如此一来,通过拼接就能构成连续的线路。

CoWoS此前迭代也是这么做的,从一代的800mm²,做到二代1200mm²、1700mm²(前两年有报道说台积电发布全球最大的CoWoS interposer就是1700mm²)。对于CoWoS-S5而言,尺寸3倍于reticle limit也就不但需要2个全幅mask拼接了。台积电的方案是4份mask拼接。

4个mask,每个都需要有与另外三者重合的部分,构成最终interposer过曝的拼接边缘部分,达成当代最大的interposer尺寸。

此外,除了面积做大,CoWoS-S5也用了新的金属堆栈。因为interposer之上的die增多以后,尤其是逻辑die,线路复杂性也会提升。而且前文也提到HBM2E存储堆栈应用于这代interposer已经得到验证。HBM2E的传输速率为3.2GT/s。

未来要采用HBM3的话,速率提升至4GT/s,信号完整性可能会成为一大问题。所以CoWoS-S5引入新的金属堆栈、新的亚微米层(双镶嵌线路)——至多5个这样的亚微米层。台积电表示,新的金属堆栈能够降低金属电阻以及via接触电阻超过50%。

与此同时,CoWoS-S5也引入了iCap(integrated capacitor)——嵌入式深槽电容(DTC)。台积电最初是于2019年发布的iCap,其电容密度能够达到最高340 nF/mm²,相比于此前的HD-MiM(high-k高密度metal-insulator-metal),有着非常高的提升。单个Si interposer可达成的总电容值为64μF。

CoWoS-S5封装技术的最后一个重点,也在于引入新的TIM热界面材料。CoWoS有顶盖和环形封装两种。在环形封装中,die上表面是与散热器直接接触的;而顶盖封装方案下,散热铁盖要通过热界面材料与die接触。凝胶型的TIM导热系数通常为10W/K,台积电认为这对于HPC、AI应用是不够的。所以CoWoS-S5为此引入了新型TIM,据说导热系数可超过20W/K。

从CoWoS大致可以窥见先进封装的未来——当然此处我们尚未探讨可与CoWoS做配合的其他3DFabric封装方案。另外2.5D封装方案并不仅有interposer这一种。文首提到Intel发布的数据中心GPU大芯片Ponte Vecchio,其2.5D封装采用的是更为经济的silicon bridge方案(Intel的EMIB封装)。这种“硅桥”是直接嵌入在封装基板中的,而不需要interposer,成本会比interposer方案明显更低。

值得一提的是,在台积电、Intel等厂商的宣传中,bump pitch缩小是此类先进封装工艺“先进”程度非常重要的一项指标。更多先进封装相关技术,未来《电子工程专辑》杂志将对此有更系列的探讨和报道。