输入输出系统——第五章

输入输出系统——第五章

-

- 一、概述

-

- 1. 输入输出系统的发展状况

-

- 1. 早期

- 2. 接口模块和DMA阶段

- 3. 具有通道结构阶段

- 4. 具有I/O处理机的阶段

- 2. 输入输出系统的组成

-

- 1. I/O软件

-

- 1. I/O指令

- 2. 通道指令

- 2. I/O硬件

- 3. I/O设备与主机的联系方式

-

- 1. I/O设备的编址方式

-

- 1. 统一编址

- 2. 不统一编址(单独编址)

- 2. 设备选址

- 3. 传送方式

- 4. 联络方式

-

- 1. 立即响应

- 2. 异步工作采用应答信号

- 3. 同步工作采用同步时标

- 5. I/O设备与主机的连接方式

-

- 1. 辐射式连接

- 2. 总线连接

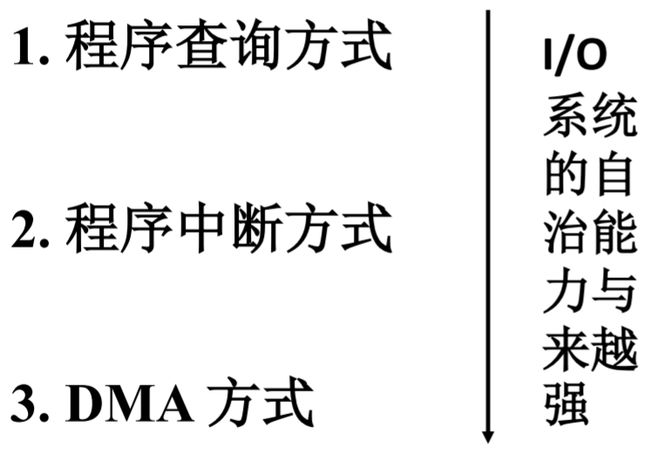

- 4. I/O设备与主机信息传送的控制方式

-

- 1. 程序查询方式

- 2. 程序中断方式

- 3. DMA方式

- 4. 三种方式的CPU工作效率比较

- 二、外部设备

-

- 1. 概述

- 2. 输入设备

-

- 1. 键盘

- 2. 鼠标

- 3. 触摸屏

- 3. 输出设备

-

- 1. 显示器

- 2. 打印机

- 4. 其他

- 5. 多媒体技术

- 三、I/O接口

-

- 1. 概述

- 2. 接口的功能和组成

-

- 1. 总线连接方式的I/O接口电路

- 2. 接口的功能和组成

- 3. I/O接口的基本组成

- 3. 接口类型

-

- 1. 按数据 传送方式 分类

- 2. 按功能 选择的灵活性 分类

- 3. 按 通用性 分类

- 4. 按数据传送的 控制方式 分类

- 四、程序查询方式

-

- 1. 程序查询流程

-

- 1. 查询流程

- 2. 程序流程

- 2. 程序查询方式的接口电路

- 五、程序中断方式

-

- 1. 中断的概念

- 2. I/O中断的产生

- 3. 程序中断方式的接口电路

-

- 1. 配置中断请求器和中断屏蔽触发器

- 2. 排队器

- 3. 中断向量地址形成部件

- 4. 程序中断方式接口电路的基本组成

- 4. I/O中断处理过程

-

- 1. CPU响应中断的条件和时间

-

- 1. 条件

- 2. 时间

- 2. I/O中断处理过程

- 5. 中断服务程序流程

-

- 1. 中断服务程序的流程

- 2. 单重中断和多重中断

- 3. 单重中断和多重中断服务程序流程对比

- 4. 主程序和服务程序抢占CPU示意图

- 六、DMA方式

-

- 1. DMA方式的特点

-

- 1. DMA和程序中断两种方式的数据通路

- 2. DMA 与主存交换数据的三种方式

-

- 1. 停置CPU访问主存

- 2. 周期挪用(周期窃取)

- 3. DMA与CPU交替访问

- 2. DMA接口的功能和组成

-

- 1. DMA接口的功能

- 2. DMA接口的组成

- 3. DMA的工作过程

-

- 1. 传送过程

-

- 1. 预处理

- 2. DMA传送过程示意

- 3. 数据传送过程(输入)

- 4. 数据传送过程(输出)

- 5. 后处理

- 2. DMA接口与系统的连接方式

-

- 1. 具有公共请求线的DMA请求

- 2. 独立的DMA请求

- 3. DMA方式与程序中断方式的比较

- 4. DMA接口的类型

-

- 1. 选择型

- 2. 多路型

- 3. 多路型 DMA 接口的工作原理

- 补充知识

-

- 1. 部分逻辑电路符号

-

- 1. 非门

- 2. 与非门

一、概述

1. 输入输出系统的发展状况

1. 早期

CPU和I/O设备以分散连接的方式进行连接。

分散连接:每个设备都有独立的控制电路。

特点:

- CPU和I/O设备紧耦合,增减外部设备苦难

- CPU和I/O设备以程序查询方式进行连接,串行工作

- I/O设备进行输入、输出时,CPU必须运行相应程序或处于停等状态

2. 接口模块和DMA阶段

出现原因:由于外设的增多,难于增减外部设备的分散连接模式被淘汰。

这一阶段,I/O接口和DMA控制器与CPU相互配合,完成输入、输出操作。I/O设备和CPU信息交换传输控制方式有两种:

- 中断方式

- DMA方式

特点:在信息传输过程中、信息传输完成后,CPU仍要参与部分信息传输的处理工作。

3. 具有通道结构阶段

出现原因:为了使CPU和I/O设备实行并行工作,使输入输出系统数据的管理控制从主机中脱离出来。

特点:

- 有自己的指令系统、控制器,部分通道还有自己的存储器

- 通过执行通道程序,可以控制连接在通道上的I/O设备直接和主机进行信息传输。

- 通道实际上是一种小型的DMA处理机

- 通道程序就是由通道指令组成的程序

4. 具有I/O处理机的阶段

出现原因和通道的出现原因一致。这一阶段可以使用专用的I/O处理机管理I/O设备,同时也可以将微处理器和与主机CPU一样的处理器当作I/O处理机来使用。当使用处理器作为I/O处理机来使用时,在I/O设备空闲时,该处理器可分担主机CPU的压力,帮助其执行运算任务。

2. 输入输出系统的组成

1. I/O软件

1. I/O指令

I/O指令就是CPU指令集中的一部分,I/O指令结构如下:

- 操作码:I/O指令的操作码相当于I/O指令的标志,表明这个指令是I/O指令

- 命令码:相当于CPU指令集中普通指令的操作码,指出要对I/O设备做出什么操作

- 设备码:I/O设备或I/O端口的地址

I/O端口:I/O设备中的某个寄存器

2. 通道指令

通道指令就是通道自身拥有的指令集。

通道的工作流程

- 编程人员为了使应用程序能够调用外部设备工作,在应用程序中编写了广义I/O指令,广义I/O指令给出了如下信息

- 参数数据传输的I/O设备

- 数据传输主存的首地址

- 传输数据的长度

- 传输的方向:是向I/O设备传输数据还是向主存传输数据

- 操作系统根据广义I/O指令给出的参数以及要执行的操作,编写一个由通道指令构成的通道程序,并将其放在内存或者通道自身的存储器的指定位置,然后启动通道进行工作

- 通道拿到通道程序的首地址后,执行通道程序,控制I/O设备完成相应的操作

通道指令需要给出要传输数据(数组)的首地址、传输字数、操作命令、传输方向、设备地址等。通道指令一般比较长。

关于IBM/370

- 通道指令长度为64位

- 通道的下面可以带若干个子通道,子通道可以并行工作

- 每个子通道可以连接多个设备控制器

- 每个设备控制器可以连接多个设备

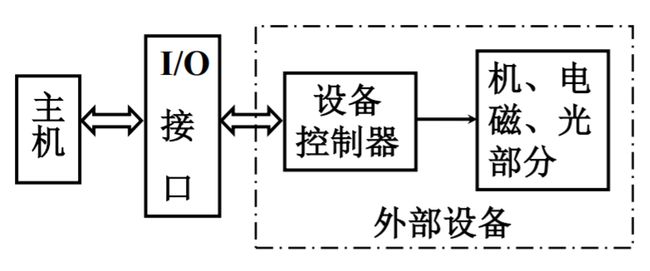

2. I/O硬件

- 采用接口模式的I/O硬件包括:设备、I/O接口

- 设备通过接口连接在总线上,和主机完成信息交换

- 采用通道模式的I/O硬件包括:设备、设备控制器、通道

- 设备连接设备控制器,设备控制器连接子通道,子通道连接通道

3. I/O设备与主机的联系方式

1. I/O设备的编址方式

I/O设备的编址方式有两种:统一编址、不统一编址。

1. 统一编址

核心思想:把I/O设备的地址看成是内存地址的一部分,在进行内存编址时统一进行编址。

实现原理:

- 取内存地址中的部分地址作为I/O设备或I/O端口的地址

- 如果输入、输出指令或者访存指令的地址码在I/O地址范围内,那么这次的操作实际上是针对I/O设备进行的

特点:

- CPU可以用取数、存数指令对I/O设备进行管理、控制,不需要特定的I/O指令

- CPU的指令集相对简单

适用情况:当内存系统编制空间较大时,可以采用这种方式

2. 不统一编址(单独编址)

核心思想:在内存地址空间之外,专门设置一个I/O设备的地址空间

虽然两个地址空间是独立的,但他们对应的二进制代码范围,是存在重合的

比如:一个20位的内存,寻址空间为1M,在对I/O设备进行编址时,地址范围为 16 个 0 到 16 个 1 16个0 \, 到 \, 16个1 16个0到16个1(即64K)。此时两个地址空间的二进制代码是存在重合的。

问题:对于相同的二进制地址,如何区分一个指令到底是对内存进行操作的还是对I/O设备进行操作的?

解决方案:采用专门的I/O指令对I/O设备进行操作。

因此这种编址方案的特点就是:有专门的I/O指令对I/O设备进行控制。

2. 设备选址

用设备选择电路识别是否被选中

用CPU给出的地址和设备保存的自己的地址进行比较

3. 传送方式

- 串行:数据一位一位的进行传输

- 并行:同时有多位数据在多条数据线上进行传输,通常情况下数据线的条数是8的倍数

4. 联络方式

外部设备在接收、发送数据的响应情况。

1. 立即响应

接收到数据后立即显示,比如LED灯,在接收到数据后立即以亮/不亮的方式显示接收到的数据。

适用于一些结构简单,状态、数量比较少的设备。

2. 异步工作采用应答信号

异步工作分为两种,可以并行传输,也可以串行传输。

并行传输

CPU和接口之间一般都是并行传输,所以现在讲的异步工作应答信号主要是I/O接口和I/O设备之间采用的。

- I/O接口和I/O设备之间有多条数据线组成了一条类似数据总线的数据线(完成并行工作)

- I/O接口和I/O设备采用应答信号,比如,当I/O设备要接收数据时

- I/O端口将数据准备好后,通过一个== R e a d y Ready Ready==信号告诉I/O设备:端口中的数据已经准备好了

- I/O设备对端口中的数据进行读取,并给出应答信号

- 如果是I/O设备要输入数据到CPU或主机:

- 当I/O接口中的数据缓冲器空了后,就会向I/O设备发送== R e a d y Ready Ready==信号,告诉I/O设备,可以向I/O接口发送数据了

- I/O设备向I/O接口发送数据,并给出应答信号

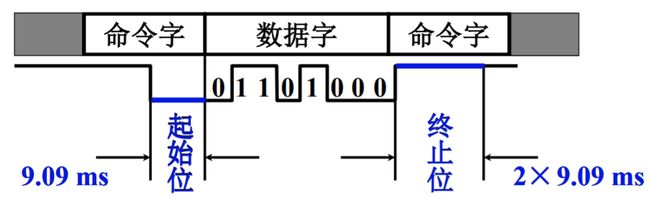

串行传输

- 传输要有起始位和终止位,如图

- 占1位的起始位,共 9.09 m s 9.09ms 9.09ms

- 占2位的起始位,共 2 × 9.09 m s 2 \times 9.09ms 2×9.09ms

- 在起始位和终止位之间,是若干位的数据位

3. 同步工作采用同步时标

5. I/O设备与主机的连接方式

有两种连接方式:辐射式连接、总线连接。

1. 辐射式连接

就是我们前面介绍过的分散连接。

如图

2. 总线连接

外部设备通过接口和主机进行连接。

接口的作用:

- 向外部设备传送主机的命令

- 向主机传送外部设备状态信息

- 完成数据缓存、数据格式变化等

优点:便于增删设备

4. I/O设备与主机信息传送的控制方式

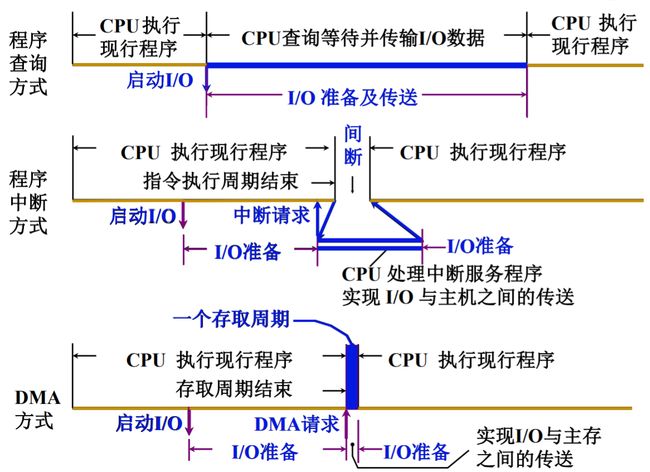

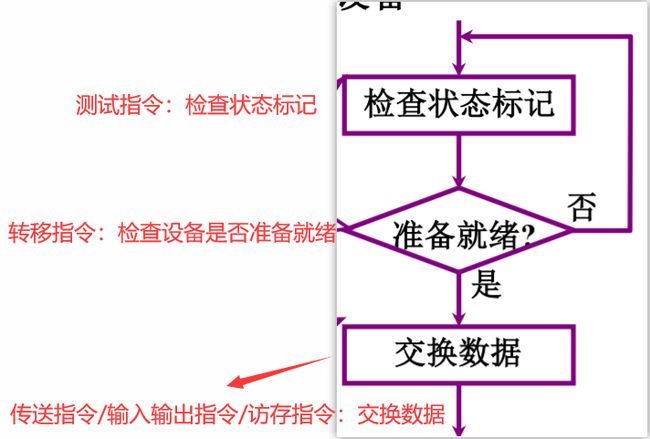

1. 程序查询方式

CPU从I/O设备读数据流程图

I/O设备和I/O接口的工作流程

- I/O设备接到CPU指令后,开始数据准备

- 经过较长时间的准备后,I/O设备将准备好的数据送入I/O接口的数据缓冲区,然后I/O接口将工作状态标志转为”已准备就绪“。I/O状态保存在I/O接口的触发器中

注意:在I/O设备准备数据过程中,CPU一直在检查I/O状态,无法执行其他指令。

特点:

- 外部设备和内存的信息交换必须通过CPU

- CPU在I/O设备准备数据的过程中处于停等状态,效率低下

- I/O设备和CPU的工作是串行的

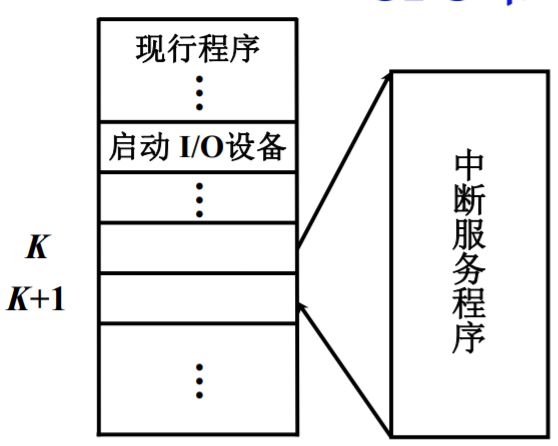

2. 程序中断方式

I/O设备的工作过程可以分为两个阶段:

- 自身准备(包括数据准备)

- 与主机交换信息

在程序查询方式中,CPU在I/O设备工作的两个阶段都要参与。

程序中断方式对程序查询方式进行了优化:

- 在I/O设备的"自身准备阶段",CPU不参与I/O工作,可以执行其他程序

- 当I/O设备需要与主机交换信息时(自身准备已完成),CPU暂停现行程序,参与I/O工作

实例

- CPU在执行现行程序时遇到了I/O指令

- CPU首先启动I/O设备,然后继续执行现行程序

- 当I/O设备完成自身准备==向CPU发出"中断请求"==后,CPU暂停执行现行程序,参与执行I/O设备的数据输入、输出工作

- 执行完I/O操作后,CPU继续执行现行程序

在这个过程中,CPU没有因I/O设备准备数据而出现"停等"现象。

优点:CPU一定程度上从I/O设备的数据输入、输出操作出解脱出来,执行效率更高了

缺点:

- I/O设备和内存的数据传输仍然需要CPU的参与

- CPU保存程序执行断点及恢复断点所耗费的指令和时间也浪费了CPU的处理效率

程序中断方式流程

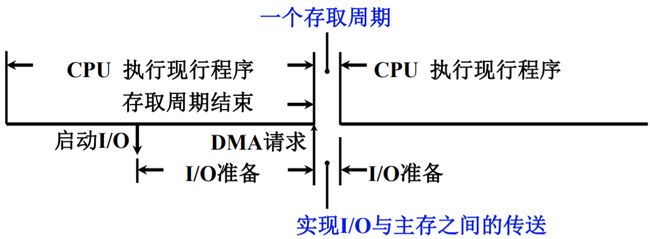

3. DMA方式

主存和I/O之间有一条直接数据通道,主存和I/O在DAM控制器控制下可以直接进行数据交换。采用的方式叫做周期挪用(周期窃取)。

DMA方式工作流程(CPU在执行现行程序时,遇到I/O操作)

- CPU首先启动I/O,然后继续执行现有程序

- I/O设备进行自身准备,准备完成后由DMA控制器发出DMA请求

- CPU接到DMA请求后,让出总线的使用权一个存取周期,在这个存取周期内

- CPU不能使用主线访问主存

- CPU虽然不能使用主线,但仍可继续执行现行程序(现代计算机一般是预读指令)

- DMA占用总线使用权,控制主存和I/O设备进行数据交换。完成后让出总线使用权给CPU

在这个过程中:

- CPU不需要中断现行程序的执行

- CPU从I/O设备的数据输入、输出中彻底解脱出来,CPU和I/O实现了并行工作

- 因为数据输入、输出占用了一个存取周期的总线使用权,因此称作周期挪用方式

4. 三种方式的CPU工作效率比较

发展趋势

二、外部设备

1. 概述

外部设备大致分为三类:

- 人机交互设备 键盘、鼠标、打印机、显示器

- 计算机信息存储设备 键盘、光盘、磁带

- 机——机通信设备 调制解调器等

2. 输入设备

1. 键盘

按键,判断哪个键按下,将此键翻译成ASCII码(编码键盘法)

2. 鼠标

- 机械式 金属球、电位器

- 光电式 光电转换器

3. 触摸屏

3. 输出设备

1. 显示器

- 字符显示 字符发生器

- 图形显示 主观图像

- 图像显示 客观图像

2. 打印机

- 打击式 点阵式(逐字、逐行)

- 非打击式 激光(逐页)喷墨(逐字)

4. 其他

- A/D、D/A 模拟/数字(数字/模拟)转换器

- 终端 由键盘和显示器组成

- 完成显示控制与存储、键盘管理及通信控制

- 汉字处理 汉字的输入、存储、输出

5. 多媒体技术

什么是多媒体?

多种媒体技术和手段相结合进行综合应用,给人以更多的视、听或者动作上的感受。

多媒体计算机的关键技术?

三、I/O接口

1. 概述

为什么要设置接口?(接口的功能)

- 实现设备的选择

- 实现数据缓冲达到速度匹配

- 实现数据串行——并行的格式转换

- 实现电平转换

- 传送控制命令

- 反应设备的状态(“忙”、“就绪”、“中断请求”)

2. 接口的功能和组成

1. 总线连接方式的I/O接口电路

如图

- 设备选择线:参与信息传输设备的设备地址或端口地址。单向线

- 数据线:完成数据的输入、输出。条数和接口的类型有关。双向线

- 命令线:来自主机的命令通过命令线来到I/O接口,命令经缓冲、译码后可以控制设备做相应的操作。单向线

- 状态线:将状态信息送给主机,使主机了解外部设备的状态信息。单向线

2. 接口的功能和组成

下图展示了接口的组成和其实现的功能的对应关系:

| 功能 | 组成 |

|---|---|

| 选址功能 | 设备选择电路 |

| 传送命令的功能 | 命令寄存器、命令译码器 |

| 传送数据的功能 | 数据缓冲寄存器 |

| 反应设备状态的功能 | 设备状态标记 |

设备状态标记是利用一系列的触发器来实现的,下表展示了各触发器及其标记的状态

| 触发器 | 取值 | 标记状态 |

|---|---|---|

| 完成触发器D | 0 | 准备工作尚未完成(准备发送数据或准备接收数据) |

| 1 | 准备工作已经完成 | |

| 工作触发器B | 0 | 外部设备处于“空闲状态” |

| 1 | 外部设备“忙” | |

| 中断请求触发器INTR | 0 | 未发出中断请求 |

| 1 | 发出中断请求 | |

| 屏蔽触发器MASK | 0 | 可以发出中断请求 |

| 1 | 主机此时处理程序的优先级高于此次I/O操作,不能发出中断请求 |

3. I/O接口的基本组成

3. 接口类型

1. 按数据 传送方式 分类

- 串行接口 如 Intel 8255

- 并行接口 如 Intel 8251

2. 按功能 选择的灵活性 分类

- 可编程接口 如 Intel 8255、Intel 8251

- 不可编程接口 如 Intel 8212

3. 按 通用性 分类

- 通用接口 如 Intel 8255、Intel 8251

- 专用接口 如 Intel 8279、Intel 8275

4. 按数据传送的 控制方式 分类

- 中断接口 如 Intel 8259

- DMA接口 如 Intel 8257

四、程序查询方式

1. 程序查询流程

1. 查询流程

单个设备

多个设备

注意:多个设备之间存在查询的优先级次序。

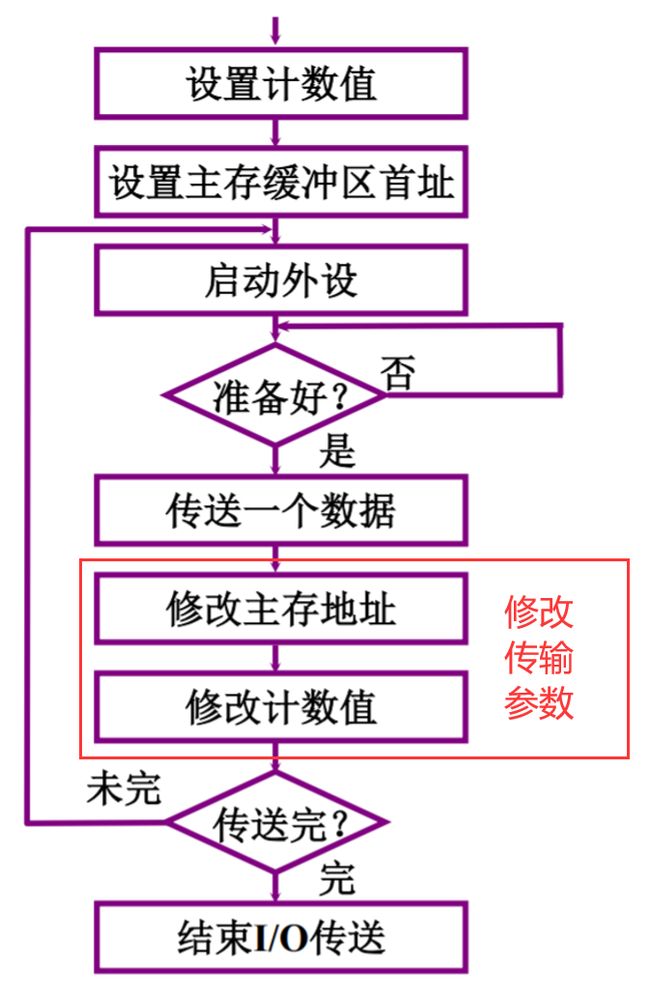

2. 程序流程

首先,保存寄存器的内容。原因:程序查询方式要完成内存和外部设备之间数据的输入输出,需要借助CPU中的某一个寄存器,对数据进行暂存。如果寄存器原先的数据是有用的,就需要对这些数据进行保存。保存寄存器数据后,执行如下流程:

程序流程图

关于计数值

- 设置计数值的目的:控制传输的数据量

- 计数值的取值方案有两种:假如现在要传输N个字

- 计数器的值就设置为== N N N==。每完成一个字的传输,计数器的值-1,直到计数器值=0,说明此次传输完成,传输结束

- 计数器的值设置为== − N -N −N==,并用补码来表示这个复数,每完成一个字的传输,计数器的值+1,当计数器值=0,传输结束

2. 程序查询方式的接口电路

程序查询方式的接口电路(以输入为例进行介绍)

- CPU通过地址线给出外部设备的地址

- 设备选择电路将自己的设备地址(或端口号)和地址线上的地址进行比较,如果相同,说明这次启动的设备就是连接在这个接口电路上的外部设备。== S E L SEL SEL==信号有效

- 在启动命令和== S E L SEL SEL==信号都有效的前提下,对两个状态标记进行置位:(图中的Q模块)请回忆各触发器及其标记的状态

- 完成触发器D=0,表明数据还未准备好

- 工作触发器B=1,表明设备开始工作,处于“忙”状态。同时触发器B启动设备,图中的②

- 设备开始工作后,准备数据并将数据通过输入数据线保存到数据缓冲DBR中。图中的③

- 数据保存到DBR后,设备的工作结束,设备通过设备的状态线向接口电路送入设备工作结束信号。图中的④。设备工作结束信号会修改接口电路中的两个状态信号:

- 完成触发器D=1,表明数据准备好。同时这个信号会被送出,图中的⑤。在这一步之前,CPU始终处于空等状态

- 工作触发器B=0,表明设备工作完成,处于空闲状态

- DBR中的数据通过数据线被送出

五、程序中断方式

1. 中断的概念

中断:CPU在执行程序过程中,如果发生特殊事件,CPU要中断当前程序的处理,去处理特殊事件,通过执行中断服务程序的方式来进行处理。处理结束后,CPU要返回到中断程序的断点,继续执行该程序。

这里的中断服务程序应该是指发出中断请求的程序

CPU中断当前程序执行时,会保存程序断点信息,继续执行该程序时会恢复断点信息。

2. I/O中断的产生

打印机引起的I/O中断

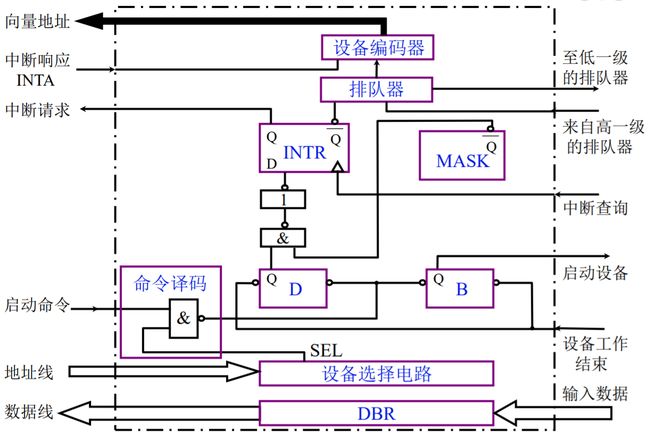

3. 程序中断方式的接口电路

学习四点内容

- 配置中断请求触发器和中断屏蔽触发器

- 排队器

- 中断向量地址形成部件

- 程序中断方式接口电路的基本组成

1. 配置中断请求器和中断屏蔽触发器

如图 重点提醒:请结合 程序查询方式的接口电路的电路图 以及 各触发器及其标记的状态 一起观看

并尝试将两张图结合在一起。同时需要注意:虽然将两张图放在一起理解,但实际上两种方式的原理是有差别的:

- 程序查询方式在完成触发器发出完成信号之前,CPU始终处于停等状态

- 程序中断方式在完成触发器发出完成信号之前,CPU一直在执行自己的工作

- 当== D = 1 , M A S K ‾ = 1 D=1,\overline{MASK}=1 D=1,MASK=1==,两个信号经与非运算后变为0,再经非运算变为1,INTR变为1(这里方框中的1代表输出为1)

- 当收到来自CPU的中断查询信号后,INTR值被送入CPU,产生中断请求

2. 排队器

排队器的实现有两种方式:

- 硬件 在CPU内或在接口电路内(链式排队器)

- 软件 见第八章

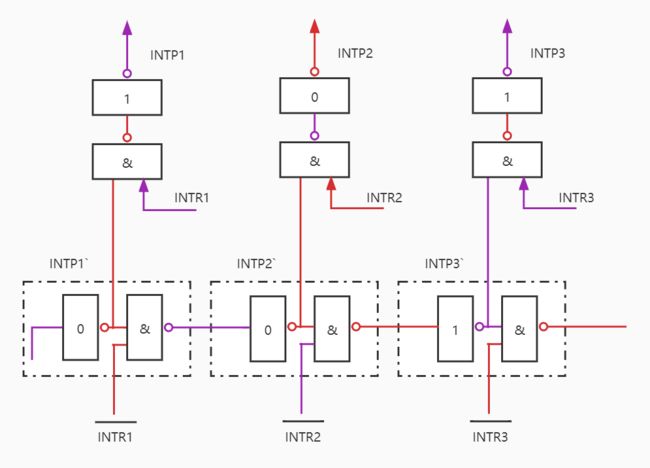

链式排队器电路图 (每一个 I N T P ‘ INTP` INTP‘包含了左侧的一个非门和右侧一个与非门(虚线内))。与非门工作原理

初始状态 (红色代表高电平,紫色代表低电平)

请特别注意:虚线框内左侧方框中的 0 是非门输入端信号,和非门右侧信号是相反的!

- I N T R 1 ‾ \overline{INTR_1} INTR1表示 INTR信号取非。 I N T R i ‾ = 0 \overline{INTR_i} = 0 INTRi=0代表i设备有请求

- 先来看 I N T P i ‘ INTP_i` INTPi‘ 的初始状态

- 先看 I N T P 1 ‘ INTP_1` INTP1‘:

- 非门左侧输入为 0(图中方框中标记为输入状态),经非门后变为1, I N T P 1 ‘ INTP_1` INTP1‘向上的线输出为1,表现为高电平

- I N T R 1 INTR_1 INTR1未发出中断请求,即 I N T R 1 = 0 , I N T R 1 ‾ = 1 INTR_1=0,\overline{INTR_1}=1 INTR1=0,INTR1=1,1 和 1 经与非门后变为 0

- 再看 I N T P 2 ‘ INTP_2` INTP2‘:

- 非门左侧输入为 0,经非门后变为1, I N T P 2 ‘ INTP_2` INTP2‘向上的线输出为1,表现为高电平

- I N T R 2 INTR_2 INTR2未发出中断请求,即 I N T R 2 = 0 , I N T R 2 ‾ = 1 INTR_2=0,\overline{INTR_2}=1 INTR2=0,INTR2=1,1 和 1 经与非门后变为 0

- …

- 依次类推,整个排队电路 I N T P i ‘ INTP_i` INTPi‘均表现为高电平

- 再来看看 I N T P i INTP_i INTPi 的初始状态

- 经过前面的分析,我们知道:所有的 I N T P ‘ INTP` INTP‘ 均向 I N T P INTP INTP 输入 1

- 所有的设备都未发出请求,则所有的 I N T R INTR INTR 都为 0

- 1 和 0 经与非门后输出为1,经过非门后,又变为 0

- 即初始状态下,所有 I N T P INTP INTP 都为0

当设备1发出中断请求 (即 I N T R 1 = 1 INTR_1 = 1 INTR1=1)

- 先来看 I N T P ‘ INTP` INTP‘

- 先看 I N T P 1 ‘ INTP_1` INTP1‘

- 非门左侧输入为0,经非门后变为1,向上的线输出为1, I N T P 1 ‘ INTP_1` INTP1‘表现为高电平

- I N T R 1 ‾ = 0 \overline{INTR_1}=0 INTR1=0,1 和 0 经与非门后向右输出为 1

- 再看 I N T P 2 ‘ INTP_2` INTP2‘

- 非门左侧输入为1,经非门后变为0,向上的线输入为0, I N T P 2 ‘ INTP_2` INTP2‘变现为低电平

- I N T R 2 ‾ = 1 \overline{INTR_2}=1 INTR2=1,0 和 1 经与非门后向右输出为 1,

- …

- 之后的 I N T P ‘ INTP` INTP‘ 和 I N T P 2 ‘ INTP_2` INTP2‘一致,均表现为低电平

- 先看 I N T P 1 ‘ INTP_1` INTP1‘

- 再来看 I N T P INTP INTP

- 先看 I N T P 1 INTP_1 INTP1

- I N T P 1 ‘ = 1 , I N T R 1 = 1 INTP_1`=1,INTR_1=1 INTP1‘=1,INTR1=1,1 和 1 经与非门后变为0,再经过非门表现为1,即== I N T P 1 = 1 INTP_1 = 1 INTP1=1==

- 再看 I N T P 2 INTP_2 INTP2

- I N T P 2 ‘ = 0 , I N T R 2 = 0 INTP_2`=0,INTR_2=0 INTP2‘=0,INTR2=0,0 和 0 经与非门后变为1,再经过非门表现为0,即== I N T P 2 = 0 INTP_2 = 0 INTP2=0==

- …

- 其后的 I N T P INTP INTP 和 I N T P 2 INTP_2 INTP2 一致,均表现为 低电平

- 先看 I N T P 1 INTP_1 INTP1

当设备2发出中断请求(即 I N T R 2 = 1 INTR_2 = 1 INTR2=1) 请自行分析(实际答案在图中给出了)

总结

- 对于 I N T P ‘ INTP` INTP‘

- 初始状态下,所有的 I N T P ‘ INTP` INTP‘ 均表现为 高电平

- 当某一个设备发出中断请求时,其前的 I N T P ‘ INTP` INTP‘均表现为高电平(包括它自己),其后的均表现为低电平

- 对于 I N T P INTP INTP

- 初始状态下,所有 I N T P INTP INTP 均表现为低电平

- 当某一个设备发出中断请求时,其对应的 I N T P INTP INTP 表现为高电平,其他的均表现为低电平

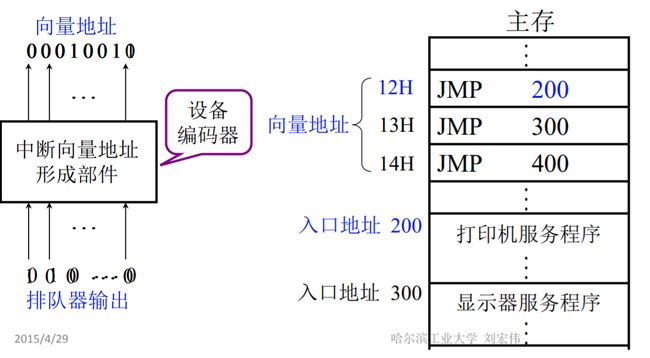

3. 中断向量地址形成部件

解决问题:找到中断程序的入口地址

入口地址的产生有两种方法:

- 由软件产生 见第八章

- 硬件向量法 由硬件产生向量地址,再由向量地址产生入口地址

工作流程分析

- 外部设备数 = 排队电路INTP数 = 排队器输出信号数 = 中断向量地址形成部件信号输入数

- 排队器每次输出的信号仅包含一个1,其他均为0,中断向量地址形成部件相当于一个设备编码器,针对每一个输出给出向量地址

- 向量地址指向主存中的一个存储单元,生成后经数据线送往CPU

- CPU根据向量地址找到对应存储单元,根据存储信息找到中断服务程序的入口地址

- JMP代表跳转指令

4. 程序中断方式接口电路的基本组成

如图

4. I/O中断处理过程

1. CPU响应中断的条件和时间

1. 条件

- 允许中断触发器 EINT = 1 该触发器值修改方案如下:

- 用 开中断 指令将EINT置为 1

- 用 关中断 指令将EINT置为 0 或硬件 自动复位

2. 时间

- 当 D = 1 D=1 D=1 且 M A S K = 0 MASK = 0 MASK=0 时

外部设备完成准备后,就着手发出中断请求,但CPU不是时刻可以处理中断请求的。因此,在CPU无法处理中断请求之时,就设置 M A S K = 1 MASK = 1 MASK=1,使外部设备无法发出中断请求。

计算机的一般设计中,CPU会在每条指令的执行阶段结束后,发出中断查询信号,判断是否有中断请求

2. I/O中断处理过程

工作流程分析 参照 程序查询方式的接口电路、排队器、各触发器及其标记的状态 自行分析

需要注意:这里 非门 框中标记的 1代表非门的输出信号为1

这里仅对⑦⑧进行介绍,其他自行分析。

- 排队器电路产生输出信号(输出信号为 一个1和多个0的组合)

- CPU发出中断响应信号,然后设备编码器产生向量地址,通过数据线传递给CPU

- CPU利用向量地址取出中断服务程序入口地址或跳转指令

5. 中断服务程序流程

1. 中断服务程序的流程

中断服务程序的流程包括以下四个部分:

- 保护现场

- 程序断点的保护 中断隐指令完成

- 寄存器内容的保护 进栈指令完成

- 中断服务:对不同的 I/O 设备具有不同内容的设备服务

- 恢复现场:出栈指令完成

- 中断返回:中断返回指令

2. 单重中断和多重中断

- 单重中断:不允许中断 现行的 中断服务程序

- 多重中断:允许级别更高 的中断源 中断 现行的 中断服务程序

3. 单重中断和多重中断服务程序流程对比

关于开中断和关中断

- 单重中断:在中断服务程序执行完成并恢复断点后,才执行开中断,因此在中断服务程序执行过程中,不会出现嵌套中断

- 多重中断:在断点保护后就执行了开中断,此时若有更高优先级的中断服务程序出现,就会中断当前正在执行的中断服务程序

4. 主程序和服务程序抢占CPU示意图

[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-Cl0swOW5-1651755472895)(D:/%E5%A4%A7%E5%AD%A6%E8%B5%84%E6%96%99/%E8%AE%A1%E7%AE%97%E6%9C%BA%E7%BB%84%E6%88%90%E5%8E%9F%E7%90%86/img/%E4%B8%BB%E7%A8%8B%E5%BA%8F%E5%92%8C%E6%9C%8D%E5%8A%A1%E7%A8%8B%E5%BA%8F%E6%8A%A2%E5%8D%A0CPU%E7%A4%BA%E6%84%8F%E5%9B%BE.png)]

- 宏观 上 CPU 和 I/O 并行 工作

- 微观 上 CPU 中断现行程序 为 I/O 服务

六、DMA方式

1. DMA方式的特点

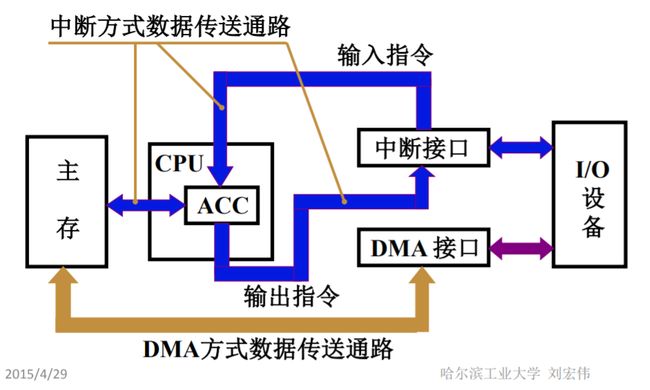

1. DMA和程序中断两种方式的数据通路

图示

区别:程序中断方式中主存和外部设备交换信息需要CPU的参与(虽然不是全程参与),而DMA方式不需要CPU的参与

2. DMA 与主存交换数据的三种方式

1. 停置CPU访问主存

CPU让出总线使用权和主存访问权,交给DMA。DMA控制外部设备和主存进行信息传输,此时CPU的工作状态可能是:

- CPU缓存中有预读指令,CPU继续工作

- CPU缓存中无预读指令,CPU处于不工作状态或保持状态

示意图

- 优点:控制简单

- 缺点:未充分发挥CPU对主存的利用率

2. 周期挪用(周期窃取)

周期挪用回顾

DMA访问主存有三种可能:

- CPU没有访问主存:DMA直接获取主存访问权

- CPU正在访问主存:DMA等待CPU访问完成

- CPU和DMA同时请求访存:此时 CPU 将总线控制权、主存访问权让给 DMA

示意图

3. DMA与CPU交替访问

将CPU工作周期拆分成两个部分:

- C 1 C_1 C1 专供DMA访存

- C 2 C_2 C2 专供CPU访存

示意图

优点:不需要申请建立和归还总线的使用权

2. DMA接口的功能和组成

接口的功能决定了接口的组成

1. DMA接口的功能

- 向CPU申请DMA传送

- 处理总线控制权的转交

- 管理系统总线、控制数据传送

- 确定数据传送的首地址和长度。

- 修正传送过程中的数据地址和长度

- DMA传送结束时,给出操作完成信号

2. DMA接口的组成

3. DMA的工作过程

1. 传送过程

1. 预处理

通过几条输入输出指令预置如下信息:

- 通知DMA控制逻辑传送方向(入/出)

- 设备地址——> DMA的DAR

- 主存地址——> DMA的AR

- 传送字数——> MA的WC

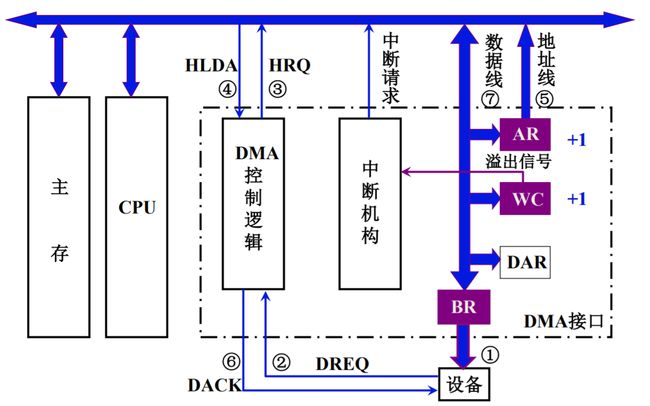

2. DMA传送过程示意

3. 数据传送过程(输入)

过程分析

- ①:设备将数据送入数据缓冲寄存器BR

- ②:设备向DMA控制逻辑发出申请信号DREQ

- ③:DMA控制逻辑向CPU请求DMA服务,发出总线使用权的请求信号HRQ

- ④:CPU在允许的情况下给出应答信号HLDA,放弃总线使用权和主存的访问权

- ⑤:主存地址寄存器AR将数据在主存中的首地址送到主存地址寄存器

- ⑥:DMA控制逻辑给出设备应答信号DACK,通知设备已经被授予一个DMA周期

- ⑦:BR中的数据经数据线传输给主存,在这个过程中,每传输一个字: A R + 1 , W C + 1 AR + 1, WC + 1 AR+1,WC+1,同时判断是否传输完成,未完成就继续。从步骤 1 开始

- ⑧:计数器溢出时(全0),表示一批数据交换完毕,WC向中断机构发出溢出信号,(INTR被置为1)中断机构向CPU发出中断请求信号。CPU响应中断请求后,通过执行中断服务程序来进行后处理

4. 数据传送过程(输出)

和输出的区别在于①、⑦

- ①:BR中的数据写入外部设备。此时BR已经空了,外部设备会在第②步发出DREQ信号

- ⑦:主存中的数据,在DMA控制下经数据线写入BR

5. 后处理

后处理处理的工作有:

- 校验送入主存的数据是否正确

- 判断是否继续用DMA

- 测试传送过程是否正确,错则转诊断程序

这些工作由CPU执行中断服务程序来完成

2. DMA接口与系统的连接方式

1. 具有公共请求线的DMA请求

如图

特点如下:

- 共享一条DMA请求线

- 越靠近CPU的DMA接口,优先级越高

- CPU通过DMA响应线进行链式的查询

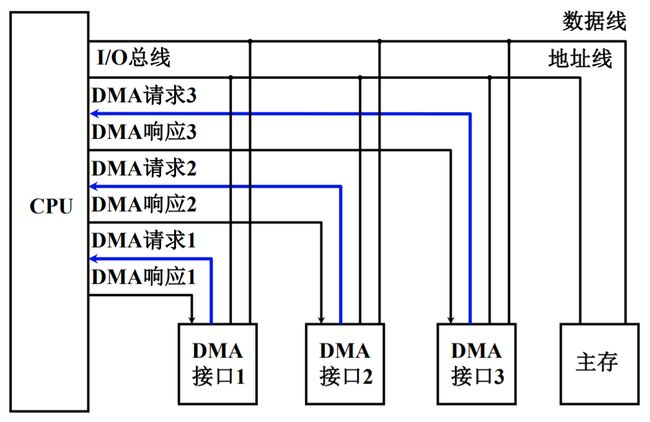

2. 独立的DMA请求

特点:

- 每个DMA接口有自己独立的请求线和响应线

- DMA请求的优先级排序在CPU中实现

3. DMA方式与程序中断方式的比较

| 比较项目 | 中断方式 | DMA方式 |

|---|---|---|

| 数据传送 | 程序,需CPU参与 | 硬件,不需要CPU参与 |

| 响应时间 | 指令执行结束 | 存取周期结束 |

| 处理异常情况 | 能 | 不能 |

| 中断请求目的 | 传送数据 | 后处理 |

| 优先级 | 低 | 高 |

4. DMA接口的类型

1. 选择型

如图

特点:

- 物理上:DMA接口连接了多个外部设备

- 逻辑上:只允许连接一个设备,不支持连接多个设备同时工作。(只有当一个设备传输完成后,才能连接另一个设备)

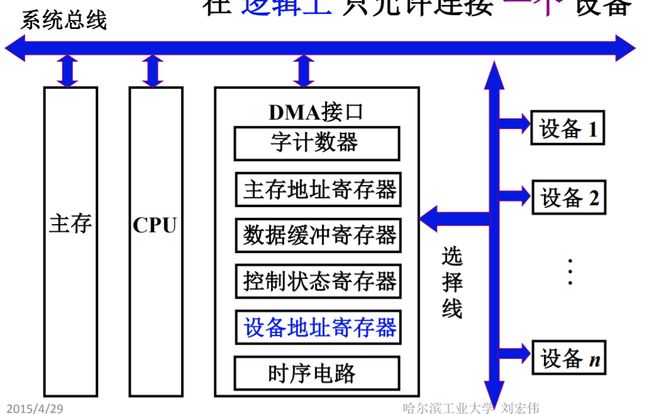

2. 多路型

如图 每个子通道就是一个小型的DMA处理器

特点:

- 物理上:连接多个设备

- 逻辑上:允许连接多个设备同时工作

3. 多路型 DMA 接口的工作原理

如图

补充知识

1. 部分逻辑电路符号

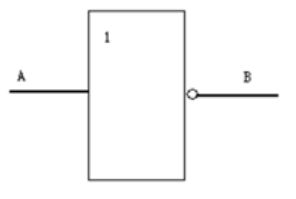

1. 非门

输入与输出

| 到达非门前(即A) | 通过非门后(即B) |

|---|---|

| 1 | 0 |

| 0 | 1 |

2. 与非门

输入与输出

| A | B | Y |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |