GPIO内部结构和各种模式

目录

前言1

前言2

1.GPIO的结构:

1.1 Push-Pull结构(推挽):

1.2 Open-Drain结构(开漏):

2.GPIO的八种工作模式

1、4种输入模式

2、4种输出模式

3、可配置3种最大翻转速度

4、八种工作方式讲解

1、GPIO输入工作模式---输入浮空模式

2、GPIO输入工作模式---输入上拉模式

3、GPIO输入工作模式---输入下拉模式

4、GPIO输入工作模式---输入模拟模式

5、GPIO输出工作模式---开漏输出模式

6、GPIO输出工作模式----开漏复用输出模式

7、GPIO输出工作模式3-推挽输出模式

8、GPIO输出工作模式4-复用推挽输出模式

参考

前言1

读了该篇文章可以知道:

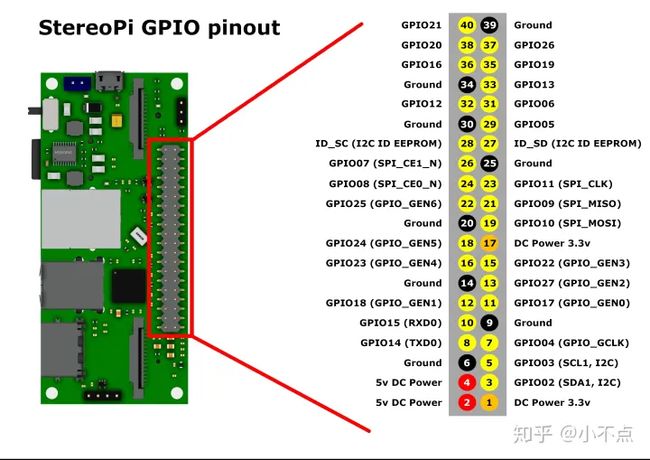

1.gpio可以直接用cpu通过寄存器控制读写

2.可以直接与片内外设连接 受外设控制(I2C)

3.gpio的push-pull和OD/OC结构

4.上下拉在输入输出的使用

5.斯密特触发器的作用:去信号抖动

6.gpio的4种输入和4种输出模式

还可以参考以下文章:

GPIO输入输出各种模式(推挽、开漏、准双向端口)详解_cy413026的博客-CSDN博客能将处理器的GPIO(General Purpose Input and Output)内部结构和各种模式彻底弄清楚的人并不多,最近在百度上搜索了大量关于这部分的资料,对于其中很多问题的说法并不统一。本文尽可能的将IO涉及到的所有问题罗列出来,对于有明确答案的问题解释清楚,对于还存在疑问的地方也将问题提出,供大家讨论。概括地说,IO的功能模式大致可以分为输入、输出以及输入输出双向三大类。其中作为基本输入IO,相对比较简单,主要涉及的知识点就是高阻态;https://blog.csdn.net/cy413026/article/details/128423927

【STM32】GPIO工作原理(八种工作方式超详细分析,附电路图)_Yngz_Miao的博客-CSDN博客STM32F1xx官方资料:《STM32中文参考手册V10》-第8章通用和复用功能IO(GPIO和AFIO ) 芯片数据手册(datasheet) STM32的GPIO介绍STM32引脚说明GPIO是通用输入/输出端口的简称,是STM32可控制的引脚。GPIO的引脚与外部硬件设备连接,可实现与外部通讯、控制外部硬件或者采集外部硬件数据的功能。STM32F103ZET6芯片..._1671465600https://blog.csdn.net/qq_38410730/article/details/79858906

电路中上拉、下拉电阻的作用及原理_cy413026的博客-CSDN博客假定芯片的供电电压为3.3V(忽略晶体管饱和压降),则输出最大电流25mA时,负载RL的值约为132欧姆(3.3V/25mA),如果负载值小于132欧姆,则相应输出电流会更大(超过25mA),但是芯片引脚只能提供最大25mA的电流,因此,输出电平将会下降(老板你只给我2500月薪,我就只能干2500的活,你要我干更多的活得开更多的工资,一个道理)需要使用上拉电阻还是下拉电阻,主要取决于电路系统本身的需要,比如,对于高有效的使能控制信号(EN),我们希望电路系统在上电后应处于无效状态,则会使用下拉电阻。https://blog.csdn.net/cy413026/article/details/128423790

前言2

据说能将处理器的GPIO(General Purpose Input and Output)内部结构和各种模式彻底弄清楚的人并不多?那现在就让多一点

GPIO的功能,简单说就是可以根据自己的需要去配置为输入或输出。但是在配置GPIO管脚的时候,常会见到两种模式:开漏(open-drain,漏极开路)和推挽(push-pull)。

1.GPIO的结构:

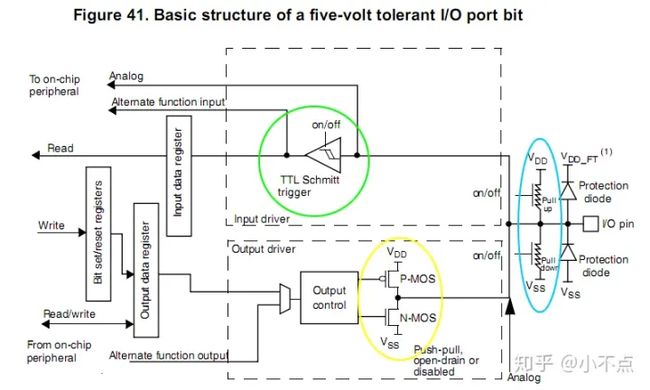

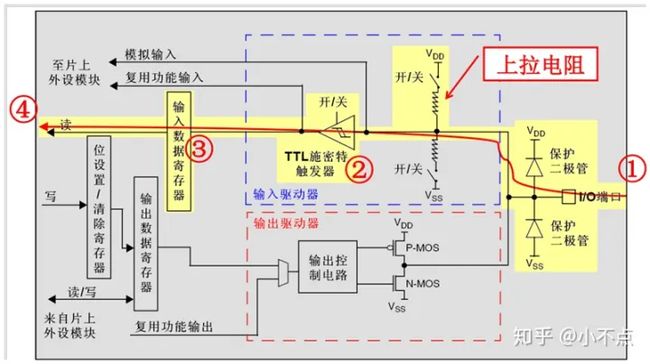

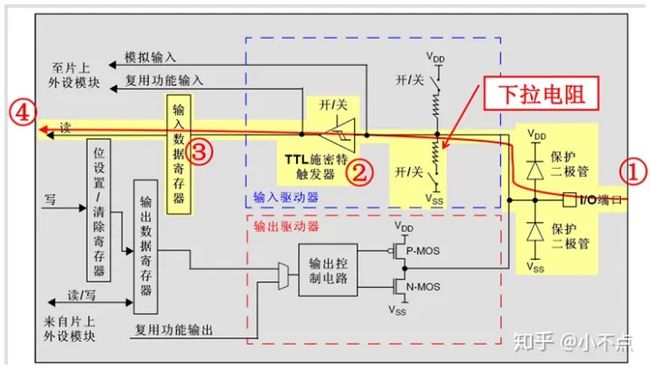

首先,了解GPIO结构里面的三个重要组成部分,如下图所示

- 上拉以及下拉电阻(pull-up and pull-down resistors):上下拉电阻的作用就是将浮空管脚拉到一个固定的状态(0或者1),上拉电阻将浮空管脚上拉至VDD,下拉电阻将浮空管脚下拉至GND。

- 施密特触发器(Schmitt trigger ):信号经过施密特触发器之后,模拟信号转换为数字信号0和1。

- PMOS和NMOS(p-mos and n-mos transistors 决定了电路工作在开漏输出模式或者是推挽输出模式),可以配置为OD,push-pull和两管子都高阻

1.1 Push-Pull结构(推挽):

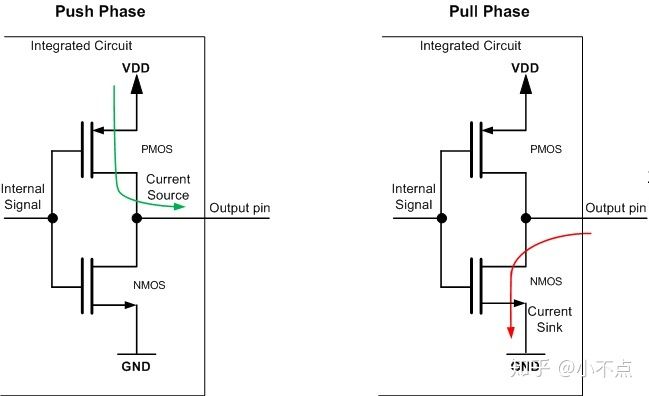

顾名思义,PUSH-PULL中所谓PUSH指的是把输出推到电路的VDD电压,所谓Pull指的是将输出拉到Ground电压。

Simplified schematic of a push-pull output

如上图所示,可以看出是由一对PMOS和NMOS组成了一个简单的Push-Pull结构,具体的原理如下:

- Push phase – 当连接在Mos管栅极的internal信号输入为低电平(Logic 0)的时候,PMOS管导通,电流从VDD流经PMOS管至输出端口。

- Pull phase – 当连接在Mos管栅极的internal信号输入为高电平(Logic 1)的时候,NMOS管导通,电流从Output端流经PMOS管至GND。

1.2 Open-Drain结构(开漏):

如图所示,可以看出开漏输出电路是由一个N沟道MOS管组成的,当NMO管导通时,电路通过NMOS管将输出拉低至GND;当NMOS管关闭时,电路输出管脚浮空。

Schematic of an open drain output

开漏输出电路一般用于通信接口,该通信接口下同时挂着n多个devices(比如I2C结构),如上图所示,当Internal signal信号输入高电平的情况下,NMOS管导通,输出被拉低到低电平状态;当Internal signal信号输入低电平的情况下,NMOS管截至,输出高阻态(高阻态、三态、浮空都表示一个意思),此时电路对外没有展示出任何驱动能力,此时可以在外部接一个上拉电阻来实现输出高电平。

- 开漏输出的这一特性一个明显的优势就是可以很方便的调节输出的电平,因为输出电平完全由上拉电阻连接的电源电平决定。所以在需要进行电平转换的地方,非常适合使用开漏输出。

- 开漏输出的这一特性另一个好处在于可以实现"线与"功能,所谓的"线与"指的是多个信号线直接连接在一起,只有当所有信号全部为高电平时,合在一起的总线为高电平;只要有任意一个或者多个信号为低电平,则总线为低电平。而推挽输出就不行,如果高电平和低电平连在一起,会出现电流倒灌,损坏器件。

高电平驱动能力低电平驱动能力电平跳变速度线与功能电平转换推挽输出强强快不支持不支持开漏输出由外部上拉电阻提供强由外部上拉电阻决定,电阻越小反应速度越快功耗越大支持支持推挽输出开漏输出高电平驱动能力强由外部上拉电阻提供低电平驱动能力强强电平跳变速度快由外部上拉电阻决定,电阻越小反应速度越快功耗越大线与功能不支持支持电平转换不支持支持

【open-drain和push-pull的总结】

对于GPIO的模式的设置,在不考虑是否需要额外的上拉电阻的情况下,是设置为open-drain还是push-pull,说到底,还是个权衡的问题:

如果你想要电平转换速度快的话,那么就选push-pull,但是缺点是功耗相对会大些。

如果你想要功耗低,且同时具有“线与”的功能,那么就用open-drain的模式。(同时注意GPIO硬件模块内部是否有上拉电阻,如果没有,需要硬件电路上添加额外的上拉电阻)[1]

2.GPIO的八种工作模式

1、4种输入模式

输入浮空、输入上拉、输入下拉、模拟输入

2、4种输出模式

开漏输出、开漏复用功能、推挽输出、推挽复用功能

3、可配置3种最大翻转速度

2MHz

10MHz

50MHz

4、八种工作方式讲解

1、GPIO输入工作模式---输入浮空模式

浮空输入模式下,I/O端口的电平信号直接进入输入数据寄存器。

详细的说:

(1)首先,外部电路通过I/O端口输入电平,外部电平通过上下拉部分(浮空模式下都关闭,既无上拉也无下拉电阻)传输到施密特触发器(此时施密特触发器为打开状态)

(2)外部电平在经过施密特触发器之后继续传输到输入数据寄存器IDR(Input Data Register)

(3)CPU通过读输入数据寄存器实现读取外部输入电平值的目标,I/O的电平状态是不确定的,完全由外部输入决定;如果在该引脚悬空(在无信号输入)的情况下,读取该端口的电平是不确定的。

2、GPIO输入工作模式---输入上拉模式

上拉输入模式下,I/O端口的电平信号直接进入输入数据寄存器。

和输入浮空模式相比较,外部输入通过上拉电阻,施密特触发器存入输入数据寄存器IDR,被CPU读取。但是不同之处在于:

(1)内部有一个上拉电阻连接到VDD(输入上拉模式下,上拉电阻开关接通,阻值约30-50K)

(2)但是在I/O端口悬空(在无信号输入)的情况下,输入端的电平可以保持在高电平;并且在I/O端口输入为高电平的时候,输入端的电平也还是高电平。

对于此种输入方式,无论输入管脚悬空或者被高电平驱动时,读取的都是1。只有在输入端为0的时候,读取到的值才是0。因此采取的时非0输入模式。即若读取非0,即为1,若读取为0,即为0 [2]。

3、GPIO输入工作模式---输入下拉模式

上拉输入模式下,I/O端口的电平信号直接进入输入数据寄存器。

和输入浮空模式相比较,外部输入通过下拉电阻,施密特触发器存入输入数据寄存器IDR,被CPU读取。但是不同之处在于:

(1)内部有一个下拉电阻连接到VSS(输入下拉模式下,下拉电阻开关接通,阻值约30-50K)

(2)但是在I/O端口悬空(在无信号输入)的情况下,输入端的电平可以保持在低电平;并且在I/O端口输入为低电平的时候,输入端的电平也还是低电平。

但是该电路对外呈现的不是高阻,某种意义上说也在向外输出,当外部驱动电路不同时可能出现错误的检测结果 [2]。

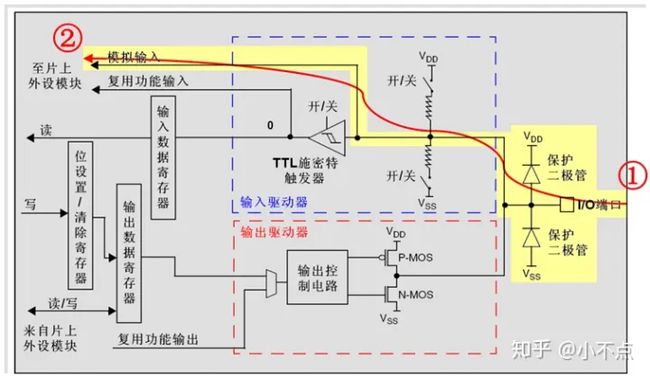

4、GPIO输入工作模式---输入模拟模式

上拉和下拉部分均为关闭状态(AD转换-模拟量转换为数字量),施密特触发器为截止状态,I/O端口的模拟信号直接通过模拟输入通道输入到CPU,IO口外部电压为模拟量(电压形式非电平形式),作为模拟输入范围一般为0~3.3V

5、GPIO输出工作模式---开漏输出模式

开漏输出模式下,通过设置位设置/清除寄存器或者输出数据寄存器的值,途经N-MOS管,最终输出到I/O端口。(这里只经过N-MOS管,P-MOS管是被输出控制电路接死为截至状态)

具体过程如下:

CPU写入位设置/清楚寄存器BSRR,映射到输出数据寄存器ODR,联通到输出控制电路(也就是ODR的电平),ODR电平通过输出控制电路进入N-MOS管。

(1)-ODR输出1:

- N-MOS截止,IO端口电平不会由ODR输出决定,而由外部上拉/下拉决定

- 在输出状态下,输出的电平可以被读取,数据存入输入数据寄存器,由CPU读取,实现CPU读取输出电平;所以,当N-MOS截止时,如果读取到输出电平为1,不一定是我们输出的1,有可能是外部上拉产生的1

(2)-ODR输出0:

- N-MOS开启,IO端口电平被N-MOS管拉低至VSS,使IO输出低电平,此时输出的低电平同样可以被CPU读取到

6、GPIO输出工作模式----开漏复用输出模式

开漏复用输出模式,与开漏输出模式很是类似。只是输出的高低电平的来源,不是让CPU直接写输出数据寄存器,取而代之利用片上外设模块的复用功能输出来决定的。

与开漏输出模式唯一的区别在于输出控制电路电平的来源

- 开漏输出模式的输出电平是由CPU写入输出数据寄存器控制的

- 开漏推挽输出模式的输出电平是由复用功能外设输出决定的

- 其他与开漏输出模式相似:

- 控制电路输出为1:N-MOS截止,IO口电平由外部上拉/下拉决定

- 控制电路输出为0:N-MOS开启,IO口输出低电平

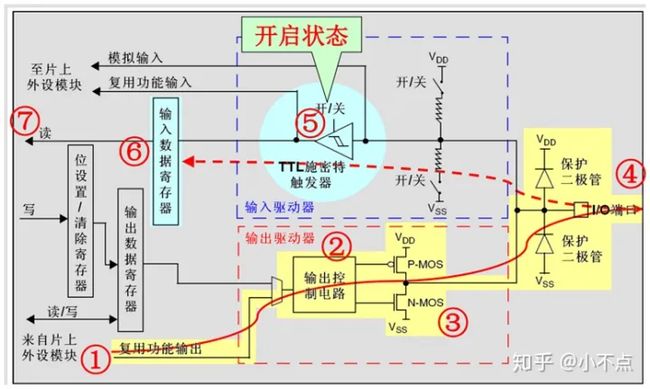

7、GPIO输出工作模式3-推挽输出模式

与开漏输出相比较,输出控制寄存器部分相同,输出驱动器部分加入了P-MOS管部分

(1)当输出控制电路输出1时:

P-MOS管导通N-MOS管截止,被上拉到高电平,IO口输出为高电平1

(2)当输出控制电路输出0时:

- P-MOS管截止N-MOS管导通,被下拉到低电平,IO口输出为低电平0

- 同时IO口输出的电平可以通过输入电路读取

8、GPIO输出工作模式4-复用推挽输出模式

与推挽输出模式唯一的区别在于输出控制电路之前电平的来源

- 开漏输出模式的输出电平是由CPU写入输出数据寄存器控制的

- 开漏推挽输出模式的输出电平是由复用功能外设输出决定的

参考

- ^高阻、三态、浮空三种说法代表同一个意思