CC2420芯片手册核心知识点

目录

- 1. 引脚分配

- 2. 电路描述

- 3. 应用电路

-

- 3.1 输入/输出匹配

- 3.2 偏置电阻

- 3.3 晶振

- 3.4 稳压器

- 3.5 电源退耦器

- 4. IEEE802.15.4的调制格式

- 5. 配置模式概述

- 6. 四线串行配置和数据接口

-

- 6.1 引脚配置

- 6.2 寄存器的访问

- 6.3 状态字节

- 6.4 命令选通

- 6.5 访问RAM

- 6.6 FIFO访问

- 6.7 连续SPI访问

- 7. 微控制接口和引脚描述

-

- 7.1 配置接口

- 7.2 接收模式

- 7.3 RXFIFO溢出

- 7.4 发送模式

- 7.5 总体控制和状态引脚

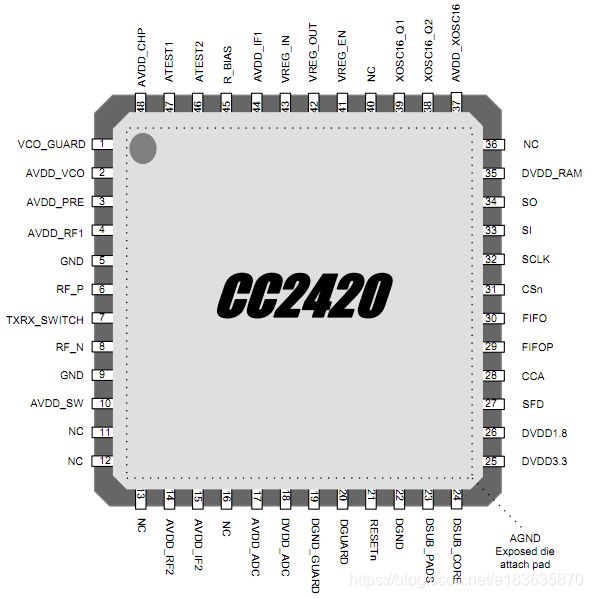

1. 引脚分配

| 引脚 | 引脚名 | 引脚类型 | 引脚描述 | 引脚描述 |

| - | AGND | Ground (analog) | Exposed die attach pad. Must be connected to solid ground plane | 外露的模具连接垫。必须连接到实心接地板上 |

| 1 | VCO_GUARD | Power (analog) | Connection of quard ring for VCO (to AVDD) shielding | 连接方形环,用来VCO屏蔽 |

| 2 | AVDD_VCO | Power (analog) | 1.8 V Power supply for VCO | 压控振荡器VCO 1.8V供电 |

| 3 | AVDD_PRE | Power (analog) | 1.8 V Power supply for Prescaler | 分频器 1.8V供电 |

| 4 | AVDD_RF1 | Power (analog) | 1.8 V Power supply for RF front-end | 射频前端 1.8V供电 |

| 5 | GND | Ground (analog) | Grounded pin for RF shielding | RF屏蔽接地引脚 |

| 6 | RF_P | RF I/O | Positive RF input/output signal to LNA/from PA in receive/transmit mode | 正射频输入/输出信号到LNA/from PA 在接收/发射模式 |

| 7 | TXRX_SWITCH | Power (analog) | Common supply connection for integrated RF front-end. Must be connected to RF P and RF N externally through a DC path | 集成射频前端的通用电源。必须通过直流路径连接到RF P和RF N |

| 8 | RF_N | RF I/O | Negative RF input/outout sianal to LNA/from PA in receive/transmit mode | 负射频输入/输出信号到LNA/from PA 在接收/发射模式 |

| 9 | GND | Ground (analog) | Grounded pin for RF shielding | 射频屏蔽接地引脚 |

| 10 | AVDD_SW | Power (analog) | 1.8 V Power supply for LNA /PA switch | LNA /PA 1.8V供电 |

| 11 | NC | - | Not Connected | 未连接 |

| 12 | NC | - | Not Connected | 未连接 |

| 13 | NC | - | Not Connected | 未连接 |

| 14 | AVDD_RF2 | Power (analog) | 1.8 V Power supply for receive and transmit mixers | 1.8V供电 |

| 15 | AVDD_IF2 | Power (analog) | 1.8 V Power supply for transmit / receive IF chain | 1.8V供电 |

| 16 | NC | - | Not Connected | 未连接 |

| 17 | AVDD_ADC | Power (analog) | 1.8 V Power supply for analog parts of ADCs and DACs | 为模拟ADC和DAC模块提供1.8V电源电压 |

| 18 | DVDD_ADC | Power (digital) | 1.8 V Power supply for diaital parts of receive ADCs | 为数字ADC数字接收模块提供1.8V电源 |

| 19 | DGND_GUARD | Ground (digital) | Ground connection for digital noise isolation | 接地,隔离数字信号噪声 |

| 20 | DGUARD | Power (digital) | 1.8 V Power supply connection for digital noise isolation | 隔离数字信号噪声 1.8V供电 |

| 21 | RESETn | Digital Input | Asynchronous, active low digital reset | 异步,低电平有效 数字复位 |

| 22 | DGND | Ground (digital) | Ground connection for digital core and pads | 数字磁芯和电垫接地 |

| 23 | DSUB_PADS | Ground (digital) | Substrate connection for digital pads | 数字焊盘的基片连接 |

| 24 | DSUB_CORE | Ground (digital) | Substrate connection for digital modules | 数字模块的基片连接 |

| 25 | DVDD3.3 | Power (digital) | 3.3 V Power supply for digital I/Os | I/Os 3.3V供电 |

| 26 | DVDD1.8 | Power (digital) | 1.8 V Power supply for digital core | 1.8V 芯片工作电压供电 |

| 27 | SFD | Digital output | SFD (Start of Frame Delimiter) / digital mux output | SFD(帧分隔符的开始)/数字mux输出 |

| 28 | CCA | Digital output | CCA (Clear Channel Assessment) / digital mux output | CCA(空闲信道评估)/数字mux输出 |

| 29 | FIFOP | Digital output | Active when number of bytes in FIFO exceeds threshold / serial RF clock output in test mode | 在测试模式下FIFO中的字节数超过了串行射频时钟输出的阈值激活 |

| 30 | FIFO | Digital I/O | Active when data in FIFO / serial RF data input / output in test mode | 在测试模式下FIFO /串行射频数据输入/输出时激活 |

| 31 | CSn | Digital input | SPI Chip select, active low | SPI片选 低电平有效 |

| 32 | SCLK | Digital input | SPI Clock input, up to 10 MHz | SPI时钟输入 高达10MHz |

| 33 | SI | Digital input | SPI Slave Input. Sampled on the positive edge of SCLK | SPI从机输入 在SCLK的上升沿采样 |

| 34 | SO | Digital output (tristate) | SPI Slave Output. Updated on the negative edge of SCLK. Tristate when CSn high. | SPI从机输出 在SCLK的下降沿更新,CSn高电平时高组态 |

| 35 | DVDD_RAM | Power (digital) | 1.8 V Power supply for digital RAM | 数字RAM供电1.8 V |

| 36 | NC | - | Not Connected | 未连接 |

| 37 | AVDD_XOSC16 | Power (analog) | 1.8 V crystal oscillator power supply | 1.8 V晶振电源 |

| 38 | XOSC16_Q2 | Analog I/O | 16 MHz Crystal oscillator pin 2 | 16MHz晶体振荡器引脚2 |

| 39 | XOSC16_Q1 | Analog I/O | 16 MHz Crystal oscillator pin 1 or external clock input | 16MHz晶体振荡器引脚1或外部时钟输入 |

| 40 | NC | - | Not Connected | 未连接 |

| 41 | VREG_EN | Digital input | Voltage regulator enable, active high, held at VREG_IN voltage level when active.Note that VREG_EN is relative VREG_IN,not DVDD3.3 | 电压调整器使能,高电平有效,激活时保持VREG_IN电压电平。注意VREG_EN是相对于VREG_IN,而不是3.3V |

| 42 | VREG_OUT | Power output | Voltage regulator 1.8 V power supply output | 电压调节器1.8 V电源输出 |

| 43 | VREG_IN | Power (analog) | Voltage regulator 2.1 to 3.6 V power supply input | 电压调压器2.1到3.6 V电源输入 |

| 44 | AVDD_IF1 | Power (analog) | 1.8 V Power supply for transmit / receive IF chain | 发射/接收IF链的1.8 V电源 |

| 45 | R_BIAS | Analog output | External precision resistor, 43 kΩ, ±1 % | 外部精密电阻、43 kΩ±1% |

| 46 | ATEST2 | Analog I/O | Analog test I/O for prototype and production testing | 用于原型和生产测试的模拟测试I/O |

| 47 | ATEST1 | Analog I/O | Analog test I/O for prototype and production testing | 用于原型和生产测试的模拟测试I/O |

| 48 | AVDD_CHP | Power (analog) | 1.8 V Power supply for phase detector and charge pump | 相位检测器和电荷泵 1.8V供电 |

2. 电路描述

CC2420的简化框图如图所示,它是一款中低频接收器。接收到的射频信号首先被一个低噪放大器(LNA)放大,并把同相正交信号下变频到中频(2MHz),接着复合的同相正交信号被滤波放大,再通过AD转换器转换成数字信号,其中自动增益控制、最后的信道滤波、扩频、相关标志位、同步字节都是以数字的方法实现的。

当SFD引脚变高的时候,标志着一个起始帧的标识符已经被发现。CC2420把收到的数据存放到一个128字节的FIFO接收单元,使用者可以通过SPI接口读取FIFO中的数据,并且通过硬件完成CRC效验,接收信号的强度指示和相关的评测都被添加到帧里面。在接收模式下CCA可以通过一个引脚来获得;在测试的时候,它还提供一个无缓冲的串行数据模式。

CC2420通过直接上转换来完成发送,待发送的数据存在一个128字节的FIFO发送单元(与FIFO接收单元相互独立)中,其中帧头和帧标识符由硬件自动添加上去。按照IEEE802.15.4中的扩展顺序,每一个字符(4bits)都被扩展成32个码片,并被送到数模转换器以模拟信号的方式输出。

一个模拟低通滤波器把信号传递到积分(quadrature)上变频混频器,得到的射频信号被功率放大器(PA)放大,并被送到天线匹配。

内部的发送接收选择开关电路使天线连接和匹配更加容易,但是射频线路是差分的,所以终端天线经常通过一个不平衡变压器来匹配。通过一个外部直流通道把TXRX_SWITCH引脚连接到RF-P引脚和RF-N引脚来为低噪声放大器和功率放大器提供偏置电压。

CC2420中的频率合成器包含一个完整的片上LC压控振荡器,其中一个90度的相位分离器用来产生同相和正交相的本地振荡信号,用来为接收模式的下变频混合器以及发送模式的上变频混合器提供原始信号。压控振荡器(VCO)工作在4800 –4966 MHz频率段,但是当分离器产生了同相和正交相的时候,这个频率就会被二分频。

一个外部晶振必须连接到XOSC16_Q1和XOSC16_Q2引脚,以用来为合成器提供参考频率。锁相环(PLL)可提供数字锁定信号。

数字基带包括支持帧处理,地址识别,数据缓存和MAC的安全机制。其中4线的SPI被用来实现配置和数据缓存,一个片上的稳压器用来提供标准的1.8V电压,同时这个稳压器还可以通过一个单独的引脚来使能。一个电源监控器被用来检测那些非正常的供电电压,并且这个监控器可以通过SPI来配置。

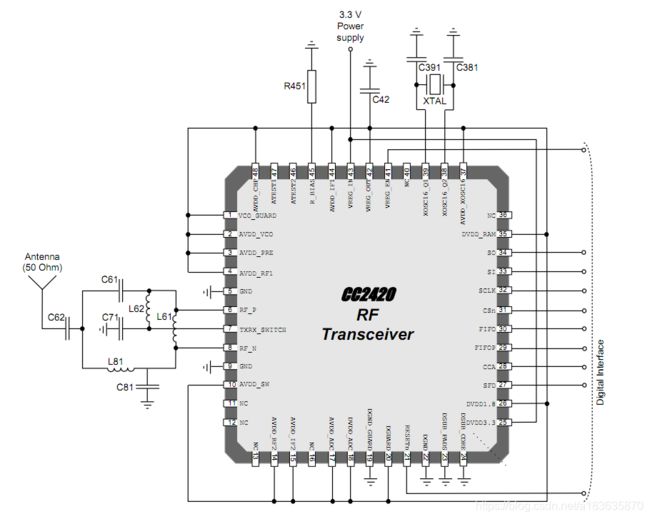

3. 应用电路

CC2420只需外接很少的外部电路即可构成应用系统。一个典型的应用电路如图所示。外接元件的说明见表1,参数典型值见表2。

3.1 输入/输出匹配

射频输入/输出是差分和高阻抗的。射频端口最适宜的差分负载值阻抗为95+j187Ω。

如果使用非平衡的天线,例如单极天线,必须使用非平衡变压器来增强其性能。非平衡变压器可以使用低成本的分立电感和电容或者再外接一个传送天线来构成。

3.2 偏置电阻

偏置电阻R451用来设置精确的偏置电流。

3.3 晶振

外部晶振的负载电容为C381和C391。

3.4 稳压器

片内稳压器提供所有的1.8V输入电压。C42用来增强稳压器的稳定性。为了满足ESR的要求需要使用一系列的电阻。

3.5 电源退耦器

为了提高电路性能必须使用合适的电源退耦器(decoupling)。在一个应用系统中,为了使电路性能达到最佳,电源退耦器的布置、退耦电容的大小以及电源滤波至关重要。Chipcon提供了一个紧凑的参考设计。

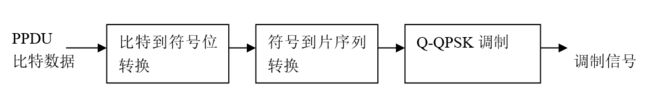

4. IEEE802.15.4的调制格式

本节对IEEE802.15.4 协议中的2.4GHz直接序列扩频(DSSS)射频调制帧格式作简单介绍。调制和扩频的功能框图见图:

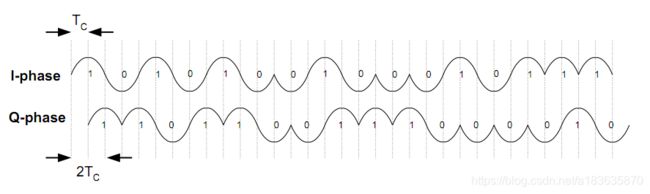

CC2420先将要传送的数据流进行变换,首先每一个字节被分成两个字符,每个字符包含4bits,最低有效字符先传送(LSS)。除了在完全相关的领域是先传送最高有效字节(MSB)外,其他的多字节传送领域都是最低有效字节(LSB)优先传送。每个字符都被映射成一个32位码片的伪随机数,如表所示。这样的伪随机数一共有16个,它们互不相同。经过转换后,码片序列的传输速率可达2MChips/s,传送先从最低有效位C0开始。此码片序列经过O-QPSK调制后,每个码片被调制成半个正弦波。码片流通过I/Q通道交替传输,两通道之间的传输延时为半个码片周期。传送符号0的波形如图所示。

5. 配置模式概述

在不同的应用中,CC2420可通过配置达到最佳工作状态。通过配置可编程控制寄存器可以修改以下的一些关键参数:

- 接收/发送模式

- 射频信道选择

- 射频输出功率

- 掉电/上电模式

- 晶振掉电/上电

- 空闲信道评估模式

- 包操作硬件支持

- 加密/解密模式

6. 四线串行配置和数据接口

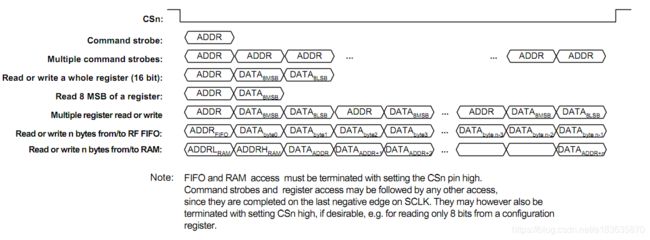

当CC2420处在从设备的时候,CC2420可以通过一个简单4线SPI接口(SI,SO,SCLK,CSN)来配置它的工作模式,并能实现读写数据缓存的功能。所有的地址和数据在SPI上传送时都是以MSB开始的。

6.1 引脚配置

数字输入引脚SCLK,SO,CSN应该配置成高阻输入,由于CC2420没有内部上拉电阻,所以必须在外部接上上拉电阻。虽然当 CSN是高的时候,SO是高阻抗的,但还是应该在SO引脚上加一个上拉电阻,以避免给微控制器带来抖动的输入。MCU上其他没有用到的I/O口应该设置成输出引脚,并把它们接到低电平,防止产生泄露电流。

6.2 寄存器的访问

CC2420内部有33个16位的配置和状态寄存器,15个命令寄存器,2个单独的8位寄存器分别用来访问发送和接收FIFO单元。这50个寄存器的地址通过6位的地址线来编址,当访问寄存器的时候,RAM/寄存器选择位必须被清0,读/写选择位选择一个读或者写操作,并且保证8位地址总线与6位寄存器地址线相互匹配。在寄存器的每一个读写周期中,SI总线上共有24比特数据,其中最先发送的是1bit的RAM/寄存器选择位(0:寄存器,1:RAM),接下来是1bit的读/写选择位(0:写,1:读),然后是6bits的地址线(从A5开始发送),最后才是16bits的数据线(丛D15开始发送),在整个传输过程中CSN引脚必须一直保持在低电平状态。通过同样的接口微控制器也可以对配置寄存器进行读操作。数据回读的时候,读/写选择位必须被置高以进行初始化,在选择好寄存器地址并且S0被控制器配置成它的数据输入脚后,控制器就可以在16个时钟周期内通过CC2420的输出脚S0从地址寄存器中读取数据。

在SCLK为上升沿的时候,SI上的数据被写入CC2420,当16bits数据的最低位D0也被写入的时候,整个字(一个字由两个字节构成)的数据被存放在CC2420的内部配置寄存器中。在不改变CSN的情况下多个寄存器可以被一次写入,在低功耗模式和休眠状态下,寄存器中的所有数据仍然不会丢失,直到供电电压关闭(例如:通过VREG_EN引脚使稳压电源关闭),寄存器的操作可以按照任何的顺序进行。

| 参数 | 符号 | 最小值 | 最大值 | 单位 | 条件 |

| SCLK 时钟频率 | Fsclk | 10 | MHZ | ||

| SCLK 低脉冲持续时间 | tcl | 25 | ns | SCLK必须保持低电平的最小时间 | |

| SCLK高脉冲持续时间 | tch | 25 | ns | SCLK必须保持高电平的最小时间 | |

| CSn 建立时间 | tsp | 25 | ns | 在第一个SCLK脉冲上升沿到来之前CS片选必须为低电平的最小时间 | |

| CSn 持续时间 | tns | 25 | ns | 在最后一个SCLK脉冲上升沿到来之后CS片选必须保持低电平的最小时间 | |

| SI 建立时间 | tsd | 25 | ns | 在SCLK脉冲上升沿到来之前SI的数据必须准备好的最小时间 | |

| SI 持续时间 | thd | 25 | ns | 在SCLK脉冲上升沿到来之后数据必须保持SI 线上的最小时间 | |

| 上升时间 | trise | 100 | ns | SCLK,CSn上升所用时间最大值 | |

| 下降时间 | tfall | 100 | ns | SCLK,CSn下降所用时间最大值 |

6.3 状态字节

CC2420在寄存器访问、命令选通(command strobes)、RAM首个地址或者数据字节传送到发送FIFO期间,SO引脚上将返回状态字节。状态字节包含有六个状态位,具体说明见下表,通过发出SNOP命令来读取状态字。也可以在芯片访问期间读取状态字,例如访问寄存器和FIFO期间。

| 命令位 | 名字 | 描述 |

|---|---|---|

| 7 | - | 保留 |

| 6 | XOSC16M_STABLE | 16M晶振工作指示位。0:16M晶振未工作 1:16M晶振在工作 |

| 5 | TX_UNDERFLOW | FIFO溢出指示位。此位需要使用SFLUSHTX命令手动清除。 0:未溢出 1:溢出 |

| 4 | ENC_BUSY | 加密模块忙指示位。0:加密模块空闲 1:加密模块忙 |

| 3 | TX_ACTIVE | RF传送器工作指示位。0:RF传送器空闲 1:RF传送器正在工作 |

| 2 | LOCK | 频率综合器PLL锁指示位。0:PLL未锁 1:PLL锁 |

| 1 | RSSI_VALID | RSSI值有效指示位。0:RSSI值无效 1:RSSI值有效,一般在接收开始至少8个符号传送时间后 |

| 0 | - | 保留 |

6.4 命令选通

命令选通(Command strobes)可以看作一个对CC2420的单字节的操作指令。访问一个命令寄存器的地址就会执行一个内部时序。这些命令用来使能晶振,使能接收模式,启动加密等。所有15个命令的资料下表

如果晶振未工作,则只有SXOSCON命令可以使用,其他的命令会全部无效。只有晶振稳定工作,其他命令才有效。访问命令寄存器的操作过程和访问其他寄存器一样,只是没有数据传输。也就是只有RAM/寄存器选通位(置为0),读/写选通位(置为0)和6位的地址位(从0x00到0x0E)被写入。一个命令将紧随一个未将CSn未置高的SPI访问进程,并且在下一个时钟的下降延被执行。

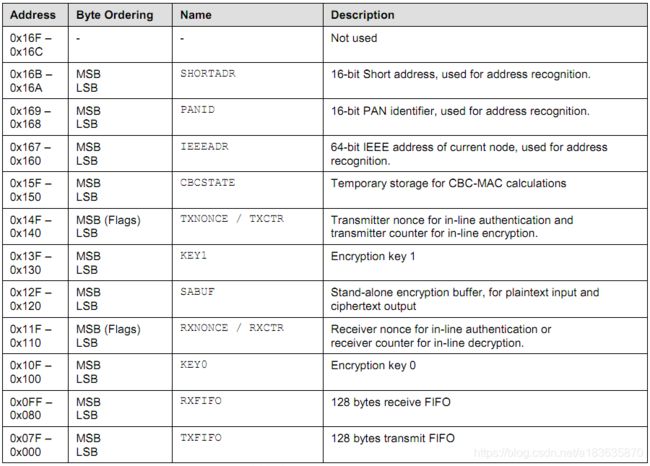

6.5 访问RAM

CC2420内部的368字节RAM可以通过SPI接口来访问。 通过传送2字节的地址可以一次读取单个或多个字节,然后由硬件自动将地址指向下一单元。每次只读或者写一个字节, 不像寄存器访问中每次读写2个字节。在访问RAM期间晶振必须工作。

通过将RAM/寄存器选通位置来使能对RAM的访问。9位的RAM地址由两部分组成。B1:0 (MSB)用来选通三个存储区的其中一个。A6:0 (LSB)用来选通该存储区的地址。RAM分成了三个存储区:发送FIFO(0区),接收FIFO(1区),安全区(2区)。每个FIFO有128字节, 而安全区有112字节。

A6:0紧随RAM/寄存器选通位传送,在开是传送数据之前还需要传送另外一个地址字节。这个字节包括第7位6位的B1:0,5位的读写选通位(0为读和写,1为读),4位到0位为无关位。

对于RAM写过程,数据将在第二个字节后直接从SI引脚读取并写入RAM,同时RAM的数据自动的从SO引脚上读出,但如果用户只对写感兴趣的话这个过程将被忽略。对于RAM读,被选通字节的数据将在第2个地址位传输完成后直接从SO引脚上读出。

下图显示了读取多个RAM字节数据的操作过程。 RAM存储器的空间分配见表6。低256字节数据用来存储FIFO数据。

和寄存器一样,数据在掉电模式下仍被保存在RAM中,但是如果电源被关闭,数据将被丢失。

6.6 FIFO访问

对发送FIFO和接收FIFO的访问是通过TXFIFO (0x3E) 和RXFIFO (0x3F)寄存器来实现的。

TXFIFO仅仅只用来写,但是也可以通过RAM访问来读取。在通过RAM访问中,每次只读和写一个字节。RXFIFO既可读也可写,写FIFO只有在调试或者执行安全操作(加密/解密)时才发生。在访问FIFO期间晶振必须工作。

在写TXFIFO时,每写一个新的字节SO引脚上都会输出状态字,如图9所示。这样就可以检测到在写TXFIFO是否有溢出。

多字节的FIFO数据可以通过RAM访问在一次操作中完成。在FIFO访问开始后只能通过将CSN拉高来中止FIFO操作。

FIFO和FIFOP两个引脚提供了接收FIFO中数据的额外信息,注意FIFO和FIFOP引脚信息只针对RXFIFO,TXFIFO有它自己的溢出状态标志。

可以使用SFLUSHTX命令来清空TXFIFO和RXFIFO。

6.7 连续SPI访问

在CSN引脚未被拉高时,寄存器访问,命令选通,FIFO访问和RAM访问可以连续执行。例如,用户可以在一个操作中执行命令选通、寄存器写、连续写3字节数据到TXFIFO,如图11所示。唯一不同的是FIFO和RAM访问必需通过将CSN拉高来中止。

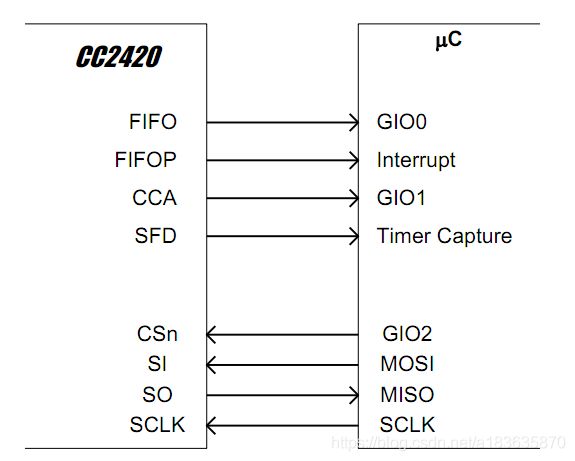

7. 微控制接口和引脚描述

在典型的应用中,CC2420将与微控制器相连接。该控制器必须能够:

设置CCC2420为不同的工作模式,读写缓存器数据,通过4位的SPI总线控制接口读写状态信息。(SI,SO,SCLK和CSn)

通过FIFO和FIFOP状态引脚连接接收和发送FIFO。

通过CCA引脚执行空闲信道评估。

通过SFD引脚获取时间信息(特别是在有信标的网络中)

7.1 配置接口

CC2420和微控制器连接的典型电路如图12所示。微控制器使用4个I/O口和CC2420的配置接口相连接(SI,SO,SCLK和CSn)。SO和微控制器的输入口连接,SI,SCLK和CSN和微控制器的输出口连接。最好的是微控制器具备硬件的SPI接口。

和SI,SO和SCLK连接的微控制器引脚可以和其他的SPI接口设备共用。在CSn为低电平的时候, SO输出高阻抗。

在内部稳压器关闭的时候,为了防止输入信号产生漂移,CSn需要外接一个上拉电阻或者置高。SI和SCLK需要置为规定的电平。

7.2 接收模式

在接收模式, 当收到完整的开始帧界定符(SFD)后,SFD将变为高电平,如果通过地址识别检测到信息是发给自己的,或者取消了地址识别功能,SFD将在MPDU接收完成之后变低。如果信息不是发给自己的,SFD将会立即变低。见图13。

如果RXFIFO中有一个或者多个字节信息,FIFO引脚将变高。写入RXFIFO中的第一个字节是接收帧的长度信息,也就是当帧长信息写入RXFIFO后FIFO引脚将变高。直到RXFIFO为空时FIFO才拉低。

如果先前接收的的帧全部或者部分还在RXFIFO中,FIFO引脚将保持高电平直到RXFIFO为空。

如果RXFIFO中的未读数据超过了编程设置的IOCFG0.FIFOP_THR的值,FIFOP引脚将变高。如果地址识别功能使能,在帧通过地址识别之前FIFOP是不会变高的,即使此时RXFIFO的数据长度超出了设置的极限值。

当一个信息包的最后一个字节数据接收完成后FIFOP也会变高,即使此时还没超过极限值。此时FIFOP将在RXFIFO中有一个字节的数据被读出之后变低。如果地址识别功能使能,在地址被完全识别之前数据将不会从RXFIFO中读出。因为如果帧没有被通过地址识别,CC2420将自动的将此帧丢弃。这可以通过使用FIFOP引脚来操作。因为该引脚只有数据帧在通过地址识别后才会变高。

7.3 RXFIFO溢出

RXFIFO每次最多只能包含128字节。RXFIFO溢出发生后需要使用SFLUSHRX命令来使其接收新的数据。注意SFLUSHRX命令必须使用两次以确保SFD引脚回到空闲状态。

对于安全使能帧,MAC必须要先读取收到帧的源地址,然后再决定使用哪个钥匙去解密和鉴别帧数据。

7.4 发送模式

在发送模式,FIFO和FIFOP引脚只与RXFIFO引脚相关,SFD引脚在传送数据帧的过程中总是处于活跃状态。

当帧的SFD字段被完全读取之后,SFD引脚变高。当MPDU完全传送完成之后或者侦测到溢出时,SFD变为低电平。

SFD引脚在接收和传送数据帧的变化状态非常相似。如果比较在接收和传送数据帧时接收器和发送器的SFD引脚区别,你会发觉有一个非常微小的大约为2 μs的时延,这是由于接收器和发送器的带宽限制引起的。

7.5 总体控制和状态引脚

在接收模式, 当门限值被超过或一个帧完全被接收时,FIFOP引脚会中断微控制器。这个引脚也应该和微控制器的中断引脚相连。

在接收模式,FIFOP引脚可以用来侦察是否数据都接收到了先进先出寄存器。

SFD引脚可以用来提取发送和接收数据帧的实时信息。当一个帧的开始分界符侦察到了或者被完全发送出去,SFD引脚就会变成高电平。SFD引脚更适合和微控制器的定时器引脚相联系。

为了调试,SFD引脚和CCA引脚可以监控许多用IOCFG1寄存器选择的状态信号。

FIFO,FIFOP,SFD,和CCA引脚的极性由IOCFG0寄存器(地址 Ox1C)控制。