【DRAM存储器十五】DDR介绍-关键技术之DLL和prefetch

个人主页:highman110

作者简介:一名硬件工程师,持续学习,不断记录,保持思考,输出干货内容

参考资料:《镁光DDR数据手册》

目录

DLL

预取

DDR SDRAM的几个新增时序参数解析

DLL

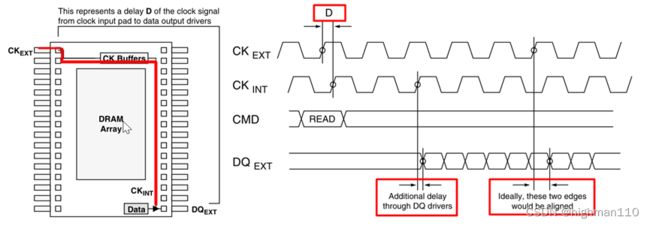

DLL,延迟锁相环:片上DLL是颗粒端输出DQ和DQS与全局时钟CLK同步的关键部件,从上面的镁光DDR4接口框图看到,外部全局时钟经过DLL延迟锁定后生成了一个与外部时钟同步的内部时钟,颗粒使用这个内部时钟来驱动DQ和DQS,以此获得全局同步。那为什么需要增加一个DLL呢?不能直接使用这个外部全局时钟去驱动颗粒的DQ和DQS输出吗?显然不可以,如下图所示,CKext为外部全局时钟输入,CKint为数据输出的内部驱动时钟,从CKext到CKint需要经过CK buffer和颗粒内部走线的延时,这个延时为D,在加上从CKint驱动有效,到数据DQext输出电平跳变,又有一个DQ driver的延时,所以CKext的跳边沿到DQ跳变沿的延时为:D+DQ driver的延时,这就不同步了。

所以需要使用DLL,将CKint与CKext同步对齐起来,下图红框中就是DLL的延迟时间,延迟时间为:一个外部时钟周期Tck-D。CKint与CKext同步之后,DQext也大致与外部时钟同步了(要求DQ driver的延时比较小)。

预取

预取prefetch:预取是DDR SDRAM新引进的技术。内存阵列的核心存储元件是电容,而电容的充电、放电是需要时间的,这就注定了存储cell的核心访问频率无法做得很高。DDR的数据在IO时钟的上升沿和下降沿各能传输一次,是SDR的两倍,若要保证两倍的数据输出量,又要保持核心频率不变,只能通过加倍内部数据传输位宽的方式,使存储阵列一次准备好2n bit(n=DQ位宽)的数据。如下所示为x4 DDR SDRAM颗粒的框图,外部数据DQ位宽为4,内部读锁存器位宽为8,也就是在给定行列地址后,内部一次性传输8bit数据,那它是怎么做到一次性能传输8比特数据的呢?我们可以看到下图存储阵列中每个bank的组成:

每个bank为4096 x 512 x 8,其中4096为阵列字线数,由12根行地址线解码后进行选择,512为阵列位线数,由9根列地址线解码后进行选择,8表示以上字线和位线选中后输出数据的位宽,在物理上这个具体怎么做的我不是很清楚,有如下两种猜测:

1、一个是纵向的,4096 x 512 x 8表示8张4096行512列的阵列叠在一起,如下图,选中字线和位线后,8张叠起来的阵列各输出1bit数据。

2、一种是横向的,4096 x 512 x 8只有一张阵列,字线4096根,位线512 x 8根,但是列地址解码后是按8根位线一组进行选中输出,一次性输出输出8bit数据。

以上两种结构在逻辑上都能讲通,具体究竟物理上怎么做的还请路过的大佬指点指点。

另外提一句,有一些文章提到了芯片位宽和configuration的一些说法,比如下图:

这里澄清一下,别把这东西搞复杂了,芯片位宽就是指的数据线DQ有几根,x4、x8、x16指的就是芯片有4根、8根、16根DQ线,所谓的configuration,也不要把他翻译成什么配置模式了,他就是一种产品的不同形态,比如我们常说的一台电脑插了多少G的内存,这就是一种configuration,在DDR芯片中这个配置指的就是芯片配了多少根DQ线,就这么简单,不要把这个x4、x8、x16硬与内部存储阵列的数量扯起来,他们之间可能有一定的关系(如果是我上面说的那种纵向结构,那每个bank的存储阵列数量=DQ位宽 * 预取倍数),也可能没有关系(如果是我上面说的那种横向结构,那就没关系,DQ再宽,预取再多,那也是一张阵列),这是两个概念。另外再说一下颗粒容量的表示方式,比如一个4Gb的颗粒可以表示为:1024 Meg x 4、512 Meg x 8、256 Meg x 16,有的文章将这种表示解释为,前面的数字表示颗粒能寻址的所有存储单元数量,后面的数字表示单个存储单元的存储容量,这种解释我不太理解,一个存储单元不是一个电容吗?一个电容要做到存4bit、8bit、甚至16bit的数据,这显然不合理,应该说这个存储单元只是逻辑上的概念,实际物理上他就是有多个电容,这组电容的寻址是共享的,输出是分开的。

另外,突发长度burst length和预取有一定的关系,下表为各代DDR支持的突发长度和预取数:

| SDRAM generation |

SDR |

DDR |

DDR2 |

DDR3 |

DDR4 |

DDR5 |

| Burst length |

1,2,4,8,full page |

2,4,8 |

4,8 |

8 |

8 |

16 |

| Prefetch |

1n |

2n |

4n |

8n |

8n |

16n |

从上表可以看到,SDRAM支持的最小突发长度就等于预取倍数,突发是指在同一行中相邻的存储单元连续进行数据传输的方式,连续传输所涉及到存储单元(应该不能说是存储单元的数量,应该是列地址的数量,一个列地址对应多个存储单元)的数量就是突发长度(SDRAM),在DDR SDRAM中突发长度指连续传输的周期数,如DDR中,BL=2时,就是一次突发传输2*DQ位宽比特数据,只需要一次预取,BL=4,就是一次突发传输4*DQ位宽比特数据,需要两次预取。很显然,由于有一次预取就能得到2*DQ位宽比特数据的限制,BL=1就意味着要丢掉一半数据,所以DDR一般不支持BL=1。DDR3支持BC4,保留前面4个burst,后面4个burst内容被mask掉,这是个特例,但是从本质上来说,它还是一次性取了8n的数据。另外,full page这种突发模式在常规的内存应用中很少用到,所以后面的DDR规范干脆把这种模式取消了。

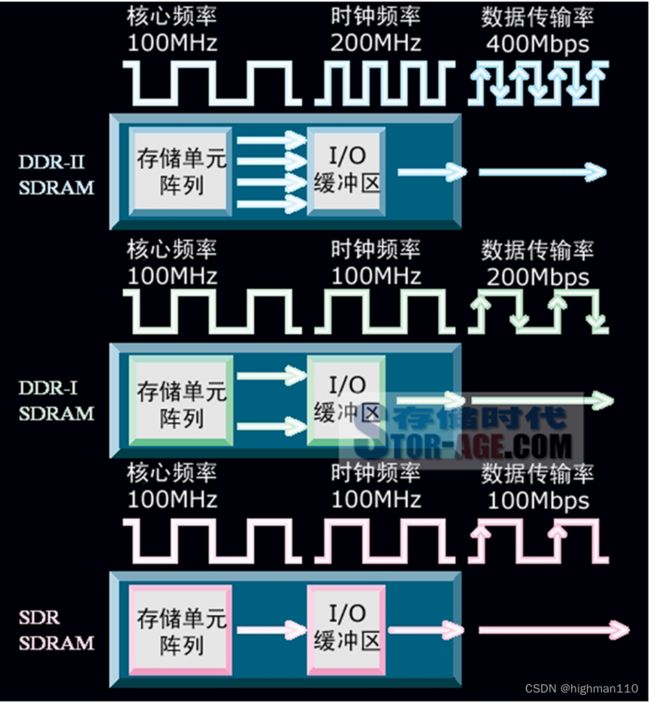

最后放一张网上流传甚广的图加深下对预取的理解:

DDR SDRAM的几个新增时序参数解析

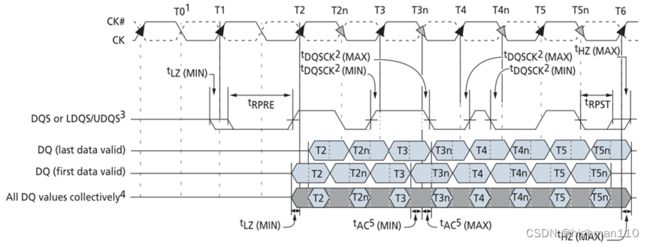

上图为读操作的数据输出时序图。从前面的DDR框图分析我们知道,DQ和DQS都是在经DLL同步后的时钟CK驱动下输出的,理论上所有DQ、DQS与外部系统时钟CK都是完全同步对齐的,但这仅仅是理论上,实际上经DLL生成的CK与外部时钟就可能有微小偏差,同时不同的DQ、DQS的颗粒内部走线也会有所差别,使得从输出驱动器输出到信号电平出现在外部IO上出现skew,于是就需要规范一些时序参数,厂家生产的颗粒skew不能超过这些参数的要求,如:

tDQSCK:表征DQS边沿相对CK边沿的偏差,理论上改值应为0,实际上DQS可能提前CK跳变,也可能滞后CK跳变,滞后好理解,就是内部CK在输出驱动器驱动DQS跳变后,DQS跳变电平要经过内部走线延迟才出现在IO上,那提前跳变怎么理解呢,我的理解是DLL生成的内部CK比外部系统CK相位提前了,才导致内部CK驱动的DQS也提前了。此参数单位为ns。

tAC:表征所有DQ边沿相对CK边沿的偏差,这个参数的道理和上面的基本一样。此参数单位为ns。

tRPRE:DQS读preamble,在读数据输出前DQS拉低一段时期,用来表示数据即将输出,通知接收端做好准备,单位为tCK,DDR里一般为1个tCK。

tRPST:DQS读postmble,在读数据的最后一笔数据输出的同时,拉低0.5个tCK,用来表示本次数据传输完毕。

上图是写数据输入的时序。

tDQSS:初代SDRAM写命令和数据输入是在同一个时钟上升沿生效的,DDR不一样了,写命令后要等tDQSS间隔后才能数据才能输入,正常是1个tCK,最小0.75tCK,最大为1.25tCK,太小可能导致写入错误(内部控制逻辑还没准备完毕),太大则影响总线效率。

tWPRES:DQS write preamble setup time,最小值为0ns。

tWPRE:DQS write preamble,道理与tRPRE类似,最小值为0.25tCK。

tWPST:DQS write postmble,道理与tRPST类似,一般为0.5tCK。

DDR的介绍就到这里,接下来开始DDR2,敬请期待。