产生问题的原因就是通过此标签的样式不能使用css样式。因为数据直接解析,那么我们可以修改或者处理这个数据来解决问题解决方法,通过修改数据中的文本内容中的img标签的内联样式来实现formatGoodsData(data){letcontent=data.goods_contentcontent=content.replace(/\

![SQLSERVER 中GO的作用详解]()

SQLSERVER 中GO的作用详解

为了省事,直接贴过来的。请看下文详解。usedb_CSharpgoselect*,备注=casewhenGrade>=90then'成绩优秀'whenGrade=80then'成绩良好'whenGrade=70then'成绩及格'else'不及格'endfromtb_Grade如果只是执行一条语句,有没有GO都一样如果多条语句之间用GO分隔开就不一样了每个被GO分隔的语句都是一个单独的事务,一个语

麒麟系统使用-进行.NET开发

mystonelxj

麒麟系统.net麒麟系统控制台及web

文章目录前言一、搭建dotnet环境1.获取相关资源2.配置dotnet二、使用dotnet三、其他说明总结前言麒麟系统的内核是基于linux的,如果需要进行.NET开发,则需要安装特定的应用。由于NETFramework是仅适用于Windows版本的.NET,所以要进行.NET开发需要特定的安装及配置。使用.NET方式与在windows环境下使用有些出入。本文将细致讲解在如何在麒麟系统中使用.N

麒麟系统使用-个性化设置

mystonelxj

麒麟系统麒麟系统个性化设置

文章目录前言一、个性化设置-背景二、个性化设置-主题三、个性化设置-锁屏四、个性化设置-屏保五、个性化设置-字体总结前言与windows系统相比,麒麟系统中的个性化设置大体相似,在细节上稍有不同。本文将讲述麒麟系统中的个性化设置中的各个模块。一、个性化设置-背景进入麒麟系统后,打开“设置”对话框,点击“个性化”区域,进入个性化设置界面默认情况下,进入个性化设置界面后打开的是“背景”模块,我们可以根

vue3 添加onShow,每次显示都执行

萧大侠jdeps

前端vue.jsjavascript

vue3的生命周期没有onShow,uniapp有提供onShow.有时候我们希望用户离开在回到页面时,把他最关心的可能变化比较平繁的数据刷新出来。constonShow=()=>{//这里执行刷新}onMounted(()=>{initData();document.addEventListener('visibilitychange',onShow);});onUnmounted(()=>{d

工厂模式中使用Map管理策略实例时,为何仍需要Context?

看这篇文章前,可以先了解一下:策略模式与工厂模式的黄金组合:从设计到实战一、核心矛盾:创建职责与调用职责的分离问题当使用Map管理策略实例时(如MapstrategyMap),工厂确实能高效获取策略实例,但这仅解决了**“策略从哪里来"的问题。而策略的"如何使用”**仍面临以下挑战:上下文逻辑碎片化:策略调用前后的公共逻辑(如参数校验、结果处理)会散落在客户端代码中调用流程不一致:不同客户端可能以

8、做中学 | 四年级下期 Golang运算符

运算符:在程序中扮演执行数学、逻辑运算的过程一、算术运算符数学运算使用到的运算符运算符描述实例+相加A+B输出结果30-相减A-B输出结果-10*相乘A*B输出结果200/相除B/A输出结果2%求余B%A输出结果0++自增A++输出结果11–自减A--输出结果9//运算符varaint=10varbint=20varcint//+运算c=a+bfmt.Println("c=",c)//30//-c

用Tensorflow进行线性回归和逻辑回归(十)

lishaoan77

tensorflow线性回归tensorboard可视化

用TensorBoard可视化线性回归模型TensorBoard是一种可视化工具,用于了解、调试和优化模型训练过程。它使用在执行程序时编写的摘要事件。上面定义的模型使用tf.summary.FileWriter来写日志到日志目录/tmp/lr-train.我们可以用命令调用日志目录的TensorBoard,见Example3-13(TensorBoard已黙认安装与TensorFlow一起).Ex

[redis系列] redis脚本

en-route

redis数据库

介绍RedisLua脚本功能使得用户能够在Redis服务器端执行自定义的Lua脚本,从而实现更高效、更灵活的数据操作。Lua脚本运行在Redis服务器内部,这意味着你可以减少客户端与服务器之间的通信开销,并且可以通过原子操作确保多个Redis命令的执行一致性。组合功能:Lua脚本能够将Redis中的简单命令组合起来,从而实现复杂的业务需求,避免多次网络往返。数据操作原子性:通过Lua脚本,开发者可

[redis系列] 发布订阅 Pub/Sub

en-route

redis数据库缓存

介绍Redis的发布/订阅(Pub/Sub)模式允许发布者通过通道广播消息,发布者不关心是否有订阅者;订阅者根据兴趣接收相关消息,而无需了解具体的发布者。这种机制通过将发布者和订阅者解耦,使得它们不直接依赖于对方,大大提高了系统的扩展性。如果您对Redis相关内容感兴趣,欢迎查看我的Redis系列博客。匹配订阅SUBSCRIBE该命令返回值的第三个表示当前客户端已订阅的频道总数。#订阅频道my_c

【MSSQL】sql server怎样整理某个表的碎片

厦门德仔

MSSQLsqlserver数据库服务器

SQLServer如何整理某个表的碎片在数据库的维护过程中,碎片化是一个常见的问题。随着数据的插入、更新和删除,SQLServer中的表和索引可能会出现碎片,这会导致查询性能下降。本文将介绍如何在SQLServer中整理某个表的碎片,并提供代码示例帮助你理解。什么是碎片化?碎片化是指数据在物理存储上不连续,导致数据库无法有效利用存储空间。碎片化通常分为两种类型:内部碎片:数据页中存在空闲空间,没有

【vue.js之夯实基础-3】TypeScript 入门之简介

alwarse

vuejstypescriptjavascriptvue.js

教程实例参照->入门教程详细教程参照->详细教程完全教程->完全教程什么是TypeScriptTypedJavaScriptatAnyScale.添加了类型系统的JavaScript,适用于任何规模的项目。TypeScript的特性类型系统从TypeScript的名字就可以看出来,「类型」是其最核心的特性。我们知道,JavaScript是一门非常灵活的编程语言:它没有类型约束,一个变量可能初始化时

embedding模型有哪些?如何选择合适的embedding模型?

行云流水AI笔记

embedding

embedding模型是一种将数据映射到低维空间的模型,常用于自然语言处理、推荐系统、图像识别等领域。以下是一些常见的embedding模型:Word2Vec:CBOW(ContinuousBag-of-Words):通过上下文预测中心词。Skip-Gram:通过中心词预测上下文。GloVe(GlobalVectorsforWordRepresentation):结合了词频统计和Word2Vec的

强化学习 16G实践以下是基于CQL(Conservative Q-Learning)与QLoRA(Quantized Low-Rank Adaptation)结合的方案相关开源项目及资源,【ai技】

行云流水AI笔记

开源人工智能

根据你提供的CUDA版本(11.5)和NVIDIA驱动错误信息,以下是PyTorch、TensorFlow的兼容版本建议及环境修复方案:1.版本兼容性表框架兼容CUDA版本推荐安装命令(CUDA11.5)PyTorch11.3/11.6pipinstalltorchtorchvisiontorchaudio--extra-index-urlhttps://download.pytorch.org/

【DeepSeek实战】3、Ollama实战指南:LobeChat+多网关架构打造高可用大模型集群

无心水

Ollama实战指南LobeChat实战DeepSeek实战DeepSeek全栈应用开发AI入门大模型CSDN技术干货

一、企业级大模型集群架构全景解析在人工智能落地应用的过程中,大模型服务的高可用性、成本控制和灵活扩展能力成为企业关注的核心痛点。本方案通过LobeChat前端、AI网关层和Ollama模型集群的三层架构设计,实现了无需复杂运维即可部署的生产级大模型服务体系。该架构不仅支持负载均衡、故障转移和模型热切换等企业级特性。还通过量化技术将硬件成本降低60%以上,为中小企业提供了与商业云服务相当的性能体验。

pdf 不是扫描件,但却无法搜索关键词【问题尝试解决未果记录】

Lauren_Lu

pdf

一、不是扫描件但不能搜索的原因1.情况一:文字被转成了“图形文字”有些PDF文件虽然看起来像是文字,其实是图片或者矢量图格式,不能直接搜索。2.情况二:PDF被加密有些PDF设置了“内容复制/提取”权限受限,即使你能阅读,但不能搜索、复制或选择文字。这通常是加密的一种表现。3.情况三:PDF嵌入了字体,但不是真正的文本有时PDF作者用的特殊软件或字体,会让文字显示正常,但实际上是不可识别的字符二、

如何在 ArcGIS 中使用 Microsoft Excel 文件_20250614

Lauren_Lu

arcgismicrosoftexcel

如何在ArcGIS中使用MicrosoftExcel文件软件版本:win11;ArcGIS10.8;Office20241.确认ArcGIS10.8对.xlsx文件的支持ArcGIS10.8支持.xlsx文件(Excel2007及以上格式),但需要安装MicrosoftAccessDatabaseEngine驱动程序来读取这些文件。ArcGIS10.8是一个32位应用程序,因此需要32位的驱动程序

print(3 or 5)的结果是什么?为什么?

Lauren_Lu

python

print(3or5)的结果是:3原因:在Python中,or是一个逻辑运算符,但当它作用于非布尔类型(比如整数)时,它的行为是:返回第一个为真的值;如果第一个值为假,则返回第二个值。具体分析:3是一个非零整数,在布尔上下文中被视为True所以3or5就是:如果3是True,就返回3;否则返回5由于3是True,所以返回的是3。类似例子:print(0or5)#输出5,因为0被视为Falsepri

深度学习实战:基于嵌入模型的AI应用开发

AIGC应用创新大全

AI人工智能与大数据应用开发MCP&Agent云算力网络人工智能深度学习ai

深度学习实战:基于嵌入模型的AI应用开发关键词:嵌入模型(EmbeddingModel)、深度学习、向量空间、语义表示、AI应用开发、相似性搜索、迁移学习摘要:本文将带你从0到1掌握基于嵌入模型的AI应用开发全流程。我们会用“翻译机”“数字身份证”等生活比喻拆解嵌入模型的核心原理,结合Python代码实战(BERT/CLIP模型)演示如何将文本、图像转化为可计算的语义向量,并通过“智能客服问答”“

java的(PO,VO,TO,BO,DAO,POJO)

Cb123456

VOTOBOPOJODAO

转:

http://www.cnblogs.com/yxnchinahlj/archive/2012/02/24/2366110.html

-------------------------------------------------------------------

O/R Mapping 是 Object Relational Mapping(对象关系映

spring ioc原理(看完后大家可以自己写一个spring)

aijuans

spring

最近,买了本Spring入门书:spring In Action 。大致浏览了下感觉还不错。就是入门了点。Manning的书还是不错的,我虽然不像哪些只看Manning书的人那样专注于Manning,但怀着崇敬 的心情和激情通览了一遍。又一次接受了IOC 、DI、AOP等Spring核心概念。 先就IOC和DI谈一点我的看法。IO

MyEclipse 2014中Customize Persperctive设置无效的解决方法

Kai_Ge

MyEclipse2014

高高兴兴下载个MyEclipse2014,发现工具条上多了个手机开发的按钮,心生不爽就想弄掉他!

结果发现Customize Persperctive失效!!

有说更新下就好了,可是国内Myeclipse访问不了,何谈更新...

so~这里提供了更新后的一下jar包,给大家使用!

1、将9个jar复制到myeclipse安装目录\plugins中

2、删除和这9个jar同包名但是版本号较

SpringMvc上传

120153216

springMVC

@RequestMapping(value = WebUrlConstant.UPLOADFILE)

@ResponseBody

public Map<String, Object> uploadFile(HttpServletRequest request,HttpServletResponse httpresponse) {

try {

//

Javascript----HTML DOM 事件

何必如此

JavaScripthtmlWeb

HTML DOM 事件允许Javascript在HTML文档元素中注册不同事件处理程序。

事件通常与函数结合使用,函数不会在事件发生前被执行!

注:DOM: 指明使用的 DOM 属性级别。

1.鼠标事件

属性

动态绑定和删除onclick事件

357029540

JavaScriptjquery

因为对JQUERY和JS的动态绑定事件的不熟悉,今天花了好久的时间才把动态绑定和删除onclick事件搞定!现在分享下我的过程。

在我的查询页面,我将我的onclick事件绑定到了tr标签上同时传入当前行(this值)参数,这样可以在点击行上的任意地方时可以选中checkbox,但是在我的某一列上也有一个onclick事件是用于下载附件的,当

HttpClient|HttpClient请求详解

7454103

apache应用服务器网络协议网络应用Security

HttpClient 是 Apache Jakarta Common 下的子项目,可以用来提供高效的、最新的、功能丰富的支持 HTTP 协议的客户端编程工具包,并且它支持 HTTP 协议最新的版本和建议。本文首先介绍 HTTPClient,然后根据作者实际工作经验给出了一些常见问题的解决方法。HTTP 协议可能是现在 Internet 上使用得最多、最重要的协议了,越来越多的 Java 应用程序需

递归 逐层统计树形结构数据

darkranger

数据结构

将集合递归获取树形结构:

/**

*

* 递归获取数据

* @param alist:所有分类

* @param subjname:对应统计的项目名称

* @param pk:对应项目主键

* @param reportList: 最后统计的结果集

* @param count:项目级别

*/

public void getReportVO(Arr

访问WEB-INF下使用frameset标签页面出错的原因

aijuans

struts2

<frameset rows="61,*,24" cols="*" framespacing="0" frameborder="no" border="0">

MAVEN常用命令

avords

Maven库:

http://repo2.maven.org/maven2/

Maven依赖查询:

http://mvnrepository.com/

Maven常用命令: 1. 创建Maven的普通java项目: mvn archetype:create -DgroupId=packageName

PHP如果自带一个小型的web服务器就好了

houxinyou

apache应用服务器WebPHP脚本

最近单位用PHP做网站,感觉PHP挺好的,不过有一些地方不太习惯,比如,环境搭建。PHP本身就是一个网站后台脚本,但用PHP做程序时还要下载apache,配置起来也不太很方便,虽然有好多配置好的apache+php+mysq的环境,但用起来总是心里不太舒服,因为我要的只是一个开发环境,如果是真实的运行环境,下个apahe也无所谓,但只是一个开发环境,总有一种杀鸡用牛刀的感觉。如果php自己的程序中

NoSQL数据库之Redis数据库管理(list类型)

bijian1013

redis数据库NoSQL

3.list类型及操作

List是一个链表结构,主要功能是push、pop、获取一个范围的所有值等等,操作key理解为链表的名字。Redis的list类型其实就是一个每个子元素都是string类型的双向链表。我们可以通过push、pop操作从链表的头部或者尾部添加删除元素,这样list既可以作为栈,又可以作为队列。

&nbs

谁在用Hadoop?

bingyingao

hadoop数据挖掘公司应用场景

Hadoop技术的应用已经十分广泛了,而我是最近才开始对它有所了解,它在大数据领域的出色表现也让我产生了兴趣。浏览了他的官网,其中有一个页面专门介绍目前世界上有哪些公司在用Hadoop,这些公司涵盖各行各业,不乏一些大公司如alibaba,ebay,amazon,google,facebook,adobe等,主要用于日志分析、数据挖掘、机器学习、构建索引、业务报表等场景,这更加激发了学习它的热情。

【Spark七十六】Spark计算结果存到MySQL

bit1129

mysql

package spark.examples.db

import java.sql.{PreparedStatement, Connection, DriverManager}

import com.mysql.jdbc.Driver

import org.apache.spark.{SparkContext, SparkConf}

object SparkMySQLInteg

Scala: JVM上的函数编程

bookjovi

scalaerlanghaskell

说Scala是JVM上的函数编程一点也不为过,Scala把面向对象和函数型编程这两种主流编程范式结合了起来,对于熟悉各种编程范式的人而言Scala并没有带来太多革新的编程思想,scala主要的有点在于Java庞大的package优势,这样也就弥补了JVM平台上函数型编程的缺失,MS家.net上已经有了F#,JVM怎么能不跟上呢?

对本人而言

jar打成exe

bro_feng

java jar exe

今天要把jar包打成exe,jsmooth和exe4j都用了。

遇见几个问题。记录一下。

两个软件都很好使,网上都有图片教程,都挺不错。

首先肯定是要用自己的jre的,不然不能通用,其次别忘了把需要的lib放到classPath中。

困扰我很久的一个问题是,我自己打包成功后,在一个同事的没有装jdk的电脑上运行,就是不行,报错jvm.dll为无效的windows映像,如截图

最后发现

读《研磨设计模式》-代码笔记-策略模式-Strategy

bylijinnan

java设计模式

声明: 本文只为方便我个人查阅和理解,详细的分析以及源代码请移步 原作者的博客http://chjavach.iteye.com/

/*

策略模式定义了一系列的算法,并将每一个算法封装起来,而且使它们还可以相互替换。策略模式让算法独立于使用它的客户而独立变化

简单理解:

1、将不同的策略提炼出一个共同接口。这是容易的,因为不同的策略,只是算法不同,需要传递的参数

cmd命令值cvfM命令

chenyu19891124

cmd

cmd命令还真是强大啊。今天发现jar -cvfM aa.rar @aaalist 就这行命令可以根据aaalist取出相应的文件

例如:

在d:\workspace\prpall\test.java 有这样一个文件,现在想要将这个文件打成一个包。运行如下命令即可比如在d:\wor

OpenJWeb(1.8) Java Web应用快速开发平台

comsci

java框架Web项目管理企业应用

OpenJWeb(1.8) Java Web应用快速开发平台的作者是我们技术联盟的成员,他最近推出了新版本的快速应用开发平台 OpenJWeb(1.8),我帮他做做宣传

OpenJWeb快速开发平台以快速开发为核心,整合先进的java 开源框架,本着自主开发+应用集成相结合的原则,旨在为政府、企事业单位、软件公司等平台用户提供一个架构透

Python 报错:IndentationError: unexpected indent

daizj

pythontab空格缩进

IndentationError: unexpected indent 是缩进的问题,也有可能是tab和空格混用啦

Python开发者有意让违反了缩进规则的程序不能通过编译,以此来强制程序员养成良好的编程习惯。并且在Python语言里,缩进而非花括号或者某种关键字,被用于表示语句块的开始和退出。增加缩进表示语句块的开

HttpClient 超时设置

dongwei_6688

httpclient

HttpClient中的超时设置包含两个部分:

1. 建立连接超时,是指在httpclient客户端和服务器端建立连接过程中允许的最大等待时间

2. 读取数据超时,是指在建立连接后,等待读取服务器端的响应数据时允许的最大等待时间

在HttpClient 4.x中如下设置:

HttpClient httpclient = new DefaultHttpC

小鱼与波浪

dcj3sjt126com

一条小鱼游出水面看蓝天,偶然间遇到了波浪。 小鱼便与波浪在海面上游戏,随着波浪上下起伏、汹涌前进。 小鱼在波浪里兴奋得大叫:“你每天都过着这么刺激的生活吗?简直太棒了。” 波浪说:“岂只每天过这样的生活,几乎每一刻都这么刺激!还有更刺激的,要有潮汐变化,或者狂风暴雨,那才是兴奋得心脏都会跳出来。” 小鱼说:“真希望我也能变成一个波浪,每天随着风雨、潮汐流动,不知道有多么好!” 很快,小鱼

Error Code: 1175 You are using safe update mode and you tried to update a table

dcj3sjt126com

mysql

快速高效用:SET SQL_SAFE_UPDATES = 0;下面的就不要看了!

今日用MySQL Workbench进行数据库的管理更新时,执行一个更新的语句碰到以下错误提示:

Error Code: 1175

You are using safe update mode and you tried to update a table without a WHERE that

枚举类型详细介绍及方法定义

gaomysion

enumjavaee

转发

http://developer.51cto.com/art/201107/275031.htm

枚举其实就是一种类型,跟int, char 这种差不多,就是定义变量时限制输入的,你只能够赋enum里面规定的值。建议大家可以看看,这两篇文章,《java枚举类型入门》和《C++的中的结构体和枚举》,供大家参考。

枚举类型是JDK5.0的新特征。Sun引进了一个全新的关键字enum

Merge Sorted Array

hcx2013

array

Given two sorted integer arrays nums1 and nums2, merge nums2 into nums1 as one sorted array.

Note:You may assume that nums1 has enough space (size that is

Expression Language 3.0新特性

jinnianshilongnian

el 3.0

Expression Language 3.0表达式语言规范最终版从2013-4-29发布到现在已经非常久的时间了;目前如Tomcat 8、Jetty 9、GlasshFish 4已经支持EL 3.0。新特性包括:如字符串拼接操作符、赋值、分号操作符、对象方法调用、Lambda表达式、静态字段/方法调用、构造器调用、Java8集合操作。目前Glassfish 4/Jetty实现最好,对大多数新特性

超越算法来看待个性化推荐

liyonghui160com

超越算法来看待个性化推荐

一提到个性化推荐,大家一般会想到协同过滤、文本相似等推荐算法,或是更高阶的模型推荐算法,百度的张栋说过,推荐40%取决于UI、30%取决于数据、20%取决于背景知识,虽然本人不是很认同这种比例,但推荐系统中,推荐算法起的作用起的作用是非常有限的。

就像任何

写给Javascript初学者的小小建议

pda158

JavaScript

一般初学JavaScript的时候最头痛的就是浏览器兼容问题。在Firefox下面好好的代码放到IE就不能显示了,又或者是在IE能正常显示的代码在firefox又报错了。 如果你正初学JavaScript并有着一样的处境的话建议你:初学JavaScript的时候无视DOM和BOM的兼容性,将更多的时间花在 了解语言本身(ECMAScript)。只在特定浏览器编写代码(Chrome/Fi

Java 枚举

ShihLei

javaenum枚举

注:文章内容大量借鉴使用网上的资料,可惜没有记录参考地址,只能再传对作者说声抱歉并表示感谢!

一 基础 1)语法

枚举类型只能有私有构造器(这样做可以保证客户代码没有办法新建一个enum的实例)

枚举实例必须最先定义

2)特性

&nb

Java SE 6 HotSpot虚拟机的垃圾回收机制

uuhorse

javaHotSpotGC垃圾回收VM

官方资料,关于Java SE 6 HotSpot虚拟机的garbage Collection,非常全,英文。

http://www.oracle.com/technetwork/java/javase/gc-tuning-6-140523.html

Java SE 6 HotSpot[tm] Virtual Machine Garbage Collection Tuning

&

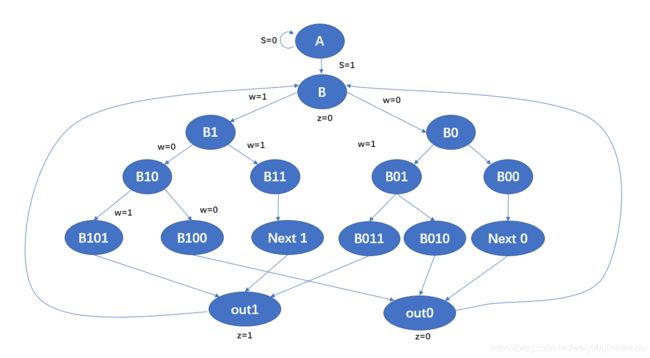

图2.状态机示意图