转载 http://www.cnblogs.com/IClearner/ ,作者:IC_learner

1、逻辑综合的概述

synthesis = translation + logic optimization + gate mapping .

DC工作流程主要分为这三步

Translation : 翻译,主要把描述RTL级的HDL语言,在约束下转换成DC内部的统一用门级描述的电路(Generic Boolean Gates)(DC自己的库表现),以GTECH或者没有映射的ddc形式展现。

Logic optimization :逻辑优化, 就是把统一用门级描述的电路进行优化,就是把路径调整一下,门给改一下等等。

Gate mapping :门级映射,把优化了的统一门级描述,DC用别的厂商的工艺库把电路给映射出来,得到一个.ddc文件。这个.ddc文件可以包含许多丰富的信息,比如映射的门电路信息与网表、.v格式的网表、延时信息(sdf)、工作约束(sdc)等信息。(.ddc不能用文本编辑器打开)。.ddc这个包含的网表文件是实际意义的网表文件,而.v这个形式的网表问价是用来做后仿真的文件。

延时信息的得出:线负载模型、拓扑结构模型(现在)。

2、DC的启动方式

启动DC的方式有三种:

·GUI:DC的图形化界面格式。用图形化界面跑一下DC。(大规模设计不可能用这种方式)。

启动方式是:$design_vision

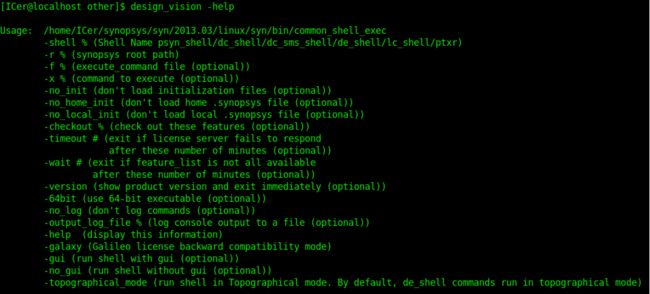

我们可以通过 man design_vision或者design_vision -help来查看DC的启动选项:

例如,可以使用$ design_vision -topographical_mode启动design compiler,意思是:-topographical是启动DC的拓扑模式,-topo是简写。关于什么是拓扑模式,为什么要启动拓扑模式,后面会有相关的叙述。

此外,还有下面的启动方式:

·dc_shell: DC以命令行的格式启动:$dc_shell

我们可以通过 man dc_shell或者dc_shell -help来查看DC的启动选项,不过我们可以发现,这些选项是一致的,是告诉我们如何启动DC,启动DC的时候可以加载哪些选项。

·Batch mode:批处理模式,也就是,前面那两种方式只是把DC启动起来,还没有真正地工作(即编译工程),前面两个方式需要通过source命令把脚本写进去以后,DC读取才真正工作。而这种批处理模式是,在启动的同时,告诉DC执行哪些脚本,例如:

$dc_shell -topo -f run.tcl | tee -i run.log

意思是:使用拓扑模式启动DC,启动的同时执行run.tcl脚本文件,并且把启动过程中显示在终端的信息记录到run.log中。| tee -i就是写进信息的管道命令,讲dc_shell -topo -f run.tcl 执行后显示的信息(输出结果),流入到run.log文件中。这样子是为了在DC启动失败的时候,通过查看启动信息,进而排除错误。

本教程这三种方式在后面都有流程介绍,本教程以命令行和批处理为主,其中dc_shell主要用来介绍DC的相关命令,此外命令行和批处理模式是现在设计的主要操作方式。

3、DC-Tcl语言的基本结构

下面介绍常见的tcl语言语法,这些语法在进行编写tcl脚本的时候比较常见。

Tcl的语法比较简单,依葫芦画瓢就可以知道写的是什么了。

我们在dc_shell的环境下,介绍tcl的一些简单语法(即启动DC,在dc_shell里面运行tcl文件):

通过编写example.tcl中的内容,来记录一下tcl的语法:

·设置变量

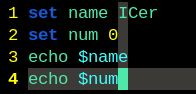

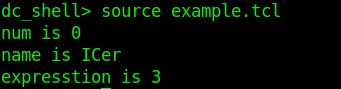

example.tcl的内容为:

意思是:设置name这个变量,这个变量的值为ICer;

设置num这个变量,这个值为 0;

echo是打印的意思,$表示引用,分别是打印name中的值,打印num中的值.

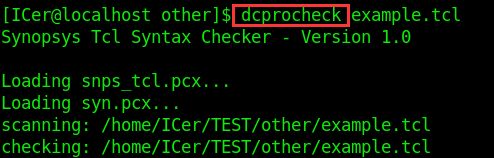

我们可以检查一下是否有语法错误,使用dcprocheck命令:

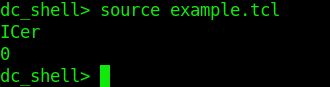

运行一下,打印出了name和num这两个变量的值:

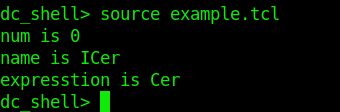

·if-else语句:

与C语言、Verilog语言不一样,这里的条件是用大括号{}来进行包括的,然后要执行的内容也是通过{}来表示的。特别注意,{}的使用都有空格间隔开

检查没有错误,进行执行:

·switch 结构

puts也是显示/打印的命令,执行后的结果如下:

还可以添加默认的选项:

执行后,显示:

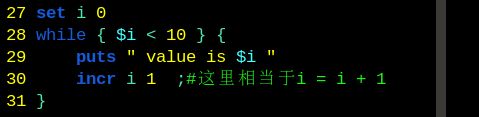

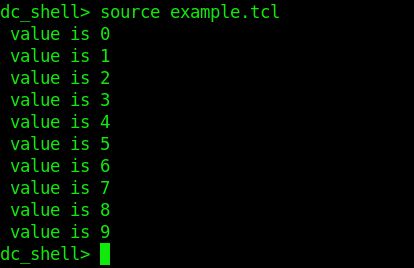

·while循环

执行的结果如下:

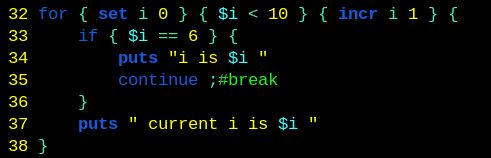

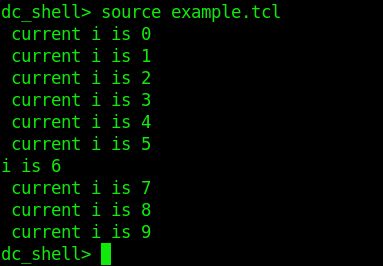

·for循环

运行的结果如下所示:

for循环的格式跟C语言一样,也有三个选项,初始条件,停止循环条件,变量递增选项。

Continue跟C语言一样,不执行本次循环。

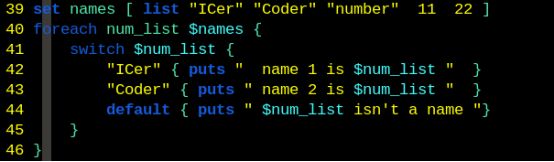

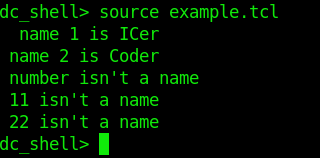

·数组(列表)与数组(列表)的遍历

首先,39行那里创建了一个名字为names的数组(列表),数组(列表)的内容有5项。

Foreach则是逐个遍历,查看数组的内容。首先把names这个列表的内容一次放进num_list这个变量里面,然后一次查看

附注:foreach_incollection对物集(collection)遍历。关于物集这个概念在后面会有说到,这里先提及一下,有一个初步印象。

执行结果如下:

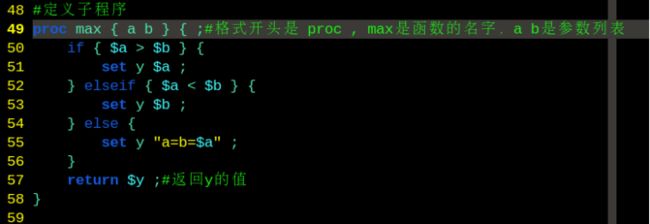

·子程序的定义和调用:

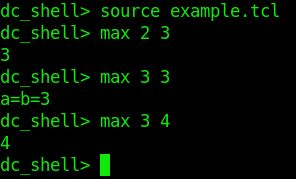

调用要在dc_shell中调用:

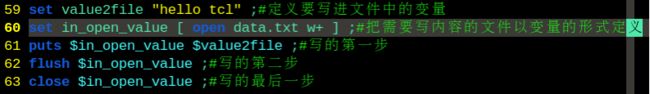

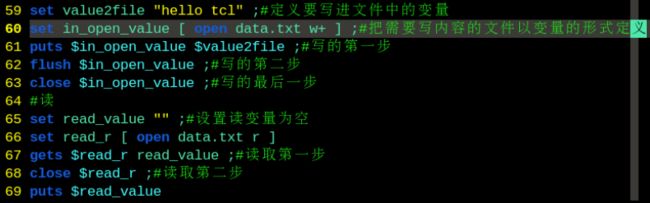

·最后是文件的处理:文件的读写

写:

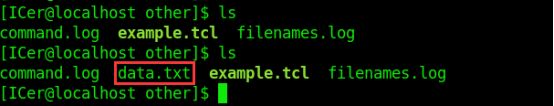

执行的结果如下所示:

Data.txt里面就有hello tcl

读:

注意gets的用法,执行后的结果如下:

Tcl的基本语法结构差不多就是这样了,Tcl的使用需要结合Tcl自带的一些命令,比如说自己的函数、错误处理、正则表达式等,此外还要结合DC的命令,总之就是具体问题具体分析。