计算机组成原理第三章 13 主存芯片的构成 主存和CPU之间的连接 字扩展和位扩展 $\color{red}{2^n}$

文章目录

-

-

-

- 主存储器存储芯片的构成 单个存储器芯片和CPU的连接

- 位扩展

- 字扩展

- 字位同时扩展

- 字扩展和位扩展中地址线,数据线,读写控制线,片选线的共用

- 字扩展和交叉编址的区别

- 存储器容量相除以后得到的结果

-

-

主存储器存储芯片的构成 单个存储器芯片和CPU的连接

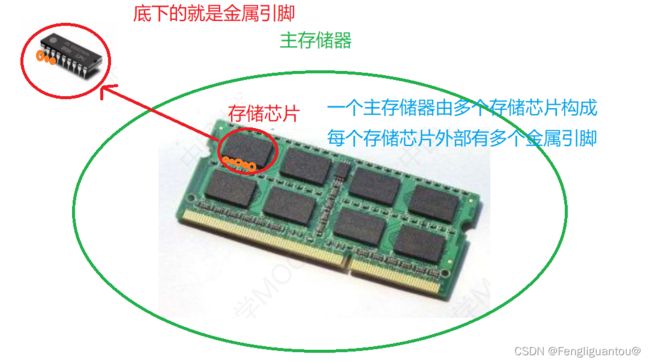

首先我们需要知道主存储器由多个存储芯片构成,每个存储芯片内含有多个存储单元,而主存使用的芯片一般是DRAM,我们下面介绍的就是DRAM,但是现在的主存一般是使用SDRAM了。

在计算机中存储的都是高低电平的电信号,通过高电平代表1,低电平代表0。接下来我们看看一个存储芯片是如何存储这些二进制高低电平信息的:

存储芯片是通过存储元来存储高低电平信息的,一个存储元可以存储一个二进制信息。

( 1 ) (1) (1)存储元

简单来看,存储元由这两个部件构成:

1.MOS管

2.一个下极板接地的电容

电容:在高中物理我们就有接触过电容这一元器件,电容由上极板,下极板和夹在中间的介质组成。对于电容这一元器件来说,当上下极板产生电压差以后,电荷就会在电容中产生流动,可以起到对电容进行充电的作用。在计算机中,电容内含有电荷表示二进制的1信号,不含有电荷则表示二进制的0信号。

MOS管:MOS管是一个半导体元器件,MOS管有一定的导通电压,只有当电压达到导通电压以后,MOS管才会导通,才能通过电流。如果没有达到导通电压,MOS管就是断开的,无法通过电流。

注:MOS管是一个半导体元器件,半导体的意思就是半导通,半绝缘,MOS管高电平时导通,低电平时绝缘。

存储元是如何存储二进制的信息的?

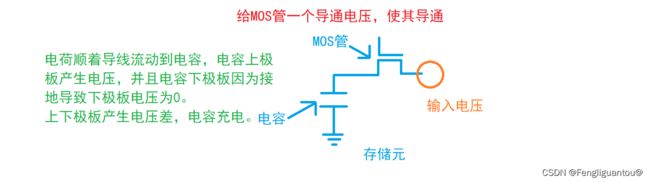

如何存储二进制的1信号?

1.给MOS管一个导通电压,使其导通以后能够通过电流

2.输入一定的电压,电荷随着导线流动到电容的上极板,上下极板产生电压差,电容内电荷流动,对电容起到充电作用。

3.电容充电完毕以后将MOS管断开,这样电荷就保存在电容中了。

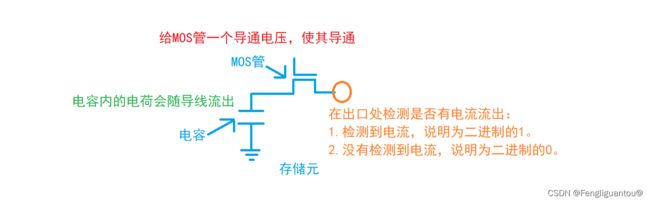

如何读取存储元中的二进制01信号?

给MOS管一个导通电压,使其导通,电容内的电荷会随着导线流出。在电流的出口处进行检测:

1.检测到电流,说明为二进制的1。

2.没有检测到电流,说明为二进制的0。

在明白了存储元以后我们看下存储单元是如何设计的:

一个存储单元就是由多个MOS管组成,一个存储单元的内容MOS管被一根导线串联在一起,所以只要红色的这跟导线发送一个高电平信号,处于一个存储单元的MOS管就都会被导通,加上每个MOS管都连接了数据总线,这样我们一次就可以读出一个存储单元的数据,这也是为什么我们之前说每次读取的基本单位是一个存储单元。

在明白了存储单元的设计以后,我们开始融入其他的部件:

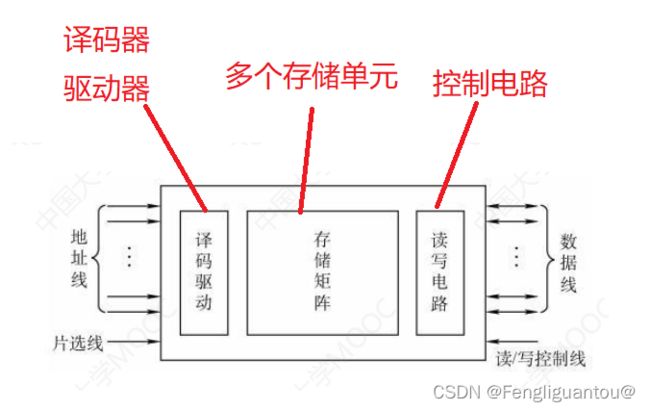

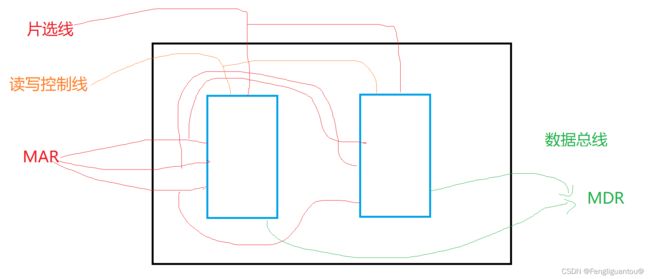

事实上一个完整的存储器芯片是如下的(不包括MDR和MAR)。

对此我们进行一一的介绍:

字扩展

字扩展扩展的是什么?

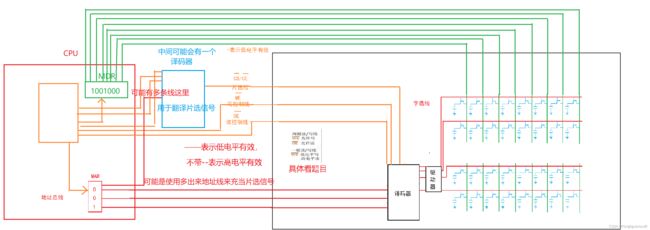

通过扩展存储器芯片的数量,从而扩展存储单元的个数。字扩展,也就是增加存储器芯片的个数,增大寻址范围。说白了就是CPU选择导通哪一个存储器芯片

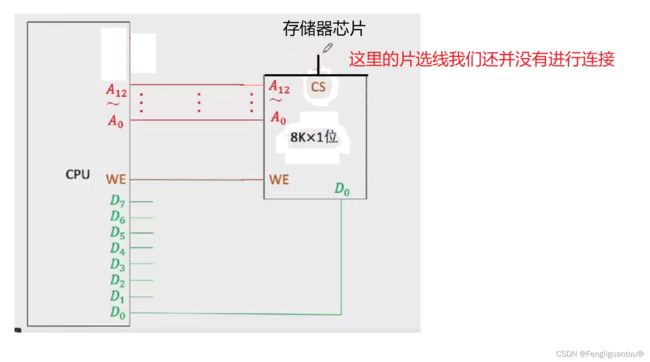

前面我们说过每个存储器芯片都有一个片选信号,当接收到片选信号的时候,存储器芯片才能开始工作,在计算机中片选信号是CPU发送的,实际上CPU是通过地址总线来发送片选信号的,其中片选信号的发送方式具有两种,分别是线选法和片选法。

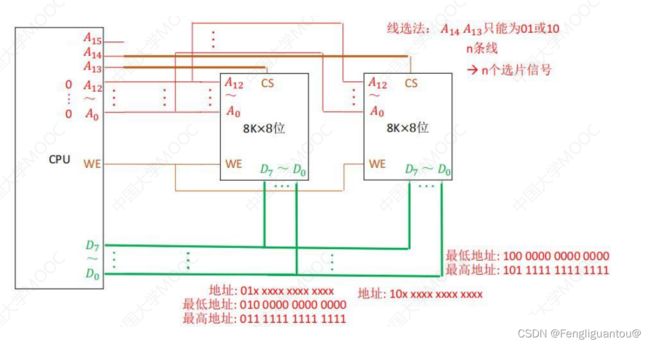

( 1 ) (1) (1)线选法

优点:不需要片选地址译码器,线路简单。

缺点:地址空间不连续,不能充分利用存储器的空间。(对此应该这样理解:第一,体号地址不连续导致CPU寻址不连续,第二因为每个存储器芯片/芯片组都需要单独一条片选线,但是片选线本质上使用的是CPU的地址线,所以可能导致一个问题,即存储器芯片组有多个,片选线不够用,所以造成地址资源的浪费。)

注:线选法的片选线默认是使用高位的地址线。

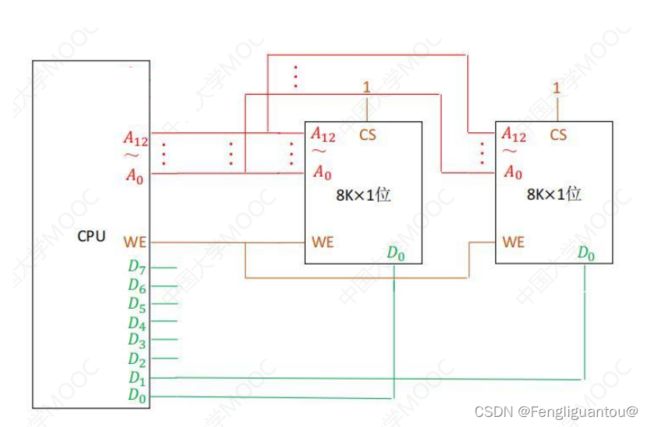

假设在下图中有两个独立的芯片组,其中两个芯片组分别连接了两条地址总线作为片选信号,由于CPU每次只能让一个芯片组进行工作,所以两条地址总线只能具有两种有效的组合:即01或者10,只有这两种方式才能只让一块芯片进行工作

如何深入理解地址不连续?

进行访存的时候,我们给一个地址。其中假设四个存储器芯片,在线选法下,前4位就代表选择哪一个存储器芯片。例如1000表示第一个。这样对于编程而言会出现问题,即如果想要访问1100…实际上是没有这个存储器芯片的。

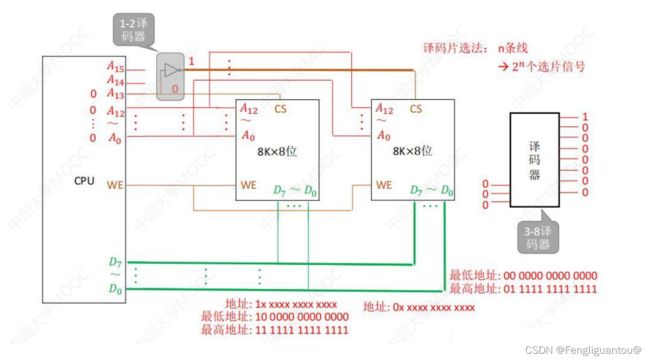

( 2 ) (2) (2)译码片选法

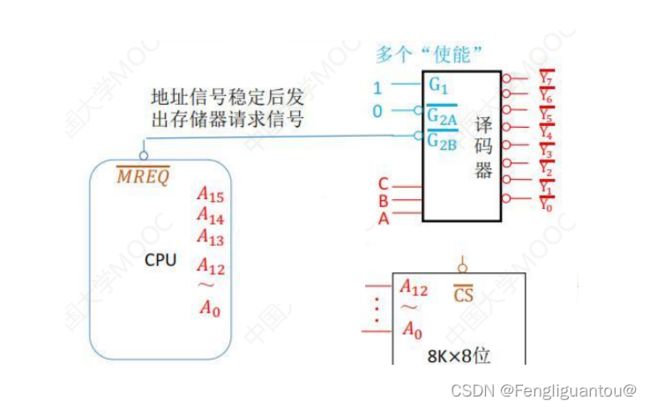

译码片选法:使用地址总线连接译码器,地址总线将片选信号发送给译码器,译码器对其进行翻译,然后导通对应芯片组的片选线。

优点:n条地址线可以控制 2 n \color{red}{2^n} 2n个芯片组的片选信号。并且因为体号中所有组合都是有效的,所以地址是连续的。

译码片选法默认使用高位的地址总线来作为片选线。

片选线的条数说明了什么?

片选线的条数说明了芯片组的个数,说明了有多少个芯片组。

优化思路:

在多余的地址线传输过程中加上一个非门,也就是这里的1-2译码器,所以一条地址线就可以对应发出两个片选信号。

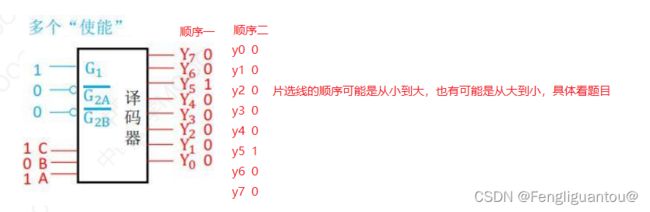

在这个基础上继续优化,3-8译码器的出现,3-8译码器似乎会复杂一点,3条地址线可以对应8种状态,所以可以

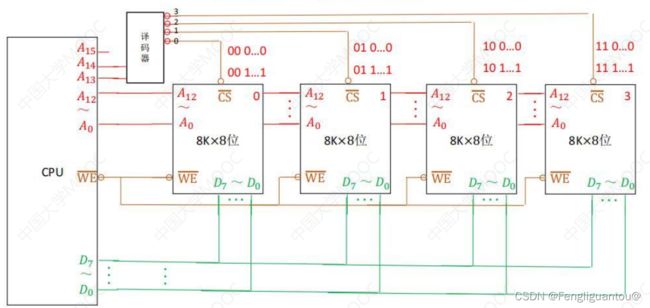

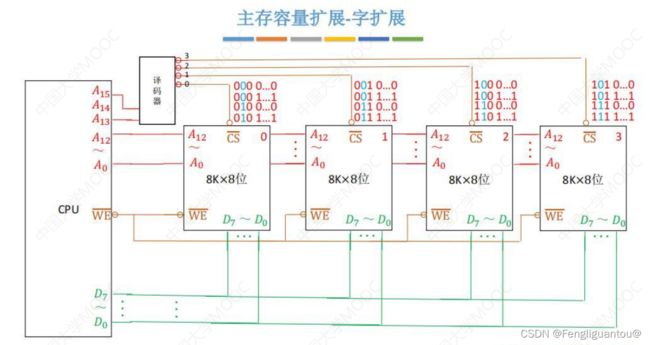

通过这种优化思路以后,主存内的地址就是连续的了,例如00开头的地址对应第一个存储器芯片,01对应第二块存储器芯片,接着是10,11。CPU可以搭配片选信号选择使用的存储器芯片。

下图需要注意的是,第二块存储器芯片和后面的存储器芯片的地址并不是从第一块存储器芯片转发来的,而是从连接第一块存储器芯片的地址总线传递来的,为了不让图片很乱,所以下图就没有这样画。

需要非常注意,不同的存储器芯片,即使用不同片选信号的存储器芯片,其一定是使用不同的读写控制电路,这很好理解,如果是相同的读写控制电路,那如何控制多块不同的芯片写入。

⭐⭐⭐⭐⭐⭐

需要注意的是,在题目中,可能会出这种脑瘫的连接方式:

即连接片选译码器的地址线不是连续的,中间空了一条。

这种接法会导致一个问题:我们看第一个芯片A,,其正常地址范围是12个0到12个1,即

2 1 2 \color{red}{2^12} 212 个地址,但是如果中间缺了一条线,就会导致出现 2 1 3 \color{red}{2^13} 213个地址,这明显是具有问题的。 但是这个其实不影响寻址。这个就是个nt玩意。

注意:字扩展是将不同存储器芯片的地址总线,数据线,读写控制线共用,但是片选线不共用,并且字扩展就是类似高位交叉编址和低位交叉编址,可以这样记忆,但是记住其不是高位交叉编址和低位交叉编址,只要记住有体号即可。

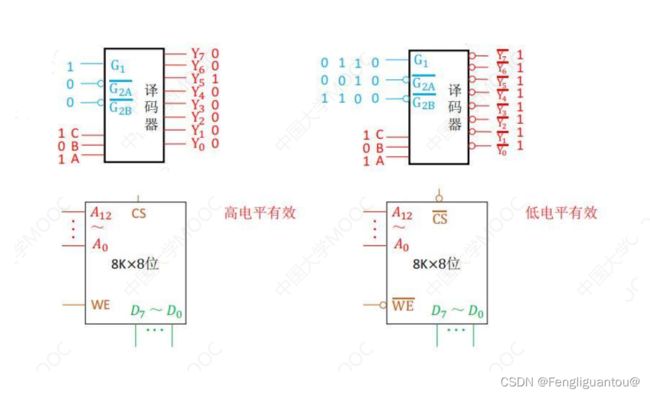

需要非常注意的是,题目中的片选译码器可能不是一个3-8译码器之类的译码器,题目可能给了实际的电路,然后给了片选地址,让你分析这个片选地址是否合理:我们判断片选是否合理就是看片选经过电路以后,产生的0或者1信号是否能够导通一个芯片组,因为如果我们这个片选地址没法导通任何一个芯片,那就说明这个地址无效的,所以这类题目我们一般是通过电路然后根据片选地址判断出译码器得到的片选信号和芯片需要的片选信号是否相同。

例如下面的这题:

字位同时扩展

两个特征:

位扩展的存储器共用一个片选信号。

字扩展不同的存储器芯片共用数据总线和地址总线。

字扩展和位扩展中地址线,数据线,读写控制线,片选线的共用

( 1 ) (1) (1)字扩展

同用地址线,读写控制线,片选线。

( 2 ) (2) (2)位扩展

同用地址线,数据总线,读写控制线(这里应该理解为因为每次访存只需要一块存储器芯片工作,所以可以大家共用,因为其他的存储器芯片接收到读写信号也没关系,其片选信号没有被导通是无法工作的。)

字扩展和交叉编址的区别

首先需要知道,字扩展和交叉编址是具有区别的。

( 1 ) (1) (1)片选线的选择

字扩展中无论是线选法还是译码器片选法都是使用的高位地址总线。

而在交叉编址中,既有使用高位,也有使用低位。

( 2 ) (2) (2)译码器

字扩展中一个存储器芯片一个译码器。

交叉编址中译码工作一般是交付给第一个存储器芯片或者最后一个存储器芯片。

存储器容量相除以后得到的结果

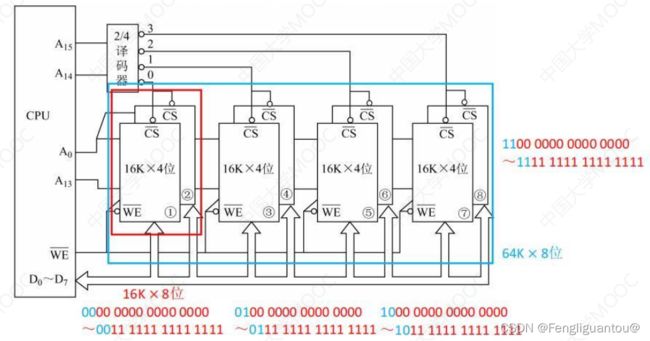

在存储器容量中 64 K × 8 \color{red}{64K \times 8} 64K×8意思是有64K个存储单元,每个存储单元是8bit。存储单元的个数说明了地址线的条数, 地址线的位数。

存储器容量相除:例如 64 K × 8 \color{red}{64K \times 8} 64K×8 / 32 K × 4 \color{red}{32K \times 4} 32K×4相除得到的结果就是需要有多少块这样的芯片才能扩展成这样。其中8/4=2说明在 64 K × 4 \color{red}{64K \times 4} 64K×4 情况下每个芯片组需要两个存储器芯片,64K/32K=2,说明在 32 K × 8 \color{red}{32K \times 8} 32K×8的情况下,需要两个存储芯片组,根据存储芯片组可以推出片选的条数,所以最终可以得出需要2*2=4个芯片。所以如果题目问需要几个这样的存储器芯片,可以直接使用存储器容量进行相除。