FPGA学习思考过程记录:一

目录

目录

目录

概述

VIVADO工程文件结构

FPGA基本开发流程

什么是IP

为什么要仿真

RTL ANALYSIS

SYNTHESIS

IMPLEMENTATION

可执行文件

bit 和 bin 区别

概述

最近开始做高速ADC采集的项目,会使用到FPGA作为高速电路以及算法处理的中心,之前断断续续也接触过一点FPGA的知识。现在算是正式将其运用到项目中。在这个项目推进的过程中,陆续有一些心得体会,主要是自己过程中的疑惑解答,记录在这里。方便日后的回顾。

VIVADO工程文件结构

VIVADO软件已经为我们配置好了工程内部需要的所有文件类型,并且分门别类地放置好了位置,因此,我们只需要按照他的定义来使用就行了。

具体每个文件夹的内容如下:

project_name.cache:Vivado 软件的运行缓存

project_name.hw:所有波形文件

project_name.ip_user_files:用户关于 IP 的文件

project_name.runs:编译与综合结果,.\impl_1 文件夹中的.bin 和 .bit 即为编译生成的可执行文件

project_name.sdk:SDK 环境代码,一般是 ZYNQ 设计中关于 PS 端的代码

project_name.sim:仿真结果

project_name.srcs:所有用户编写的源码、仿真文件与约束文件

project_name.tmp:自制 IP 核时的临时工程文件夹,IP 核设计完成后会自动清理

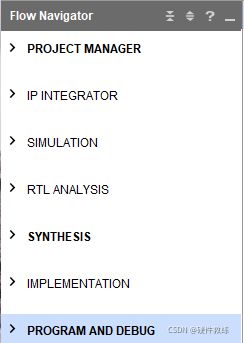

FPGA基本开发流程

FPGA开发流程,在IDE软件中已经按照步骤归纳好。大部分的开发流依照下面的流程进行即可。

什么是IP

IP(知识产权)核将一些在数字电路中常用,但比较复杂的功能块,如 FIR滤波器 、SDRAM控制器、PCI接口等设计成可修改参数的模块。IP核的重用是设计人员赢得迅速上市时间的主要策略。随着CPLD/FPGA的规模越来越大,设计越来越复杂(IC的复杂度以每年55%的速率递增,而设计能力每年仅提高21%),设计者的主要任务是在规定的时间周期内完成复杂的设计。调用IP核能避免重复劳动,大大减轻工程师的负担,因此使用IP核是一个发展趋势。

为什么要仿真

这里主要有一个疑问,就是为什么FPGA在仿真阶段花费了大量的时间,以及有专门的的仿真软件存在。

这里摘抄网络上的理解:仿真可以让设计者能够很快知道模块输出值是否正确。说到这,就有读者想问,直接上板子不是更快吗?如果你以后的工作都是用FPGA来跑流水灯,点数码管的话,那么直接上板子确实是比较快。但是笔者相信,不会有哪个公司要求你用FPGA仅仅是跑个流水灯的。如果设计者遇到稍微复杂一点的工程,注意笔者说的是稍微复杂一点,还不是很复杂。那么当您完成一次综合、布局布线、生成bit文件的时间超过半个小时是很正常的。当你发现效果不对,又返回来打算用个ChipScope插入寄存器查看怀疑对象,那么问题来了,你打算用ChipScope查看多少个寄存器值呢?ChipScope是利用FPGA内部资源来存储数据达到捕捉的功能,加入过大的ChipScope会使得布局布线更为困难,时间会更久。再者ChipScope存储量是有限的,不可能从时间0开始一直存储下去。存满了,下次再来就刷新了。从上面看开,如果不仿真,单纯的用ChipScope进行捕捉,每综合一次消耗大量的时间,再者ChipScope能观察到的信号有限,以及功能单一。这样一个流程下来,也许一天也未必能找到问题的所在,更别说处理问题了。

逻辑就是,简单的程序,直接运行看效果更佳直观,但是项目一旦复杂,或者内部的逻辑不能够通过外在的指示显示出来,这时候仿真的重要性就体现出来了。

RTL ANALYSIS

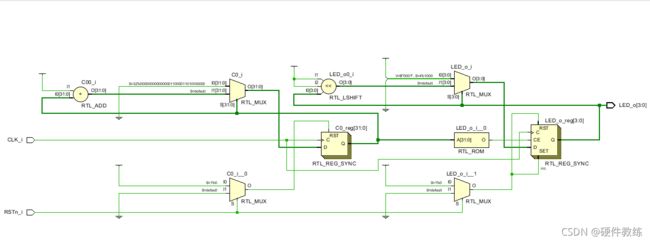

在集成电路设计中, register-transfer level(RTL)是用于描述同步数字电路操作的抽象级。

在RTL级,IC是由一组寄存器以及寄存器之间的逻辑操作构成。之所以如此,是因为绝大多数的电路可以被看成由寄存器来存储二进制数据、由寄存器之间的逻辑操作来完成数据的处理,数据处理的流程由时序状态机来控制,这些处理和控制可以用硬件描述语言来描述。

RTL级和门级简单的区别在于,RTL是用硬件描述语言(Verilog 或VHDL)描述理想达到的功能,门级则是用具体的逻辑单元(依赖厂家的库)来实现你的功能,门级最终可以在半导体厂加工成实际的硬件,一句话,RTL和门级是设计实现上的不同阶段,RTL经过逻辑综合后,就得到门级。

RTL描述是可以表示为一个有限状态机,或是一个可以在一个预定的时钟周期边界上进行寄存器传输的更一般的时序状态机,通常VHDL/verilog两种语言进行描述。

比如下图就是一个流水灯RTL结果,这个是无法直接在电路中实现的,需要经过逻辑综合之后,才可以得到能够被实施在电路中的门级电路。

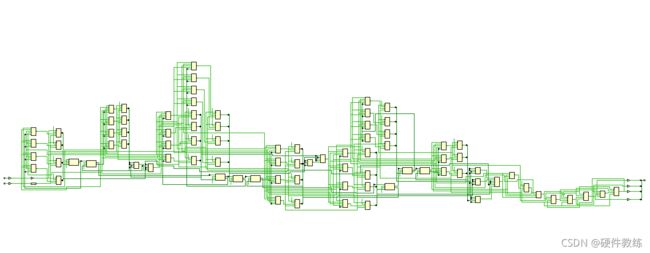

SYNTHESIS

我们常说的综合是逻辑综合即将RTL级转化为门级网表,比如上图的RTL级综合后得到下面的门级电路。

IMPLEMENTATION

上图的综合,只是表明了具体每个门之间的逻辑连接关系,但是对应到FPGA内部具体的电路,还没有确定。因此,实现的目的就是将门电路映射到目标器件的实体中。

计实现是利用FPGA厂商的实现工具把综合后的逻辑映射到目标器件结构的资源中,决定逻辑的最佳布局,选择逻辑与输入输出功能连接的布线通道进行连线,并产生相应的文件(如配置文件和相关报告)。通常可以为如下五个步骤。

1.转换:将多个设计文件进行转换并合并到一个设计库文件中。

2.映射:将网表中的逻辑门映射成物理元素,即把逻辑设计分割到构成可编程逻辑阵列内的额可配置逻辑块与输入输出块及其他资源中的过程。

3.布局布线: 布局是指从映射取出定义的逻辑和输入输出块,并把它们分配FPGA内部的物理位置,通常基于某种先进的算法来完成;布线是指利用自动布线软件使用布线资源选择路径试着完成所有的逻辑连接。可以使用约束条件操作布线软件,完成设计规定的性能要求。在布局布线过程中,可同时提取时序信息形成报告。

4.时序提取:产生一反标文件,供给后续的时序仿真使用。

5.配置:产生FPGA配置时需要的位流文件

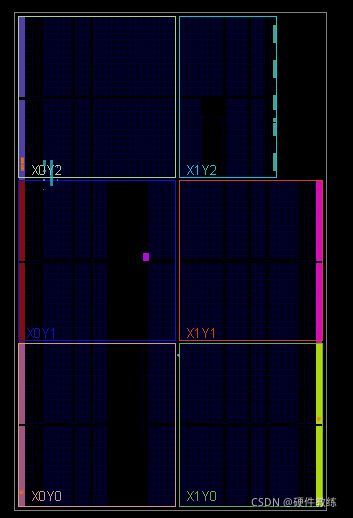

比如下图就是FPGA使用的具体资源的缩略图

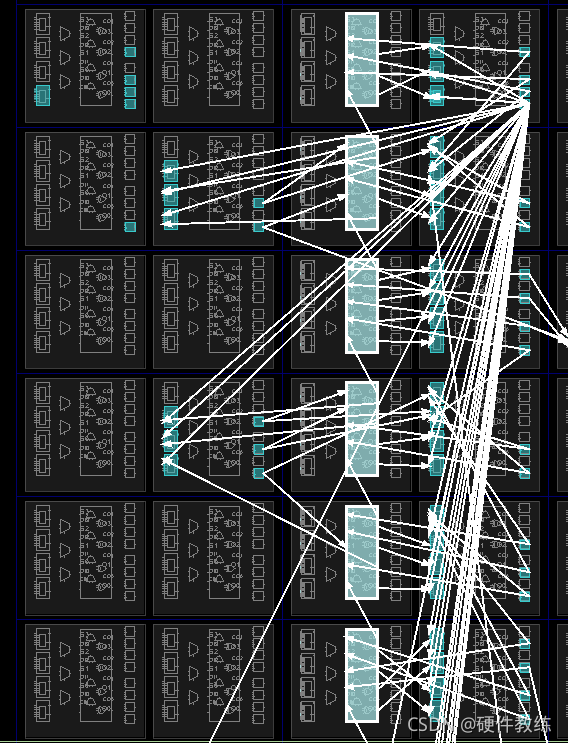

下面是具体使用了哪些LUT进行布线。其中还可以看出具体的连接是什么,比如下图中的白线所示。

可执行文件

FPGA最终下载到芯片内部的文件分为几类:*.bit, *.mcs, *.bin 和 *.elf。具体含义解释如下

BIT文件

bit 文件一般用于JTAG在线进行调试的时候,是把bit文件是烧写到FPGA中进行在线调试。

BIN文件

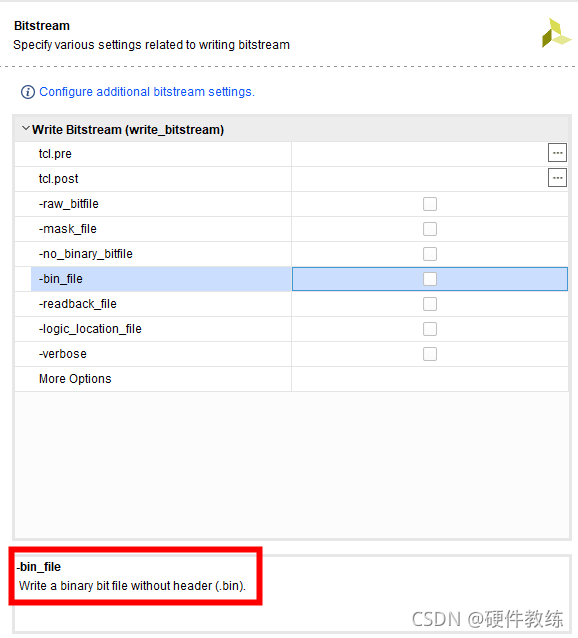

bin 文件是二进制文件,按顺序只包含原始字节流,烧写进flash,上电加载自动加载。FPGA一般默认生成的是bit文件,bin文件生成是在property里勾选的,如下图所示。

UltraEdit 查看 bin 和 bit 文件区别

可以看到bit文件比bin文件多了文件信息:比如工程名,User_ID,工具的版本信息(下图给的是vivado 2015.4),FPGA芯片型号(下图为7k325tffg900),bit生成日期(下图为2019/10/09)等信息。

MCS文件

mcs也是烧写到flash中的,上电后会自动加载到FPGA里,因此烧写进flash,需要断电重启。mcs文件是其中两个ASCII字符用于表示数据的每个字节HEX文件。mcs文件除了包含头部信息外还有地址信息以及校验码。

因此,MCS文件的效率似乎较低,因为它需要2个字节来表示1个字节。但是它有两个优点:

- 在每行的末尾都有一个校验和以确保完整性。

- 每行包括该行应位于内存中的地址

elf文件

如果FPGA中用到 microblaze 或者 ZYNQ 的结构,还会有一个 elf 文件,这是因为其继承了 ARM 的可执行文件。

ARM 体系中,所有文件均采用的 ELF 文件格式。ARM 中的各种源文件(包括汇编文件,C 语言程序及 C++ 程序等)经过 ARM 编译器编译后生成 ELF 格式的对象文件(Object File)(.o文件)。这些对象文件(Object File)和相应的 C/C++ 运行时用到的库经过 ARM 连接器处理后,生成 ELF 格式的镜像文件(image),这种ELF 格式的映像文件是一种可执行文件,可被写入嵌入式设备的 ROM 中。

可执行文件存放

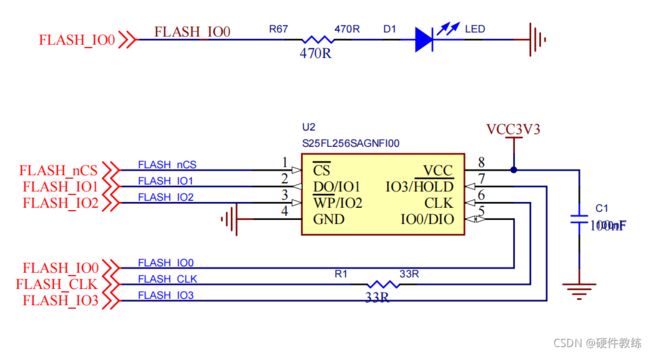

FPGA板卡一般会自带FLASH,用于在上电的时候读取程序。如果烧录的是BIT或者BIN文件,掉电后不会保存。

MCS文件可以下载到FLASH中,每次上电后,FPGA可以读取FLASH内部的程序。