Introduction To AMBA 简单理解

文章目录

-

- 前言

- 简介

- AMBA 的演进

-

-

- AMBA的进化历史

- AMBA 演进图解

- AMBA specifications

-

- AMBA1.0

-

-

- 1.1 Introduction to AMBA

- 1.2 AMBA Specification

-

-

- 1.2.1ASB

- 1.2.2 APB

- 1.2.3 ASB VS APB

- 1.2.4 External interface 中的 TIC(Test Interface Controller) 功能

-

- 1.3 总结

- 1.4 Appendices

-

-

- 1.4.1 Document references

- 1.4.2 AMBA-related products and support

-

-

- AMBA 各个版本是怎么处理 Coherency 的

- ACE 和 CHI 的区别

- cortex-a57 cortex-a53 与 AMBA

前言

之前在 很多文章都都提及到 AMBA ,知道 它是 ARM 的 总线实现,且是一个非常重要的组成部分

- soc(一) soc核心组件

- soc(八) 总线

- 处理器架构 (九) arm soc 文档

- ARM 处理器 总览

这些文章都是只提及了AMBA ,但是没有介绍.

最近在熟悉 ARM 内存模型 中的 shareability 的概念时, 涉及到了 ACE , ACE 就是 AMBA 总线的内容.

并且发现 从 AMBA 层面 理解 shareability 更为有效.

另外,公司的芯片中也有很多总线,然后访存的时候,涉及到总线,我总是忽略了.

综上,打算学习一下 AMBA 总线.了解总线设计

第一步,是 总线的功能 , 以及接口

第二步,是 总线概念与各种ARMv8概念对接

第三步,是 总线的内部实现

简介

AMBA 是 ARM 独有的总线名称, x86/rv的没有了解过,TODO

AMBA 用来连接 ARM 的 各个IP , 例如 cpu dma 外设

当CPU访存的时候,数据就会在总线中流动 . 当然,总线不只是提供数据流动,还要处理很多负责的事情,例如冲突 一致性 等问题需要总线处理.

我基于 DVI0010.pdf ,先简单理解一下 AMBA . 这份文档很老了,而且只有一个版本的release,是 1996年的.那就先了解一下的1996年的 AMBA(AMBA1)设计吧.

AMBA 的演进

AMBA的进化历史

- 进化历史

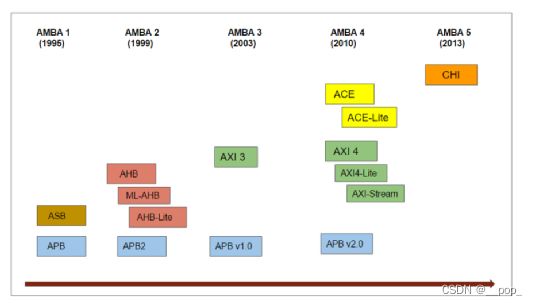

AMBA 演进图解

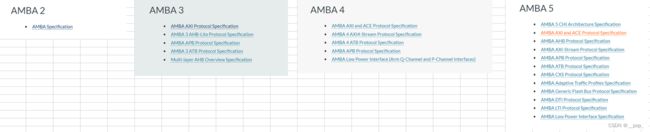

AMBA specifications

| AMBA 1(1996) | 手册编码 | AMBA 2(1999) | 手册编码 | AMBA 3(2003) | 手册编码 | AMBA 4(2010) | 手册编码 | AMBA 5(2013) | 手册编码 |

|---|---|---|---|---|---|---|---|---|---|

| Introduction To AMBA | dvi0010/a | AMBA Specification | ihi0011/a | AMBA 5 CHI Architecture Specification | ihi0050/E.b | ||||

| AMBA AXI Protocol Specification | ihi0022/b | AMBA AXI and ACE Protocol Specification | ihi0022/e | AMBA AXI and ACE Protocol Specification | ihi0022/H.c | ||||

| AMBA 4 AXI4-Stream Protocol Specification | ihi0051/a | AMBA AXI-Stream Protocol Specification | ihi0051/B | ||||||

| AHB | AMBA 3 AHB-Lite Protocol Specification | ihi0033/a | AMBA AHB Protocol Specification | ihi0033/C | |||||

| Multi-layer AHB Overview Specification | dvi0045/2 | ||||||||

| APB | APB | AMBA APB Protocol Specification | ihi0024/b | AMBA APB Protocol Specification | ihi0024/c | AMBA APB Protocol Specification | ihi0024/D | ||

| AMBA 3 ATB Protocol Specification | ihi0032/a | AMBA 4 ATB Protocol Specification | ihi0032/b | AMBA ATB Protocol Specification | ihi0032/C | ||||

| AMBA Low Power Interface (Arm Q-Channel and P-Channel Interfaces) | ihi0068/c | AMBA Low Power Interface Specification | ihi0068/D | ||||||

| AMBA CXS Protocol Specification | ihi0079/B | ||||||||

| AMBA Adaptive Traffic Profiles Specification | ihi0082/A | ||||||||

| AMBA Generic Flash Bus Protocol Specification | ihi0083/A.b | ||||||||

| AMBA DTI Protocol Specification | ihi0088/E.b | ||||||||

| AMBA LTI Protocol Specification | ihi0089/A.b | ||||||||

| ASB | ASB |

AMBA1.0

1.1 Introduction to AMBA

AMBA是一种片上总线规范,用于将宏单元(如CPU、DSP、外围设备和内存控制器)连接在一起,形成微控制器或复杂的外围芯片。

之所以将AMBA独立出来,作为一个专门的技术,是因为想要达成这些目标

•促进具有一个或多个CPU/信号处理器和多个外围设备的嵌入式微控制器的“首次正确”开发

•最大限度地减少片上总线和片外制造测试访问所需的硅开销

•独立模块技术:

-在广泛的集成电路工艺中提高外围和系统宏单元的可重用性

-以适合全定制、标准单元和门阵列技术的方式

•缩短上市时间,促进芯片系列路线图。AMBA鼓励模块化设计和处理器独立性,有助于外围库的开发,并允许随时使用先进的缓存CPU核。

为了达成这些目标,该体系结构具有以下关键特征:

•高度模块化

•多主机支持

•低功耗强调

•创新的测试方法

license 相关

AMBA规范是开放的。

任何人都可以从ARM获得该规范的免费副本,并使用该协议设计芯片。

没有相关的许可证或特许权使用费

规范是开放的,但是rtl不是免费的

1.2 AMBA Specification

AMBA规范定义了:

•一种高速、高带宽总线,即高级系统总线(ASB)

•一种简单、低功耗的外围总线,即高级外围总线(ASP)

•访问外部测试仪,以允许对缓存RAM进行模块化测试和快速测试

•基本内务操作(重置/通电、初始化和断电)

- ASB

Advanced System Bus

高性能总线是主系统的“主干”。该总线还能够维持外部总线接口所需的数据速率。

CPU和其他总线主机(如DMA控制器)以及高速本地内存通常连接到此总线。

(ASB通过桥连接到更简单的APB-见下文)

- APB

简单、低速、低功耗的外围总线。

这通常(但并非总是)是一条较窄的总线,并且设计为简单(即非管道化),用于连接许多常见的外围设备,

如计时器、并行i/O端口、UART等

(通过将这些不经常访问的外围设备放置在APB上,并将其从ASB中分离出来,可以减少ASB上的负载,并更容易实现ASB上的最大性能)

- External interface

一般用于 接外部内存

这也用于测试访问。(这通常是一个外部内存接口,但可以使用任何合适的引脚集。)

外部测试仪可以控制总线,并依次单独检查每个组件。

这种模块化方法促进了测试向量的可重用性。并行访问方法允许快速测试,尤其是缓存的CPU。

- 基本事务操作

基于AMBA的微控制器还包含重置和电源管理信息,以确保:

•单总线驱动器通电

•持续的省电或断电模式

•冷/温/看门狗重置的重置机制

1.2.1ASB

ASB设计用于高性能、高带宽使用:

•非多路复用(即独立)地址和数据总线

•支持流水线操作(包括仲裁)

•支持多个总线主机,硅开销低

•支持多个从设备,包括到外围总线(APB)的桥接器

•集中式解码器和仲裁器

绝对传输速率取决于许多设计因素,但出于比较目的,如果假设32位数据路径和100MHz时钟,则可以实现200字节/秒的速率。这些图不受规范限制,只是为了澄清。

通过使用总线请求、总线授权和总线锁定信号支持多个总线主控器。这些信号的使用是可选的;如果您只有一个总线主控器,则不会因实现这些总线控制线路而受到惩罚。

1.2.2 APB

APB设计为ASB的二次总线,通过桥接器连接(限制ASB负载)。APB是一种简单得多的总线,具有低功耗重点:

•数据访问仅由选择和选通控制(即无时钟,从而降低功率)

•总线未使用时,功耗几乎为零

•简单的未布线接口,是许多简单外围宏单元所需的典型接口。

数据传输速率取决于外围设备的速度。单个读取或写入周期需要5个时钟,因此假设32位数据路径和100MHz时钟,数据速率为80MB/s。这些图不受规范限制,只是为了澄清。可以更容易地优化APB的数据总线,以适合所连接的外围设备。许多外围设备具有狭窄的数据路径需求,一种机制可能是连接桥旁边的32位外围设备和最远的8位外围设备,从而减少总线所需的芯片面积。

虽然AMBA中未指定时钟策略,但桥接器和APB提供的分区确实为最小化功耗提供了一个良好的起点。许多外围设备(计时器、波特率发生器、pwm单元)需要一个向下划分的系统时钟,在电桥附近放置一个可编程的分频器既方便又省电。

APB中没有总线主控(除了网桥)。所有外围设备都充当从属设备。

1.2.3 ASB VS APB

ASB用于CPU、DSP、DMA控制器和其他总线主机,或高性能外围设备(通常带有FIFO)

APB用于非流水线、寄存器映射的从属外围设备,尤其是当外围设备数量较多且需要将功耗降至最低时

ASB和APB共享AMBA中包含的测试方法

1.2.4 External interface 中的 TIC(Test Interface Controller) 功能

测试接口控制器(TIC)是一个ASB总线主机,它使用外部总线接口(或其他合适的引脚)为外部测试设备提供测试访问。

该机制允许低门计数测试访问端口,提供快速并行访问,这对于测试缓存RAM至关重要。

这种测试方法允许在芯片之间重复使用测试向量,节省了宝贵的时间并降低了风险。例如,当重新使用外围宏单元时,测试向量模块(已以经验证的测试形式存在)可以重新使用,测试程序的上层仅在芯片之间特定。

1.3 总结

自1995年9月以来,AMBA规范一直保持稳定。这是一种经过验证的总线架构,已用于ARM7100和许多其他高集成度微控制器中。

AMBA成功解决了以下问题:

芯片架构

通过使设备能够一致地划分为高速、低功耗和生产测试部分。

项目管理

通过鼓励宏单元重复使用,从而减少开发时间和风险

产品路线

通过独立于技术和流程,并允许重新使用更新、更具竞争力的流程

生产测试

通过提供一种快速测试缓存RAM和以模块化方式重用测试向量的机制

ARM正在继续围绕AMBA开发支持工具和环境,包括第三方EDA工具供应商

参考 1.4.2

1.4 Appendices

1.4.1 Document references

AMBA Specification ARM IHI 0001 // 对应 AMBA 2

ARM7100 Data sheet ARM DDI 0035

ARM AMBA-peripheral data sheets ARM DDI 0017

ARM MicroPack data sheets ARM DDI 0014

ARM Reference Peripherals Specification ARM DDI 0062

1.4.2 AMBA-related products and support

ARM正在AMBA周围和之上发展广泛的支持,如下所示:

MicroPack微型封装

MicroPack是一组HDL模型,实现了一个示例AMBA系统和一个符合性测试套件。还包括将CPU连接到AMBA高速总线的各种包装器。ARM的许多合作伙伴已获得MicroPack许可,可以直接支持OEM。例如

•提供AMBA系统样本的HDL模型

•提供开发卡

•ARM和合作伙伴的外围设备集成。

开发卡Development card

这在PCB上实现了AMBA。该卡允许使用各种CPU(通过头卡),并在FPGA中原型化外围设备。

Peripheral Library 外围库

ARM正在开发越来越多的AMBA兼容外围设备,以加快高集成度微控制器的设计。这些外围设备特别适合PDA和网络计算机应用。

Consultancy咨询

ARM咨询集团拥有相当多的AMBA专业知识。该组已经调整了多个CPU以具有AMBA本机总线。其他专业知识包括实施AMBA兼容的外围设备,到设计具有基于AMBA的创新架构的高集成度微控制器。

Real-time ICE

ARM开发了一种使用AMBA的实时在线仿真器的创新概念,并获得了专利。实时ICE目前正在开发中,很可能在1997年第一季度以后提供。

3rd-Party

EDA工具供应商将宣布从1996年第4季度开始支持AMBA。

AMBA 各个版本是怎么处理 Coherency 的

在 AMBA2 和 AMBA1 协议中,没有硬件支持的缓存一致性(Cache Coherency)机制。因此,在这些协议中,处理一致性的问题是由系统设计人员通过软件来实现的。通常,这种软件实现的方式是通过在读写操作时进行同步,以确保多个处理器或设备访问同一内存区域时不会发生冲突。

在 AMBA2 和 AMBA1 中,可以使用一些软件技术来实现缓存一致性,例如使用锁(lock)或信号量(semaphore)等同步机制。这些技术可以确保多个处理器或设备访问同一内存区域时不会发生竞争条件和数据不一致的问题。但是,这种软件实现的方式通常会带来额外的开销和复杂性,并且在大型系统中可能会导致性能问题。

因此,在后续版本的AMBA协议中,ARM引入了硬件支持的缓存一致性机制,例如AXI3、ACE和CHI等协议。

ACE是在AXI3规范中引入的,而不是在AXI4中。

ACE(AXI Coherency Extensions)是在 AMBA3 协议中引入的,而不是在 AMBA4 中。AMBA3规范中引入了ACE-lite和ACE-full两种协议,这些协议增加了对硬件支持的缓存一致性(Cache Coherency)和内存一致性(Memory Coherency)的支持。AMBA4规范中则进一步扩展了ACE-lite和ACE-full协议,并引入了新的AXI4协议。

/*

在AXI3及之前的版本中,处理一致性的方式是通过在总线上进行广播(broadcast)和响应(response)来实现的。

这种方式被称为“总线嗅探”(bus snooping),它需要在总线上进行频繁的通信,因此在大型系统中可能会导致性能问题。

*/

https://aijishu.com/a/1060000000207840

ACE是AXI Coherency Extensions的缩写。

顾名思义,ACE就是AXI加上支持一致性的扩展.

之前是怎么处理 Coherency 的

关于AXI规范的详细信息,可以参考ARM官方文档《AMBA AXI and ACE Protocol Specification》。

而在ACE和CHI协议中,引入了目录(directory)和Snoop Filter等新的技术,可以更加高效地处理一致性。

https://aijishu.com/a/1060000000220025

ACE 和 CHI 的区别

CHI uses a similar coherency model to ACE,

adding support for snoop filters and directory-based systems for snoop scaling.

增加了 监听过滤器, 和 基于目录的系统 , 以减少监听范围

cortex-a57 cortex-a53 与 AMBA

我关注的硬件架构 为 armv8, 微架构 cortex-a57

The Cortex-A57 processor complies with the:

• AMBA 4 AXI Coherency Extensions (ACE) protocol if the processor memory interface implements an ACE bus interface.

See the ARM® AMBA® AXI and ACE Protocol Specification.

• AMBA 4 Advanced eXtensible Interface (AXI) protocol for the Accelerator Coherency Port (ACP) slave interface.

See the ARM® AMBA® AXI and ACE Protocol Specification.

• AMBA 3 Advanced Peripheral Bus (APB) protocol.

See the ARM® AMBA® APB Protocol Specification.

• AMBA 3 Advanced Trace Bus (ATB) protocol.

See the ARM® AMBA® 3 ATB Protocol Specification.

The processor complies with the CHI architecture if the memory interface implements a CHI bus

interface.

The Cortex-A53 bus interface natively supports one of:

• AMBA 4 ACE bus architecture.

See the Arm® AMBA® AXI and ACE Protocol Specification AXI3, AXI4, and AXI4-Lite, ACE and ACE-Lite.

• AMBA 5 CHI bus architecture.

See the Arm® AMBA® 5 CHI Protocol Specification.

看起来cortex-a53/a57 都要有

ATB 和 APB 和 AXI

ACE/CHI 两者选其一