简单8位CPU设计verilog微处理器,源码/视频

名称:8位CPU设计微处理器

软件:QuartusII

语言:Verilog

代码功能:

设计一个简单的处理器,可以实现加减法以及简单的逻辑运算。

设计包括程序计数器电路,指令存储器电路,指令译码器电路(控制器),运算电路,数据存储器(寄存器)电路。

演示视频:http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=213

FPGA代码Verilog/VHDL代码资源下载网:www.hdlcode.com

代码下载:

8位CPU设计微处理器 软件:QuartusII 语言:Verilog 代码功能: 设计一个简单的处理器,可以实现加减法以及简单的逻辑运算。 设计包括程序计数器电路,指令存储器电路,指令译码器电路(控制器),运算电路,数据存储器(寄存器)电路。名称:8位CPU设计(代码在文末付费下载)软件:QuartusII语言:Verilog代码功能: 设计一个简单的处理器,可以实现加减法以及简单的逻辑运算。 设计包括程序计数器电路,指令存储器电路,指令译码器电路(控制器),运算电路,数据存储器(寄存器)电路。演示视频:FPGA代码Verilog/VHDL代码资源下载网:www.hdlcode.com部分代码展示`timescale 1n![]() http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=213

http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=213

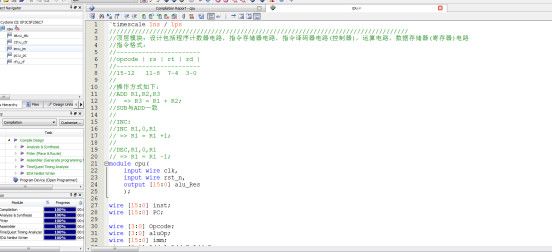

部分代码展示

`timescale 1ns / 1ps / //顶层模块:设计包括程序计数器电路,指令存储器电路,指令译码器电路(控制器),运算电路,数据存储器(寄存器)电路 //指令格式: //----------------------- //opcode | rs | rt | rd | //----------------------- //15-12 11-8 7-4 3-0 // //操作方式如下: //ADD R1,R2,R3 // => R3 = R1 + R2; //SUB与ADD一致 // //INC: //INC R1,0,R1 // => R1 = R1 +1; // //DEC,R1,0,R1 // => R1 = R1 -1; module cpu( input wire clk, input wire rst_n, output [15:0] alu_Res ); wire [15:0] inst; wire [15:0] PC; wire [3:0] Opcode; wire [3:0] aluOp; wire [15:0] imm; wire [3:0] Addr1,Addr2,Addr3; wire [15:0] Write_data; wire [15:0] Read_data1,Read_data2; wire [15:0] aluRes; wire [15:0] input1,input2; wire writereg; assign Opcode = inst[15:12]; //操作码为指令的高四位 assign Addr1 = inst[11:8];//操作数1地址 assign Addr2 = inst[ 7:4];//操作数2地址 assign Addr3 = inst[ 3:0];//目的寄存器地址 assign Write_data = aluRes; assign input1 = Read_data1; assign input2 = Read_data2; assign alu_Res=aluRes; //指令存储器例化 im u_im( .Addr(PC), .inst(inst) ); //指令译码器例化 ctr u_ctr( .Opcode(Opcode), .aluOp(aluOp), .writereg(writereg) ); //数据存储器例化 rf u_rf( .clk(clk), .rst_n(rst_n), .Addr1(Addr1), .Addr2(Addr2), .Addr3(Addr3), .Write_data(Write_data), .writereg(writereg), .Read_data1(Read_data1), .Read_data2(Read_data2) ); //程序计数器电路例化 pc u_pc( .clk(clk), .rst_n(rst_n), .current_pc(PC) ); //运算电路例化 alu u_alu( .aluOp(aluOp), .input1(input1), .input2(input2), .aluRes(aluRes), .Zero(Zero) ); endmodule

设计文档:

设计文档.doc

1. 工程文件

2. 程序文件

3. 程序编译

4. RTL图

5. Testbench

6. 仿真图

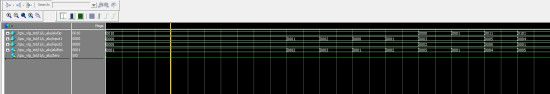

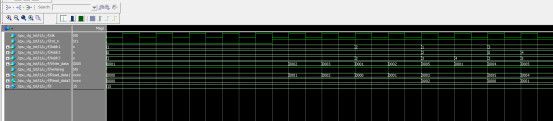

顶层仿真图

//微程序内容如下:

//2101 # INC R1 结果:R1 =1

//2101 # INC R1 结果:R1 =2

//2101 # INC R1 结果:R1 =3

//2202 # INC R2 结果:R2 =1

//2202 # INC R2 结果:R1 =2

//0123 # ADD R1,R2,R3 结果:R3 =2 + 3 = 5

//1124 # SUB R1,R2,R4 结果:R4 =3 -2 =1

//3303 # DEC R3 结果:R3 =5 -1 = 4

//5345 # OR R3,R4,R5 结果:R5 =4 | 1 = 5

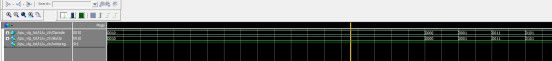

运算器仿真

控制器仿真

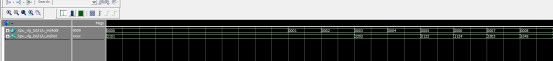

指令存储器仿真

程序计数器仿真

寄存器组仿真