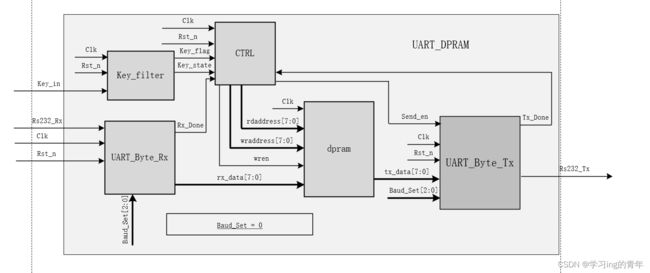

FPGA串口收发+按键+双口RAM组成的简易系统设计

实验现象:通过串口发送数据到FPGA中,FPGA接收到数据后将数据存储在双口ram的一段连续空间中,通过Quartus II软件提供的In-System Memory Content Editor工具查看RAM中接收到的数据。当需要时,按下按键0,则FPGA将RAM中存储的数据通过串口发送出去。

知识点:

1、Altera公司Cyclone IV系列器件的内部结构

2、存储器IP核的使用

3、In-System Memory Content Editor内存查看工具的使用。

4、串口收发+按键+双口RAM组成的简易系统设计

顶层代码

module UART_DPRAM(

Clk,

Rst_n,

Key_in,

Rs232_Rx,

Rs232_Tx

);

input Clk;

input Rst_n;

input Key_in;

input Rs232_Rx;

output Rs232_Tx;

wire Key_flag;

wire Key_state;

wire Rx_Done;

wire Tx_Done;

wire Send_en;

wire [7:0]rdaddress,wraddress;

wire wren;

wire [7:0]rx_data,tx_data;

uart_byte_tx uart_byte_tx(

.Clk(Clk),

.Rst_n(Rst_n),

.data_byte(tx_data),

.send_en(Send_en),

.baud_set(3'd0),

.Rs232_Tx(Rs232_Tx),

.Tx_Done(Tx_Done),

.uart_state()

);

uart_byte_rx uart_byte_rx(

.Clk(Clk),

.Rst_n(Rst_n),

.baud_set(3'd0),

.Rs232_Rx(Rs232_Rx),

.data_byte(rx_data),

.Rx_Done(Rx_Done)

);

key_filter key_filter(

.Clk(Clk),

.Rst_n(Rst_n),

.key_in(Key_in),

.key_flag(Key_flag),

.key_state(Key_state)

);

dpram dpram0(

.clock(Clk),

.data(rx_data),

.rdaddress(rdaddress),

.wraddress(wraddress),

.wren(wren),

.q(tx_data)

);

CTRL CTRL(

.Clk(Clk),

.Rst_n(Rst_n),

.Key_flag(Key_flag),

.Key_state(Key_state),

.Rx_Done(Rx_Done),

.Tx_Done(Tx_Done),

.rdaddress(rdaddress),

.wraddress(wraddress),

.wren(wren),

.Send_en(Send_en)

);

endmodule

CTRL

module CTRL(

Clk,

Rst_n,

Key_flag,

Key_state,

Rx_Done,

Tx_Done,

rdaddress,

wraddress,

wren,

Send_en

);

input Clk;

input Rst_n;

input Key_flag;

input Key_state;

input Rx_Done;

input Tx_Done;

output reg[7:0]rdaddress;

output reg[7:0]wraddress;

output wren;

output reg Send_en;

assign wren = Rx_Done;

reg do_send; //

reg r0_send_done,r1_send_done;

always@(posedge Clk or negedge Rst_n)

if(!Rst_n)

wraddress <= 8'd0;

else if(Rx_Done)

wraddress <= wraddress + 1'b1;

else

wraddress <= wraddress;

always@(posedge Clk or negedge Rst_n)

if(!Rst_n)

do_send <= 1'd0;

else if(Key_flag && !Key_state)

do_send <= ~do_send;

always@(posedge Clk or negedge Rst_n)

if(!Rst_n)

rdaddress <= 8'd0;

else if(do_send && Tx_Done)

rdaddress <= rdaddress + 8'd1;

else

rdaddress <= rdaddress;

always@(posedge Clk or negedge Rst_n)

if(!Rst_n)begin

r0_send_done <= 1'b0;

r1_send_done <= 1'b0;

end

else begin

r0_send_done <= (do_send && Tx_Done);

r1_send_done <= r0_send_done;

end

always@(posedge Clk or negedge Rst_n)

if(!Rst_n)

Send_en <= 1'b0;

else if(Key_flag && !Key_state)

Send_en <= 1'b1;

else if(r1_send_done)

Send_en <= 1'b1;

else

Send_en <= 1'b0;

endmodule