AXI总线介绍

AXI总线介绍

参考文档:

- UG761-AXI Reference Guide(v14.3)

- AXI入门

- 深入AXI总线(一)

- 深入AXI总线(二)

AXI是什么?

axi是一种总线协议,他是ARM AMBA(Advanced Microcontroller Bus Architecture)中最重要的一部分,是一种面向高性能、高带宽、低延迟的片内总线。它的地址/控制和数据相位是分离的,支持不对齐的数据传输,同时在突发传输中,只需要首地址,同时分离的读写数据通道、并支持Outstanding传输访问和乱序访问,并更加容易进行时序收敛。目前Xilinx的7系列FPGA中使用的均是AMBA4.0中的AXI协议。

AXI4总线有三种类型:

- AXI4用于高性能内存映射(Memory-Mapped)型的通信上。

- AXI4-Lite用于简单低吞吐量的内存映射型通信上(比如简单的寄存器读写)。

- AXI4-Stream用于高速的数据流传输,无需地址管理。

从以上介绍和实践开发来看,AXI4主要用于大块的数据读写,如DDR、BRAM的数据搬移;AXI4-Lite主要用于外设模块的配置,状态寄存器的读写等;而AXI4-Stream主要用于高速数据的传输,如高速AD数据、视频数据等的传输。

AXI工作原理

总体架构

AXI协议是一个点对点的传输协议。总线两端发起读写事务的一端称为主设备(Master),响应事务的一端是从设备(Slave)。点对点传输意味着本条总线只能用于两个设备间通信,和SPI等接口不一样,不存在片选从设备这样的机制。那你肯定会问,那如果主设备想访问多个从设备该怎么办?或者某个从设备需要被多个主设备访问该怎么办?这就需要AXI总线中一个重要的设备:中央互联(Interconnect)。一般来说,系统中的电路结构如下图所示:

传输通道

AXI4 总线的一大特征是它有 5 个独立的传输通道,这些通道都只支持单向传输。单向传输的通道意味着两端的终端节点是有身份差距的,好比水只能从上游流到下流。在 AXI 总线传输中,通道两端分为 Master 主机与 Slave 从机,主机总是发起读写请求的一方。常见的主机有CPU、DMA,而存储介质控制器(比如 DDR 控制器)则是典型的从机。主机可能通过从机读取或者写入存储介质。而显然从机不可能主动向 CPU 写入数据。

通道的读/写定义都是根据主机来定义的,这五种通道是:

- 读地址通道 (ARC) read address channel

- 读数据通道 (RC) read data channel

- 写地址通道 (AWC) write address channel

- 写数据通道(WC) write data channel

- 写回复通道 (RC) write response channel

读写传输操作

AXI4的一次读写传输操作中支持最多256个data transfers,而在AXI4-lite中每次读写传输操作只支持一个data transfer。

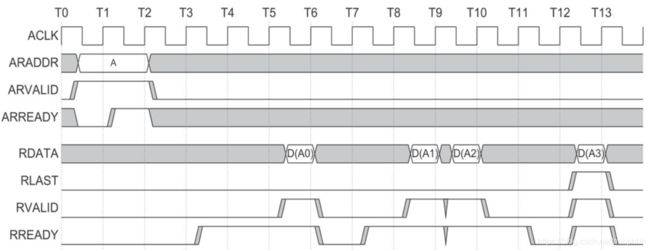

read transaction:

[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-w3lhdmmb-1622445062334)(/home/xsx/.config/Typora/typora-user-images/image-20210323170317141.png)]

write transaction:

[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-rQp9xxZT-1622445062336)(/home/xsx/.config/Typora/typora-user-images/image-20210323170440628.png)]

由上图可以看出,AXI4的数据和地址通道是独立的,所以它支持全双工的数据传输。在硬件层面,AXI4允许每组master-slave使用不同的时钟。

Valid/Ready握手机制

在上面讲到AXI4总线一共有5种独立的传输通道,这些传输通道使用同一种VALID/READY握手机制来进行通信。

在握手机制中,通信双方分别扮演发送方(Source)和接收方(Destination),两者的操作(技能)并不相同。

发送方置高 VALID 信号表示发送方已经将数据,地址或者控制信息已经就绪,并保持于消息总线上。

接收方置高 READY 信号表示接收方已经做好接收的准备。

其中ACLK为时钟信号

当双方的 VALID/READY 信号同时为高,在时钟 ACLK 上升沿,完成一次数据传输。所有数据传输完毕后,双方同时置低自己的信号。

所谓的双向流控机制,指的是发送方通过置起 VALID 信号控制发送的时机与速度,接收方也可以通过 READY 信号的置起与否控制接收速度。

发送方拥有传输的主动权,但接收方在不具备接收能力时,也能够置低信号停止传输,反压发送方。

VALID信号先到达

[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-Sr7AnNb0-1622445062339)(/home/xsx/.config/Typora/typora-user-images/image-20210329145044800.png)]

我发送方的VALID先置高,表示我已经准备好发送数据了,并且我已经 将数据放在消息总线上了,这时可能接收方还没准备好,它在T2

的时候才忙完,然后我置高READY信号,表示我现在可以接收数据了。这样以来,两者皆大欢喜,在时钟下一个的上升沿完成数据的传输,

然后同时置低双方的信号。

READY信号先到达

[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-T6YataSk-1622445062340)(/home/xsx/.config/Typora/typora-user-images/image-20210329145058649.png)]

现在情况反过来了,接收方现在很闲,而发送方很忙。这时,接收方的READY置高,表明其已做好接收数据的准备,而发送方在T2时刻才

忙完,将其VALID信号置高发送数据,在时钟下一个的上升沿完成数据的传输,然后同时置低双方的信号,一次传输完成。

VALID和READY同时到达

[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-kEVgFqG3-1622445062341)(/home/xsx/.config/Typora/typora-user-images/image-20210329145108911.png)]

这种情况最简单,两者同时置高,完成数据的传输。

注意,Valid信号一旦置高,它只有等待完成至少一次传输才能置低。

突发传输机制(Burst)

在 AXI 总线中的突发传输是指,在地址总线上进行一次地址传输后,进行多次数据传输(transfer),第一次地址传输中的地址作为起始地址,根据突发传输类型的不同,后续数据的存储地址在起始地址的基础上递增(INCR 模式);或者首先递增,到达上限地址后回到起始地址,继续递增(WRAP 模式);又或者后续数据都将不断写入起始地址,刷新起始地址上的数据。(FIXED 模式)

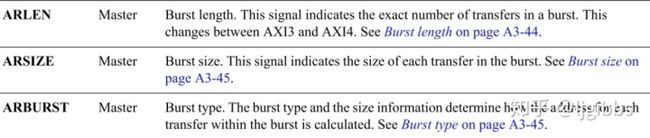

AXI4突发传输控制信息在地址通道上,随着第一次地址传输时写入,控制信息包括:

其中,ARLEN表示突发传输的长度,其实也就是支持多少个transfer。

ARSIZE表示每个transfer中的最大数据宽度。突发传输数据宽度不能超过数据线本身的宽度。当数据线本身宽度大于突发传输宽度时,将根据协议的相关规定制定数据在部分数据线上传输。

ARBURST表示传输的类型,包括INCR,WRAP,FIXED。

FIXED 类型适合对某个固定地址进行数据更新,比如向一个 almost full 的 fifo 更新数据。

INCR 类型最为常用,后续的数据的存储地址在初始地址的基础上,以突发传输宽度进行递增,适合对于 RAM 等 mapped memory 存储介质进行读写操作。

WRAP 模式比较特殊,除了初始地址外,还有最高地址的界限。在最大地址以下,WRAP 与 INCR 类型完全相同,地址递增,但达到最高地址后,地址直接回到起始地址,再进行递增,就这样循环往复。数据手册上表示,WRAP 适合对 cache 的访问。

举个例子: