vscode搭建Verilog环境

VScode搭建Verilog源码开发环境记录【2023-7-21更新】

目录

- VScode搭建Verilog源码开发环境记录【2023-7-21更新】

- 一、从官网下载安装VScode

- 二、登录账号同步数据(如果已有)

- 三、安装插件

-

- 3.1 Chinese(simplified)中文汉化包

- 3.2 文件管理器的图标包icon theme

- 3.3 安装Verilog-HDL/systemVerilog插件

- 3.4 安装Verilog Highlight插件

- 3.5 安装CTags Support插件

- 3.6 安装Verilog Testbench插件

- 四、高级环境详细配置

-

- 4.1 配置默认文本编码格式,修正中文乱码

- 4.2 安装ctags

-

- ● Windows系统安装universal ctags

- ● Linux主流发行版安装universal ctags

- 4.3 在vscode:ctags support中进行相关配置

- 4.4 配置Verilog-HDL/SystemVerilog/Bluespec SystemVerilog的相关参数

-

- ● ctags PATH

- ● linter(语法检查工具)

- 五、将vivado默认文本编辑器替换为VsCode【2023-7-21更新】

最近实验室要做FPGA相关的工作,于是笔者开始自学相关技术。目前市面上最成熟的工具应该是VCS+Verdi,但是考虑到该工具链仅支持Linux,而且软件画面过于古早,安装和使用都过于冗杂,并且对新手来说学习成本实在太高。

因此我整理了各种资料,记录了本人使用vscode搭建轻量级Verilog开发环境的全过程,以供他人和自己将来参考。

一、从官网下载安装VScode

此步骤略

二、登录账号同步数据(如果已有)

注意,本人在实际使用时发现了vscode关于登录账户的一个bug:如果首次登陆选择使用GitHub登陆,那么无法直接注销账户再用Microsoft账户登陆。反之,若首次登陆选择使用Microsoft账户登陆,那么如果之后想换用GitHub账户登陆,也是不行的。它注销后再次登录会直接跳转到原来的登录方式验证网址,并且没有切换登陆渠道的选项(在2023年6月当前版本还未修复)。

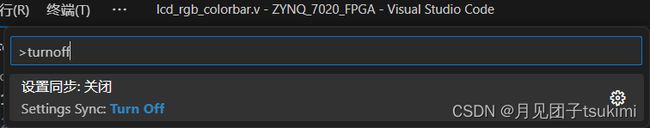

在这种情况下,如果想切换登陆账户,只能在设置中,先关闭云同步,注销账户,再重新打开云同步:

可以直接点击左下角设置中的“设置同步已打开”将其关闭,也可以通过命令将其关闭(如下):

按住CTRL+shift+P,召唤出vscode命令输入框(顶部弹出),在输入框中输入turnoff即可查找到【设置同步关闭】选项。

如果还从未使用过vscode可以暂时跳过此步。

三、安装插件

vscode本身是不支持Verilog语言开发的,要想在vscode中顺利的编写Verilog源码,需要安装如下插件:

3.1 Chinese(simplified)中文汉化包

在左栏的插件“extension”栏目中,搜索Chinese即可看到这个插件,安装后按照提示重启vscode,整个软件大部分界面即可变为中文。

3.2 文件管理器的图标包icon theme

vscode默认的资源管理器界面全部以文本显示,很多时候难以区分不同文件类型,安装图标包可以显著地区分开各种源码文件以及各种配置信息文件。

在vscode拓展插件市场中,本人推荐使用图中的这俩icon pak

3.3 安装Verilog-HDL/systemVerilog插件

搜索安装此插件:

这个插件提供了Verilog开发环境的绝大多数基础功能,例如:

- 代码高亮(highlight)

- 简单语法补全提示(snippets)

- 静态语法检查(lint,需要自行配置linter组件)

- Ctags功能集成(需要额外安装ctags组件)

- 自动补全

- 文档符号大纲

- 鼠标悬停显示代码声明

- CTRL鼠标点击跳转到代码声明

- 自动实例化模块

- Language server(实验性功能)

- 代码自动格式化(formatting,实验性功能)

这个插件虽然是vscode拓展市场下载量最高的插件,但是部分功能仍然残缺不全,很多高级功能无法开箱即用,需要我们进一步配置(这个细节配置将在第四节详细介绍。)

3.4 安装Verilog Highlight插件

此插件配合上面的Verilog-HDL/systemVerilog插件使用,能够完善.v文件和.sv文件的代码高亮功能。

3.5 安装CTags Support插件

搜索ctags,下载安装此插件:

注意:此插件本身不带ctags组件,它只是作为ctags到vscode的桥梁,将两者联系起来,使得vscode中的其他插件能够自动调用ctags相关功能。

3.6 安装Verilog Testbench插件

虽然上文3.3中安装的【Verilog-HDL/systemVerilog插件】已经有Verilog模块实例化功能,但是它只能生成一个空的例化模块(读者可以自行研究尝试),其功能并不完善。

通过3.6安装的testbench插件,不仅可以生成完整的例化代码,还可以生成信号比较完善的testbench测试代码。

注意:这个插件的功能需要依赖python3,并且安装过程会产生许多错误,不建议新手尝试。

当然,笔者既然写这篇文章,后文肯定会介绍安装和调试的过程。

四、高级环境详细配置

如果你只是一个新手,那么安装完上面的3.1,3.2,3.3,3.4插件已经足够简单的学习使用。

如果这些功能都不能满足你,可以继续往下看,进行更复杂的环境配置。通过下面的配置,可以在vscode中实现代码声明跳转、静态语法检查、模块自动例化、生成测试模块等高阶功能。

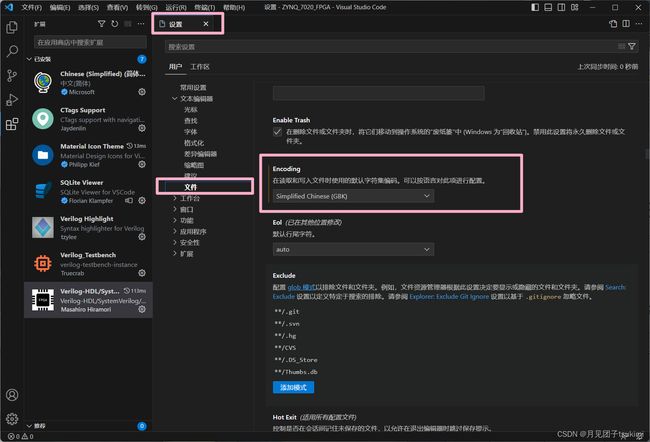

4.1 配置默认文本编码格式,修正中文乱码

如果你在打开含有中文注释的源码时发现中文变为乱码,100%的情况是因为文本字符编码和系统不兼容。

- 对于中国大陆的Windows用户来说,最佳的默认文字编码是GBK:

- 对于大多数Linux用户来说,最佳的字符编码是UTF-8:

如果在使用的过程中,出现中文字符乱码,请参考上述推荐编码模式进行配置。

4.2 安装ctags

如图所示,这个插件依赖于 universal ctags ,在该插件的详情页有各种操作系统的ctags安装网址,对应自己的操作系统选择对应的安装方式即可。

特别注意: Verilog-HDL/SystemVerilog/Bluespec SystemVerilog插件只兼容universal ctags ,并不兼容其他的ctags实现!!!

如果安装完以后,发现出现ctags索引不全,大概率安装的ctags并非这里所说的最新版universal ctags 。

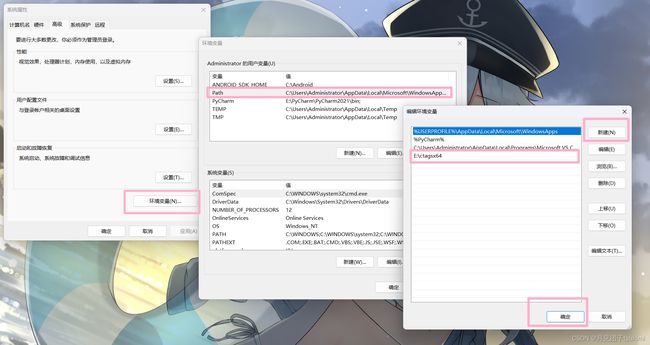

● Windows系统安装universal ctags

点击插件Verilog-HDL/SystemVerilog/Bluespec SystemVerilog详情页中的:

进入该网址,从release page选择最新版下载:

下载到本机,建议解压到一个不含空格和特殊字符的纯英文路径,例如:

然后将路径添加到Windows系统环境变量中的Path中,以我为例:

打开cmd终端,输入ctags --version,观察输出是否正常:

出现对应的版本信息,特别注意显示的ctags信息是universal ctags,说明安装正常,顺利结束。

● Linux主流发行版安装universal ctags

打开对应的下载官网:

- 如果你使用的Linux发行版版本较新,例如Ubuntu较新的版本,或者是Fedora较新的版本,则可以直接通过系统内置的包管理器apt install 或者dnf install。这个是最省事的。首选推荐方案!

- 如果你用的Linux发行版是较老的centOS或者其他不带apt或dnf工具的Linux版本,那么需要从源码安装

universal ctags- 特别注意:yum包管理器不行!!!!

从源码安装universal ctags参考官方最上面的教程:

$ git clone https://github.com/universal-ctags/ctags.git

$ cd ctags

$ ./autogen.sh

$ ./configure --prefix=/where/you/want # defaults to /usr/local

$ make

$ make install # may require extra privileges depending on where to install

注意,最后两步骤make和make install请务必在root权限下执行(加上sudo执行)!

在make install安装完成之后,ctags可执行文件将生成于$prefix/bin/路径下。默认为/usr/local/bin/ctags

同样,安装完成之后(没报错),随意在任何一个路径下打开终端,输入ctags --version观察回显是否正常。

至此,两大主流平台Windows和Linux安装ctags的教程介绍完毕。

(什么??你说还有macOS??)

4.3 在vscode:ctags support中进行相关配置

上一步我们只是在本机操作系统中成功安装了universal ctags组件,但是vscode中的拓展插件还不会自动调用ctags命令,需要我们在拓展设置中填入一些配置信息()

打开vscode拓展插件栏,找到ctags support,右键,点【拓展设置】:

在拓展设置中,按下图设置:

ctags support配置完成!

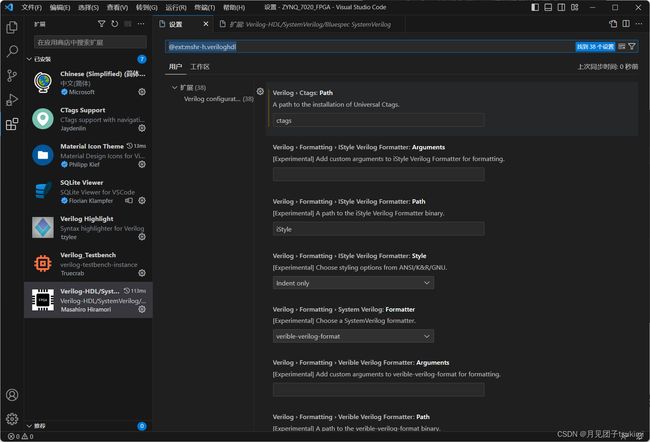

4.4 配置Verilog-HDL/SystemVerilog/Bluespec SystemVerilog的相关参数

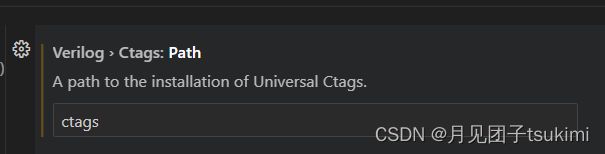

● ctags PATH

由于前面我们安装universal ctags的时候添加了系统环境变量,因此这里只需要填入“ctags”即可。

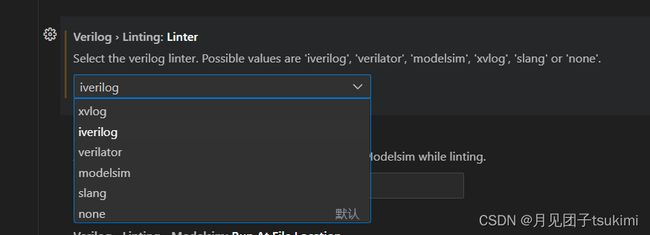

● linter(语法检查工具)

该插件支持以上静态语法检查工具(需要额外安装对应的软件),在Windows上笔者推荐使用Xilinx vivado自带的xvlog,在Linux上笔者推荐开源的轻量级iverilog。

对于vivado的安装以及iverilog,或者verilator的安装,不在本文范围之内,否则本文将过于冗长啰嗦,若有需要这两者的安装和使用教程,等后面笔者有时间再更新新的文章。

最后特别注意:linter工具只会在保存(CTRL+S)之后进行语法检查,因此,在编写源码的过程中没有红色波浪线提示,是正常的,如果你需要立刻进行一次语法检查,可以立即保存一次,或者通过rerun lint tool命令强制执行一次。

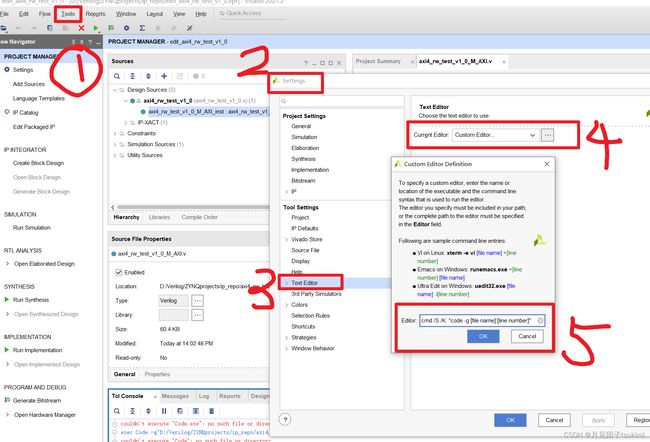

五、将vivado默认文本编辑器替换为VsCode【2023-7-21更新】

按照前文所述,安装好vscode环境后。启动vivado,按照如下所示,配置默认的 text editor:

*特别注意: 图中第五个框处的vscode调用代码应该写为:

cmd /S /K "code -g [file name]:[line number]"

如果直接写code -g [file name]:[line number] 会造成打开的vscode界面卡死!!!!

最终的使用效果,就不放展示视频了,基本上可以还原verdi端的50%的常用功能吧,各种鼠标悬停显示,代码声明跳转,静态语法检查,基本上都有了。总的来说,作为学习和科研使用,这套配置的体验是非常优秀的~

本文完·····························································Write by tsukimi @2023