Modelsim 使用教程(2)——Basic Simulation

一、概述

在本文中,我们将介绍Modelsim基本的仿真流程,包括有:

-

Create the Working Design Library(创建工具库)

-

Compile the Design Units(编译设计单元)

-

Optimize the Design(优化设计)

-

Load the Design(加载设计)

-

Run the Simulation(运行仿真)

二、设计文件及tb

首先给出本文中用到的设计文件及tb。

2.1 设计文件 counter.v

// Copyright 1991-2014 Mentor Graphics Corporation

//

// All Rights Reserved.

//

// THIS WORK CONTAINS TRADE SECRET AND PROPRIETARY INFORMATION WHICH IS THE PROPERTY OF

// MENTOR GRAPHICS CORPORATION OR ITS LICENSORS AND IS SUBJECT TO LICENSE TERMS.

//

`timescale 1ns / 1ns

module counter (count, clk, reset);

output [7:0] count;

input clk, reset;

reg [7:0] count;

parameter tpd_reset_to_count = 3;

parameter tpd_clk_to_count = 2;

function [7:0] increment;

input [7:0] val;

reg [3:0] i;

reg carry;

begin

increment = val;

carry = 1'b1;

/*

* Exit this loop when carry == zero, OR all bits processed

*/

for (i = 4'b0; ((carry == 4'b1) && (i <= 7)); i = i+ 4'b1)

begin

increment[i] = val[i] ^ carry;

carry = val[i] & carry;

end

end

endfunction

always @ (posedge clk or posedge reset)

if (reset)

count = #tpd_reset_to_count 8'h00;

else

count <= #tpd_clk_to_count increment(count);

/*****************************************************************

Use the following block to make the design synthesizable.

always @ (posedge clk or posedge reset)

if (reset)

count = 8'h00;

else

count <= count + 8'h01;

******************************************************************/

endmodule

2.2 仿真文件 tcounter.v

//

// Copyright 1991-2014 Mentor Graphics Corporation

//

// All Rights Reserved.

//

// THIS WORK CONTAINS TRADE SECRET AND PROPRIETARY INFORMATION WHICH IS THE PROPERTY OF

// MENTOR GRAPHICS CORPORATION OR ITS LICENSORS AND IS SUBJECT TO LICENSE TERMS.

//

`timescale 1ns / 1ns

module test_counter;

reg clk, reset;

wire [7:0] count;

counter dut (count, clk, reset);

initial // Clock generator

begin

clk = 0;

forever #10 clk = !clk;

end

initial // Test stimulus

begin

reset = 0;

#5 reset = 1;

#4 reset = 0;

end

initial

$monitor($stime,, reset,, clk,,, count);

endmodule

三、操作流程

3.1 Create the Working Design Library(创建工具库)

在开始设计仿真之前,必须首先创建一个库,并将源代码编译到该库中。

1、创建一个新的目录,并将设计文件复制到其中。

2、打开modelsim,点击File -> Change Directory,把目录改成我们之前刚刚创建的新文件夹。

3、 创建工作库

(1)选择File -> New -> Library

(2)点击OK

ModelSim创建一个名为work的目录,并将一个名为_info的特殊格式文件写入该目录。_info文件必须保留在目录中,以区分它作为ModelSim库。不要在操作系统中编辑文件夹内容;所有更改都应在ModelSim中进行。

ModelSim还将库添加到库窗口,并将库映射记录在ModelSim初始化文件(modelsim.ini)中以供将来参考。

此时在Transcript界面应该打印有如下内容:

这两行是你所做的菜单选择的命令行。许多命令行等价物将以这种方式响应它们的菜单驱动功能。

3.2 Compile the Design Units(编译设计单元)

在创建了工作库后,你就可以编译源文件了。你可以使用图形界面的菜单和对话框来编译源文件,如下面的Verilog示例中所述,或者通过在ModelSim>prompt下输入一个命令。

1、编译 counter.v 和 tcounter.v

(1)选择 Compile > Compile ,这会打开编译源文件对话框。

如果“编译”菜单选项不可用,则你可能已经打开了一个项目。如果是,通过使库窗口活动,并从菜单中选择File > Close来关闭项目。

(2)从编译源文件对话框中选择到 counter.v 和 tcounter.v 文件,分别点击Complie,完成后点击done。这些文件就会被编译到库中。

2、查看编译好的设计单元

(1)在“library”窗口中,单击work库旁边的“+”图标,您将看到两个设计单元,您还可以看到它们的类型(模块、实体等)。以及到底层源文件的路径。

3.3 Optimize the Design(优化设计)

优化你的仿真设计会加快这个过程。

1、使用 vopt 命令优化设计,使所有设计单位完全可见。

在 Transcript 窗口中的 ModelSim>prompt 下输入以下命令:

vopt +acc test_counter -o testcounter_opt+acc为调试提供了对设计的可见性。

-o允许你指定优化后的设计文件(testcounter_opt)的名称。

(使用vopt命令时,必须为优化的设计文件提供名称。)

3.4 Load the Design(加载设计)

现在我们就可以把设计加载进仿真中了

1、把tb_module模块加载到仿真中

通过vsim指令,使用优化后的设计名称(testcounter_opt)来加载设计

vsim testcounter_opt当设计被加载时,就会打开一个结构窗口(标记为sim)。此窗口显示了设计的层次结构,如下图所示:

2、打开 Objects 和 Process 窗口

(1)选择 View > Objects,同样的方式 打开View > Process

Objects窗口显示了在结构(sim)窗口中选定的当前区域中的数据对象的名称和当前值。数据对象包括信号、线网、寄存器、常量和变量、泛型、参数和SystemC模块的成员数据变量。

Process窗口提供了4种观测模式:动态,在区域、设计和分层中(Active, In Region, Design, and Hierarchical)来观测HDL或者SystemC过程。设计视图模式是用于ESL(电子系统级)设计的主要导航,其中流程是最要考虑的因素。默认情况下,此窗口将显示仿真的动态进程(active模式)。

3.5 Run the Simulation(运行仿真)

现在我们就可以进行仿真了,但是在此之前,我们还要打开wave窗口,把信号添加进去。

1、打开wave窗口

2、把信号加到wave窗口中

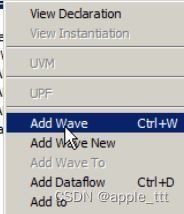

(1)在结构(sim)窗口中,右键单击test_counter打开弹出上下文菜单。

(2)选择 Add Wave

3、进行仿真

(1)点击 Run 按钮

仿真运行100ns(默认的仿真长度),波形会在Wave窗口中绘制。

(2)在Transcript界面的VSIM> prompt后面直接输入run 500us

仿真器又进行了500us的仿真,总共就进行了600us的仿真

(3)在命令行输入run -all 或者在主界面点击

仿真继续运行,直到执行break命令或代码中的停止仿真的命令语句(即Verilog $stop语句)。

(4)单击“中断”图标以停止模拟

至此,我们就完成了一些基本的仿真操作。

3.6 Set Breakpoints and Step through the Source(设置断点并逐行运行源代码)

接下来,我们将简单介绍Modelsim的交互式调试特性环境。你将在“源代码”窗口中设置一个断点,运行仿真,然后逐步完成测试中的设计。断点只能在可执行行上设置,它们用红线号表示。

1、在源代码窗口打开 counter.v 文件

(1)选择 View > Files 来打开Files窗口

(2)单击sim文件名旁边的+符号,可以查看vsim.wlf数据集的内容

(3)双击打开counter.v文件

2、在counter.v文件的第36行设置一个断点

滚动到第36行,然后单击行号旁边的Ln#(行号)列。在第36行行号列中出现一个红点(图3-9),表示已设置了断点。

3、禁用、启用和删除该断点

(1)单击该红点以禁用该断点。它会变成一个灰色的点

(2)再次单击灰点以重新启用断点。它会变成一个红点

(3)用鼠标右键单击红点,然后选择“删除断点36。

(4)再次单击第36行旁边的行号列,以重新创建断点。

4、重新启动仿真

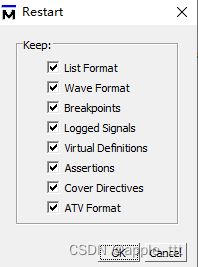

(1)单击“重新启动”图标以重新加载设计元素,并将模拟时间重置为零。

出现的“重新启动”对话框为你提供了关于在重新启动期间要保留什么的选项。

(2)点击OK

(3)点击 run -all按键

仿真将一直运行,直到到达断点为止。当仿真到达断点时,它将停止运行,在源代码视图中用蓝色箭头突出显示该行(图3-11),并在文字记录窗口中发出中断消息。

在这个时候程序就停止了运行,我们可以通过自己的方式进行程序运行的检查。

(4)继续运行

单击步骤”工具栏上的“Step into”图标

程序就跳过了断点,可以继续运行了。接下来可以自己进行尝试,掌握这部分的相关内容。

四、总结

我们需要结束当前的模拟。 1.选择“Simulate>End Simulate”。 2.当提示确认要退出仿真时,单击“是”。

在本文中,我们详细介绍了Modelsim仿真的一个基本流程,并做出了详细的步骤指导。