【ug903】Xilinx XDC约束的序(Order)

“Because XDC constraints are applied sequentially, and are prioritized based on clear precedence rules, you must review the order of your constraints carefully.”

这句话告诉我们,XDC约束按顺序执行,且约束之间有优先级。那么,XDC约束的顺序由什么决定呢?XDC约束之间的优先级关系又是怎样的呢?

1 约束文件读取顺序

与ISE不同, Vivado使用约束集(constraints set)包含一个或多个XDC约束文件,每个约束文件包含一条或多条约束指令。确定了约束文件的读取顺序,也就基本确定了约束指令的执行顺序。

Xilinx XDC约束文件分为两类:

1. 用户约束文件 :出现在Sources > Hierarchy > Constraints文件夹下的约束集中;

2. IP 约束文件 :出现在Sources > IP Sources视图下的IP中;

Vivado通过PROCESSING_ORDER属性初步将Xilinx XDC约束文件的读取顺序分为三个等级:

1. EARLY : Files that must be read first

2. NORMAL : Default

3. LATE : Files that must be read last

对于用户约束文件

1. By default, user XDC files belong the PROCESSING_ORDER NORMAL group.

2. For user XDC files that belong to the same PROCESSING_ORDER group, their relative order desplayed in the Vivado IDE determines their read sequence.

3. The order within the group can be modified by moving the files in the Vivado IDE constraints set.

以上三点总结如下:

1. 用户约束文件PROCESSING_ORDER默认为NORMAL;

2. PROCESSING_ORDER相同的用户约束文件读取顺序由它们在Vivado约束集中的相对位置决定;

3. 可以通过拖拽的方式来改变用户约束文件在约束集中的位置,进而改变其读取顺序

对于IP约束文件

1. An IP XDC will have its PROCESSING_ORDER property set to either EARLY or LATE. No IP delivers XDC files that belong to the NORMAL constraints group.

2. For IP XDC files that belong to the same PROCESSING_ORDER group, the order is determined by import or creation sequence of the IP cores.

3. This order cannot be changed after the project has been created.

以上三点总结如下:

1. IP约束文件PROCESSING_ORDER默认只能EARLY或LATE,不能是NORMAL;

2. PROCESSING_ORDER相同的IP约束文件读取顺序由包含它们的IP核在Vivado IP Sources窗口中的相对位置决定,不可更改;

关于PROCESSING_ORDER相同的IP约束文件读取顺序的更改,个人有以下看法:

1. 可以通过将IP从工程中移除然后再重新添加到工程中的方式改变IP约束文件的读取顺序;

2. 可以通过将IP约束文件Disable然后复制其内容到用户约束文件的方式改变IP约束文件的读取顺序(Xilinx给出的方法);

关于IP约束文件再补充几点:

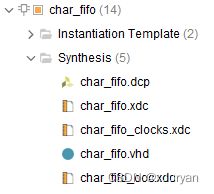

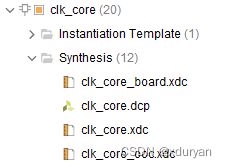

1. IP约束文件常见有ip_name.xdc、ip_name_ooc.xdc、ip_name_clocks.xdc等,其他相见ug896;

2. ip_name.xdc和ip_name_ooc.xdc默认的PROCESSING_ORDER为EARLY;

3. ip_name_clocks.xdc默认的PROCESSING_ORDER为LATE;

用户约束文件和IP约束文件之间的关系

1. By default, IP XDC files are read in before the user XDC files.

2. Processing it in this way allows an IP to create a clock object that can be referenced in the XDC.

3. It also allows you to overwrite physical constraints set by an IP core because the user constraints are evaluated after the IP.

关于以上三点总结如下:

1. 默认先读取IP约束文件后读取用户约束文件(原因在上面的2和3中已经给出),ip_name_clocks.xdc是个例外(相见ug896);

用户约束文件和IP约束文件的最终读取顺序如下:

1. User Constraints marked as EARLY

2. IP Constraints marked as EARLY (default)

3. User Constraints marked as NORMAL

4. IP Constraints marked as LATE (contain clock dependencies)

5. User Constraints marked as LATE

约束文件读取实例

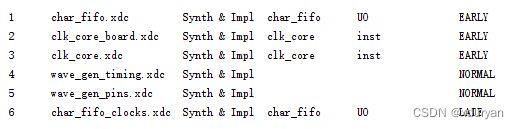

使用report_compile_order -constraints命令可以查询当前工程所有约束文件的执行顺序,这里以xilinx自带的wavegen example design为例,如下图所示。

“Constraint evaluation order for ‘implementation’ with fileset ‘sources_1’ & with fileset ‘constrs_1’”

注意:char_fifo_ooc.xdc和clk_core_ooc.xdc未出现在上图中,因为上图报告的是"implementation"阶段约束文件的读取顺序,ip_name_ooc.xdc只在IP的OOC Synthesis综合阶段生成DCP文件时有用。

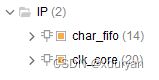

wavegen工程有两个IP:char_fifo和clk_core,其位置如下图所示:

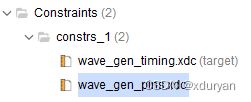

wavegen工程有两个用户约束:wave_gen_tming.xdc和wave_gen_pins.xdc,其位置如下图所示:

2 约束指令执行顺序

前文提到过:约束文件的读取顺序确定了,约束指令的执行顺序也就基本确定了。注意这里说的是“基本确定”,但是尚未完全确定,因为约束指令之间可能存在冲突、重叠和依赖特殊情况。

约束按照对象不同可以分为物理约束(physical constraints)和时序约束(timing constraints)。

对于物理约束

1. 存在冲突(Conflict)的情况:If multiple physical constraints are conflicting, the latest constraint wins. For example, if an I/O port gets assigned a different location (LOC) through multiple XDC files, the latest location assigned to the port takes precedence.

对于时序约束

1. 存在冲突(Conflict)的情况:对同一个时钟Port使用两条create_clock指令创建时钟对象,在不加-add选项的情况下,后面的约束指令会覆盖前面的约束指令;

2. 存在重叠(Overlap)的情况:主要是时序例外(Timing Exception)约束中的路径重叠,时序例外约束有执行的优先级,和读取顺序没有关系,优先级按照指令不同、对象不同和选项不同如所示:

(1)指令不同

If constraints overlap (for example, if several timing exceptions are applied to the samepath), the priority from highest to lowest is:

a. Clock Groups (set_clock_groups)

b. False Path (set_false_path)

c. Maximum Delay Path (set_max_delay) and Minimum Delay Path (set_min_delay)

d. Multicycle Paths (set_multicycle_path)

(2)对象不同

The priority rule for the objects is:

1. Ports, pins, and cells

Pins of a cell are used instead of the cell itself.

2. Clocks

Clocks always have lower priority than ports, pins, and cells. A timing exception that uses clock object(s) always has a lower priority than another timing exception defined with ports, pins, and cells.

(3)选项不同

The precedence rule for the filters, from highest to lowest, is:

a. -from -through -to

b. -from -to

c. -from -through

d. -from

e. -through -to

f. -to

g. -through

3. 存在依赖(Dependency)的情况:

(1)一定要先创建主时钟

a. Start with the clock definitions.

b. The clocks must be created before they can be used by any subsequent constraints.

c. Any reference to a clock before it has been declared results in an error and the corresponding constraint is ignored.

(2)建议时序约束顺序如下

Timing Assertions Section

a. Primary clocks

b. Virtual clocks

c. Generated clocks

d. Clock Groups

e. Bus Skew constraints

f. Input and output delay constraints

Timing Exceptions Section

a. False Paths

b. Max Delay / Min Delay

c. Multicycle Paths

d. Case Analysis

e. Disable Timing

物理约束和时序约束的位置关系

两者关系如下:

Physical Constraints Section

1. located anywhere in the file, preferably before or after the timing constraints or stored in a separate constraint file

总结就是:物理约束要么在时序约束前边,要么在时序约束后边,最好分开存放在不同的约束文件中吗,如project_name_pinout.xdc和project_name_timing.xdc。