ZYNQ实验---IQ调制实现SSB PART1

参考文献

-

软件无线电 多模式调制解调

-

HDL Digital Up-Converter (DUC)

-

复信号与IQ调制

-

HackRFOne

-

TI超外差接收与零中频接收

一、基本理论

软件无线电中,各种调制信号都是用一种通用数字信号来实现的。采用复数IQ信号结合DAC芯片的实现各种调制。理论上,各种信号都可以用正交调制的方法实现。

调制信号的信息都包括()和()内,可以对上式子进行数字化处理

IQ调制(复数形式)实现可以表示为以下形式

SSB调制

二、实验介绍

实验平台

硬件平台:ZYNQ 7020, HackRF One

软件平台:Matlab 2021b,Vivado2018.3,VS2022

实验设计

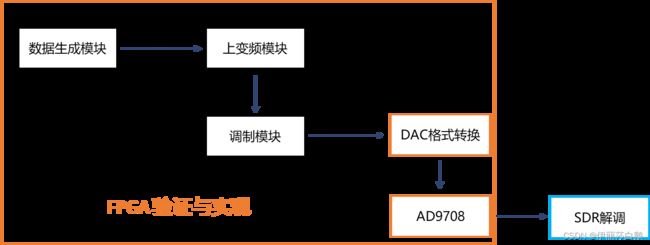

根据第一部分的理论介绍,实验目标为设计实现通用数字调制器。本文以SSB调制为例详细描述实验过程。

整体设计包含3部分结构:PC端数据处理,PL端数据转发即控制,PS端的上变频与调制。

1、PC端数据处理

PC将读取到的调制信号转化统一定点数格式的IQ信号(解析信号形式),并将其存入到PL端中。

2、PS端数据转发

实现对DUC发送通道的控制,通过PS实现PC与PL的数据交互。

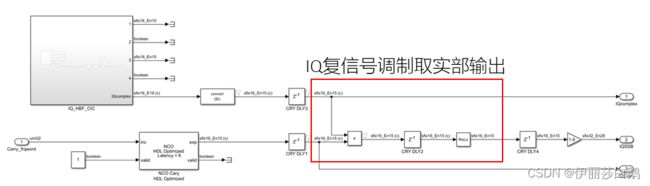

3、PL端数据处理

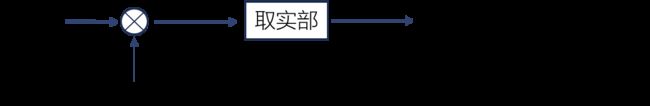

读取PS端并将数据从存储模式转换为流模式(DAC是数据输入是流模式),通过CIC以及FIR滤波器后实现数字上变频,变频后的信号与载波相乘取实部发送至DAC实现整个调制。实验的重点PL端DUC发送通道的设计实现

三、实验实现

DUC的实现使用Simulink HDL设计Simulink HDL设计提供了一种图形化、高级和快速的方式来进行硬件系统设计和开发。它可以大大加速设计过程并降低错误的风险,同时提供灵活性和可重用性。

Simulink HDL使用介绍可以参考我写的文章,后续还会再其他文章中对这部分进行补充。

DUC整体设计方案

Simulink中为方便仿真fs=8MHz,实际使用fs=80MHz

1、数据生成模块(fs=16kHz)

14个单音信号按照一定的时序组合生成调制信号,该信号的频率成分单一便于分析观察。每个单音持续时间0.125秒,采用两个RAM实现,一个用于存储频率字出现的顺序另一个用于存储信号频率字。

2、上变频模块(fs=16kHz~8MHz)

3、调制模块(fs=8MHz)

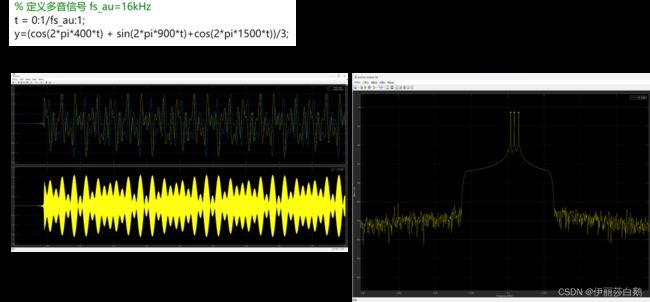

Simulink 仿真

上图为待调制的IQ信号,下图为调制后的信号

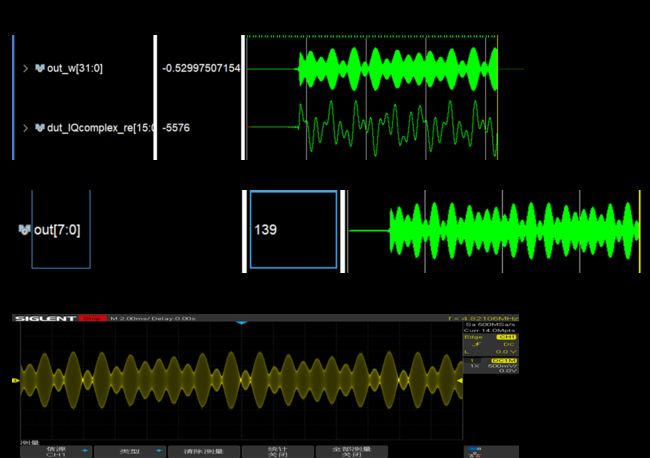

使用Simulink的逻辑分析仪进行仿真(定点数仿真结果未出现失真)

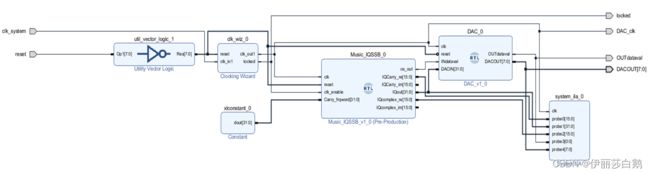

ZYNQ 实现

核心的IQSSB模块通过Simulink代码生成,DAC模块未截取数据位输入到DAC中将数据转换为模拟信号。模块的仿真就不再展示,结果和Simulink的逻辑分析仪类似。

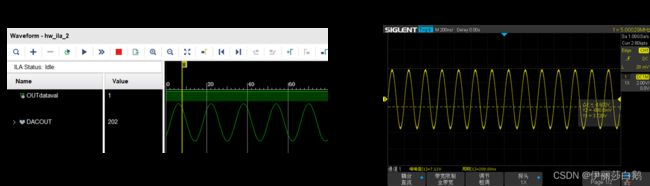

实际运行结果

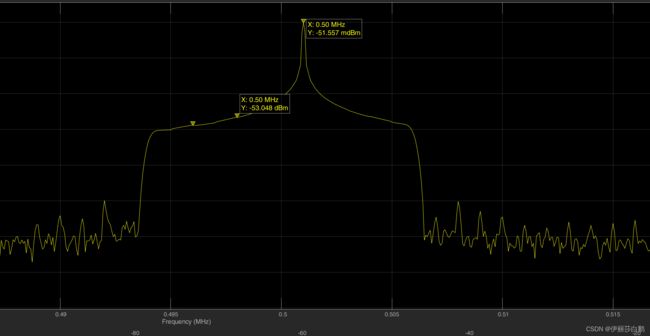

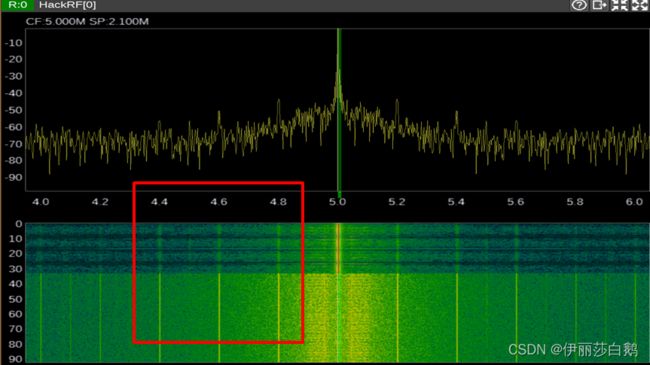

FPGA实际输出的信号波形完整未发生失真,将信号送入HackRF one中进行SSB解调,观察是否能正常解调出单音信号。

SDR解调演示

问题: 实验使用的调制信号为单音信号,不便于观察其时域波形是否失真,并且可能存在互调失真等等问题,在实际应用中信号为单音信号情况较少,因此还行进一步验证DUC模块处理多音信号的情况。HackRF One接收到信号的频谱中存在明显的频谱泄露。

四、实验问题改进

1、多音信号实验

音频包含的频率成分较多,从时域和频域上都不便于直接观测出是否正常调制。简化实验采用多音信号进行实验,验证方案可行性。

1.1 Matlab仿真

1.2 Simulink HDL仿真

Simulink设计的结构相较于之前的实验并未做修改,仅将输入信号从音频变为多音信号。

1.3 FPGA验证

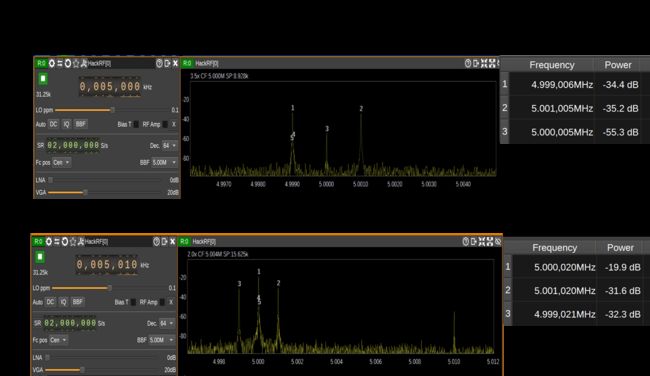

2、SDR实验问题

HackRF one接收实验信号,SDRangle频谱图除5MHz的中心频率外每隔200kHz的旁瓣上存在谱线,并且在中心频率上还会出现较大的直流信号。此时的相关参数:fc=5MHz,基带采样率为2.1Msps,信号带宽24kHz。

FPGA通过DAC输出的已调信号通过频谱仪观察是正常的,但是使用SDR观察其频谱就会出现上述问题

2.1 旁瓣谱线

通过与频谱仪的观测结果做对比,旁瓣出现谱线的问题是软件问题导致,通过软件设置重新设置FFT采样点数,窗函数等等可以消除这部分的影响。

2.2 中心直流信号

Hack RF采用的是零中频接收机的方式,本振泄露等方式导致出现了直流偏置(中心频率的较大偏置)。Hack RF One并未采用一定的方法去消除本振泄露,官方文档给出的几个建议:1、中心频率不直接设置为需要解调的频率 2、在软件端采用算法去消除显示

2.3 实验测试

使用信号源输出AM调制信号,通过Hack RF One观测信号

五、整体实验设计

红色部分为未完成部分,后续会进行补充。

目前存在的问题:

1、调试过程中UDP丢包严重

2、中断控制反应不正确

3、上位机程序设计存在问题