【实验报告】LFM信号产生与频谱分析(记录一次实验:《电类综合实验》)

本实验利用DE2-115开发板产生一个参数可变的线性调频(LFM)信号,用数字滤波器滤波并通过DA转换为模拟中频信号。然后通过AD采样,并进行正交下变频和fft处理进行频谱分析。

实验报告首先介绍了LFM、FFT以及VGA、LCD、数码管显示的基本原理,然后给出了工程的总体设计方案。其次使用Verilog HDL进行模块的设计。再次利用Modelsim软件与Quartus II进行工程的RTL级联合仿真,验证基本功能的正确性。最后上板调试完成了基本功能与提升功能,并在此基础上,添加了开发板VGA接口显示时域波形、FFT幅度谱以及相位谱的功能。

经实验验证,本设计可以很好的满足实验要求。

关键词:FPGA、LFM、FFT、VGA

文章目录

- 1 实验内容与要求

-

- 1.1 实验内容

- 1.2 实验要求

- 2 实验仪器

- 3 实验原理

-

- 3.1 线性调频信号的产生

-

- 3.1.1 LFM信号分析

- 3.1.2 用DDS产生LFM信号

- 3.2 FIR滤波器的设计

- 3.3 频谱分析

-

- 3.3.1 频谱分析流程

- 3.3.2 基于FFT的频谱分析

- 3.4 拓展1:VGA显示原理

- 3.5 拓展2:LCD以及数码管显示原理

-

- 3.5.1 LCD1602显示原理

- 3.5.2 7段数码管显示原理

- 4 实验过程

-

- 4.1 FPGA工程总体设计

-

- 4.1.1 总体方案设计

- 4.1.2 控制协议

- 4.2 FPGA工程子模块设计

-

- 4.2.1 lfm_gen:LFM波形产生模块

- 4.2.2 fir_lpf :FIR滤波器模块

- 4.2.3 ddc:数字下变频模块

- 4.2.4 abs:FFT输出值求幅值模块

- 4.2.5 phase_calc_cordic:相位计算模块

- 4.2.6 vga_disp:VGA显示模块

- 4.2.7 vga_driver:VGA驱动模块

- 4.2.8 abs_cur_key_ctrl:VGA显示截位模块

- 4.2.9 lcd1602_disp:LCD1602显示模块

- 4.2.10 seg7_disp:数码管显示模块

- 4.3 基于Modelsim的RTL级仿真

- 4.4 测试结果

-

- 4.4.1 LFM脉冲信号的产生

- 4.4.2 FIR滤波器测试

- 4.4.3 ADC信号频谱分析结果

- 4.4.4 拓展1:VGA显示测试

- 4.4.5 拓展2:LCD与数码管显示测试

- 5 思考与讨论

-

- 5.1 遇到的问题及解决

- 5.2 实验的收获与感受

- 5.3 未来的期望与要求

1 实验内容与要求

1.1 实验内容

本实验基于FPGA开发板(DE2-115)和AD/DA板(THDB-ADA)设计一个信号产生与频谱分析系统,主要完成以下两个内容:

-

本实验基于FPGA开发板(DE2-115)和AD/DA板(THDB-ADA)设计一个信号产生与频谱分析系统

-

本实验基于FPGA开发板(DE2-115)和AD/DA板(THDB-ADA)设计一个信号产生与频谱分析系统

1.2 实验要求

-

基本要求

-

产生LFM脉冲,通过调试工具设置信号参数,使得脉冲宽度在1us~1s内可变,带宽在5MHz~10MHz可变,脉冲重复周期在10us~2s内可变,载波频率在5MHz~20MHz可变,输出信号幅度在0.1~1V可变,以上参数可任意组合,产生的信号通过DAC输出,DAC数据更新率为120MHz。

-

将上面产生的LFM脉冲先通过截止频率为5MHz,阻带频率为10MHz的FIR低通滤波器,再通过DAC输出。

-

ADC采集外接信号,采样率为60MHz,对其进行1024点FFT,能够通过Signaltap观察信号的幅频特性和相频特性。

-

-

提高要求

-

LFM信号的参数可变范围进一步扩展,范围越大越好。

-

多组FIR滤波器的冲击响应可实时切换。

-

频谱分析的分辨率进一步提高。

-

-

拓展要求

由于本周实验是第十四周,为了保证实验内容有一定的创新性,可以加入一些拓展内容。我加入的拓展内容如下:

-

增加开发板上VGA接口连接显示器显示时域信号或频谱的功能。

-

增加开发板上LCD1602显示学号姓名,数码管显示参数的功能。

-

2 实验仪器

| 序号 | 仪器 | 数量 |

|---|---|---|

| 1 | FPGA开发板(DE2-115) | 1 |

| 2 | AD/DA板(THDB-ADA) | 1 |

| 3 | 示波器 | 1 |

| 4 | 信号源 | 1 |

| 5 | NBC-SMA导线 | 1 |

| 6 | SMA-SMA导线 | 1 |

| 7 | 显示器(VGA接口) | 1 |

3 实验原理

3.1 线性调频信号的产生

3.1.1 LFM信号分析

LFM基带信号的数学表达式为:

s ( t ) = r e c t ( t T ) e j 2 π K t 2 s(t)=rect(\frac{t}{T})e^{j2{\pi}Kt^2} s(t)=rect(Tt)ej2πKt2

其中,rect()是矩形脉冲函数,T是脉冲持续时间,单位是s,K是调制斜率,单位是Hz/s。

瞬时相位为:

φ ( t ) = π K t 2 \varphi(t)=\pi Kt^2 φ(t)=πKt2

瞬时频率为:

f ( t ) = 1 2 π d φ ( t ) d t = K t f(t)=\frac{1}{2\pi}\frac{d\varphi(t)}{dt}=Kt f(t)=2π1dtdφ(t)=Kt

带宽为:

B = K t B=Kt B=Kt

LFM带通信号的数学表达式为:

s ( t ) = r e c t ( t T ) e j ( 2 π f c t + 2 π K t 2 ) s(t)=rect(\frac{t}{T})e^{j(2\pi f_c t + 2{\pi}Kt^2)} s(t)=rect(Tt)ej(2πfct+2πKt2)

其中,real()是取复数实部函数, f c f_c fc是载波频率,单位是Hz。

瞬时相位为:

φ ( t ) = 2 π f c t + π K t 2 \varphi(t)=2\pi f_c t + \pi Kt^2 φ(t)=2πfct+πKt2

瞬时频率为:

f ( t ) = 1 2 π d φ ( t ) d t = f c + K t f(t)=\frac{1}{2\pi}\frac{d\varphi(t)}{dt}=f_c + Kt f(t)=2π1dtdφ(t)=fc+Kt

带宽为:

B = K t B=Kt B=Kt

3.1.2 用DDS产生LFM信号

瞬时频率:

f ( n T s ) = f c + K n T s f(nT_s)=f_c + KnT_s f(nTs)=fc+KnTs

DDS的频率调谐字FTW与输出频率的关系:

F T W = f 0 f s 2 N FTW=\frac{f_0}{f_s}2^N FTW=fsf02N

其中,N是DDS的相位累加器位数, f s f_s fs为DDS的时钟频率。因此,用DDS产生LFM信号时,对应的频率调谐字为:

F T W = r o u n d ( f 0 ( n ) f s 2 N ) = r o u n d ( f c f s 2 N + n H T s 2 2 N ) FTW=round(\frac{f_0(n)}{f_s}2^N)=round(\frac{f_c}{f_s}2^N + nH{T_s}^22^N) FTW=round(fsf0(n)2N)=round(fsfc2N+nHTs22N)

3.2 FIR滤波器的设计

FIR滤波器的设计方法主要有:

-

窗函数法:是一种在时域设计FIR数字滤波器的方法,用窗函数对理想滤波器的冲击响应进行加权。

-

频率取样法:从频域出发,对理想滤波器频域特性进行等间隔采样,将采样值作为待设计滤波器的频率特性,对其做IDFT得到滤波器的冲击响应。

-

最优设计方法:等波纹切比雪夫逼近法,采用“最大误差最小”准则得到最佳滤波器。

本实验通过最优滤波器设计方法来设计滤波器,需要设计用于LFM信号滤波以及数字下变频滤波的滤波器,滤波器参数如下:

| 序号 | 采样率/MHz | 通带截止频率/MHz | 阻带截止频率/MHz | 用途 |

|---|---|---|---|---|

| 1 | 120 | 5 | 10 | LFM输出滤波 |

| 2 | 120 | 10 | 15 | LFM输出滤波 |

| 3 | 120 | 15 | 20 | LFM输出滤波 |

| 4 | 120 | 20 | 25 | LFM输出滤波 |

| 5 | 120 | 30 | 35 | LFM输出滤波 |

| 6 | 120 | 40 | 45 | LFM输出滤波 |

| 7 | 120 | 50 | 55 | LFM输出滤波 |

| 8 | 60 | 10 | 13 | 数字下变频滤波 |

使用matlab生成滤波器系数并生成txt文件,相关代码如下:

clear all;

close all;

Fs = 120e6; % 采样率

Fc = 15e6; % 通带截止频率

Fa = 20e6; % 阻带截止频率

mag = [1 0]; % 幅度

dev = [0.01 0.05]; % 波纹

[n,wn,beta,ftype] = kaiserord([Fc Fa],mag,dev,Fs);

fpm = [0 Fc*2/Fs Fa*2/Fs 1]; % 频段向量

magpm = [1 1 0 0]; % 幅度向量

% 窗函数法

% h1 = fir1(n,wn,ftype,kaiser(n+1,beta));

% figure;freqz(h1);title('窗函数法');

% figure;plot(h1);title('窗函数法冲击响应');

% 最优滤波器设计方法

h2 = firpm(n,fpm,magpm);

figure;freqz(h2);title('最优滤波器设计法');

figure;plot(h2);title('最优滤波器设计法冲击响应');

% coef = h2 * 2^13 / max(abs(h2));

% figure;freqz(coef);title('最优滤波器设计法量化');

% figure;plot(coef);title('最优滤波器设计法冲击响应量化');

coef = h2;

fid = fopen('.\coef\fir_fs120_15_20.txt','w'); %写到sin.coe文件,用来初始化sin_rom

for i = 1:1:length(coef)

fprintf(fid,'%d,',coef(i));

end

fclose(fid);

在Quartus II中选择“FIR Compil II”IP核并选择对应的系数文件并点击应用即可完成滤波器的设计,如果需要不同的类型以及截止频率,选择不同的系数文件即可。

3.3 频谱分析

3.3.1 频谱分析流程

-

对模拟信号进行低通采样或者带通采样得到实信号(对应FPGA的ADC驱动模块);

-

对实信号正交下变频,得到零中频复信号(对应FPGA的DDS以及数字下变频驱动模块);

-

对零中频信号作FFT,得到被分析信号的幅频特性和相频特性(对应FPGA的FFT以及求模和幅角的模块)。

3.3.2 基于FFT的频谱分析

FFT是快速傅里叶变换的简称,可对离散信号进行频谱分析。

若时域离散序列为 x ( n ) , 0 ≤ n ≤ N − 1 x(n),0\leq n \leq N-1 x(n),0≤n≤N−1,对其作N点FFT运算得到:

X ( k ) = ∑ n = 0 N − 1 x ( n ) e − j 2 π N k n X(k)=\sum_{n=0}^{N-1}x(n)e^{-j\frac{2\pi}{N}kn} X(k)=n=0∑N−1x(n)e−jN2πkn

其中, ∣ X ( k ) ∣ |X(k)| ∣X(k)∣是归一化频率为 2 π N k \frac{2\pi}{Nk} Nk2π的信号分量的幅度, a r g ( X ( K ) ) arg(X(K)) arg(X(K))是相位。一般地,N为2的整数次幂方。

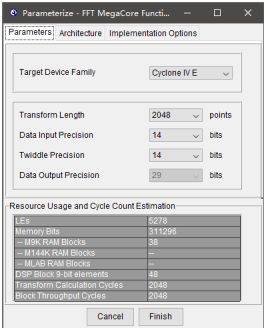

在本实验中,为了实现进一步提高频谱分析的分辨率,选择使用2048点FFT,在采样率为60MHz的情况下,频谱的分辨率为:

Δ = ] f r a c 1 N × f s = 1 2048 × 60 M H z = 29296.875 H z \Delta=]frac{1}{N}\times f_s=\frac{1}{2048}\times 60MHz=29296.875Hz Δ=]frac1N×fs=20481×60MHz=29296.875Hz

实验中的处理直接采用FFT IP核,在Quartus II中选择“FFT”IP核并选择对应的参数即可。

3.4 拓展1:VGA显示原理

VGA是IBM公司在1987年推出的一种视频传输标准,它具有分辨率高、显示速率快、颜色丰富等优点,因而在彩色显示器领域得到了广泛的应用。 虽然由于体积较大等原因,VGA接口已经逐渐被HDMI等新式接口淘汰, 但是对于近几年的显示器而言,VGA仍是制造商所支持的最低显示标准。

DE2-115 开发板包含一个用于 VGA 视频输出的 15 引脚 D-SUB 接头。 VGA同步信号直接由Cyclone IV E FPGA 所驱动, Analog Device 公司的 ADV7123 三通道 10位(仅高八位连接到FPGA)高速视频 DAC芯片用来将输出的数字信号转换为模拟信号(R,G,B)。芯片可支持的分辨率为 SVGA标准(1280*1024),带宽达 100MHz。

在本实验中,我根据实验室显示器以及实际需要显示的内容(2048点FFT幅频与相频特性、滤波前后时域波形),选择XVGA格式,VGA在传输过程中的同步时序分为行时序和场时序。

从上面两幅图中我们可以看到VGA传输过程中的行同步时序和场同步时序非常类似,一行或一场(又称一帧)数据都分为四个部分:低电平同步脉冲、显示后沿、有效数据段以及显示前沿。其时序规范如下:

| VGA模式 | 行时序(像素数) | 帧时序(行数) | |||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| 配置 | 时钟 | a | b | c | d | e | a | b | c | d | e |

| XGA(60Hz) 1024*768 | 65MHz | 136 | 160 | 1024 | 24 | 1344 | 6 | 29 | 768 | 3 | 806 |

3.5 拓展2:LCD以及数码管显示原理

3.5.1 LCD1602显示原理

DE2-115开发板上配有美国Crystalfontz公司的LCD模块,型号为CFAH1602B-TMC-JP,发送合适的命令控制字到显示控制器HD44780便可以在LCD显示文字信息。

LCD1602顾名思义就是显示2行,每行16个字符的LCD显示器。如下图所示:

这个模块通过一系列的内部控制指令完成模块的清屏、光标定位、显示掩码、显示字符查找表中的字符等功能。指令或数据的写时序以及字符查找表如下:

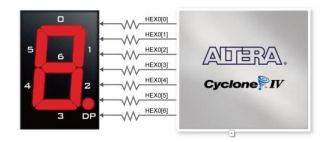

3.5.2 7段数码管显示原理

DE2-115配有八个七段数码管。它们被分成两组,每组四个,用来作为数字显示用。七段数码管的每个引脚均连接到Cyclone

IV E

FPGA。查看原理图可以得知数码管是共阳结构,FPGA输出低电压的时候,对应的字码段点亮,反之则熄灭。

本实验将显示各部分数据的截位以及带宽和载频。

4 实验过程

本次实验主要流程由总体方案设计,基本功能的RTL级仿真、实际调试以及最终验收四个部分组成。总体方案设计基于自顶向下的设计流程,对总体设计进行功能划分,分为不同功能的子模块,提高代码的可读性与可维护性。基于Modelsim的RTL级仿真主要是验证基本功能时序的正确性,为上板调试前解决一些例如代码时序逻辑错误等bug,可以节省调试时间,提高效率。实际调试则是通过实际的结果来反馈工程设计的过程,对工程中一些例如人机交互、功能设计等方面的bug进行修复,如果需要添加一些功能,还需要重复上述过程。实验过程的流程图如下:

4.1 FPGA工程总体设计

4.1.1 总体方案设计

其中,pll_clk模块为分频模块,输入板载晶振产生的50MHz时钟,通过锁相环输出120MHz、60MHZ以及64MHz三个时钟域。其中120MHz时钟主要用于DA及相关模块,60MHz主要用于AD及相关模块,64MHz主要用于VGA显示模块,值得注意的是,标准XGA模式(1024*768,60Hz)时序的工作时钟为65MHz,由于不满足50MHz时钟输入下整数的倍频与分频系数,所以为了方便直接取64MHz,此时显示器刷新率达不到60Hz。

120MHz时钟域下的主要模块及功能如下:

| 序号 | 模块名称 | 功能 |

|---|---|---|

| 1 | lfm_gen | 产生特定的LFM波形 |

| 2 | fir_lpf | 将LFM波形通过选择的滤波器并输出 |

60MHz时钟域下的主要模块及功能如下:

| 序号 | 模块名称 | 功能 |

|---|---|---|

| 1 | ctrl_signal | 根据lfm_gen的同步信号进行采样时序同步 |

| 2 | carry_gen | 根据载频控制参数输出该时钟域下DDC需要的载波 |

| 3 | ddc | 对ad采样的信号进行数字下变频处理 |

| 4 | fft | 对数字下变频后的信号进行fft处理 |

| 5 | abs | 对fft后的信号进行求模处理 |

| 6 | phase_calc_cordic | 对fft后的信号进行求相角处理 |

| 7 | lcd1602_disp | 驱动LCD1602显示学号及姓名 |

60MHz时钟域下的主要模块及功能如下:

| 序号 | 模块名称 | 功能 |

|---|---|---|

| 1 | vga_disp | 根据lfm_gen的同步信号进行采样时序同步 |

| 2 | vga_driver | 产生vga显示的时序 |

4.1.2 控制协议

此方案的操作说明(控制协议)如下:

| 硬件 | 位 | 说明 |

|---|---|---|

| Switch | [1:0] | 00:输出相位谱 01:输出幅度谱 11/10:输出lfm波形 |

| [2] | DDC使能: 0:失能 1:使能,载波频率=lfm载波频率 | |

| [4:3] | 显示波形模式时的采样点数 00:1024 01:2048 10:4096 11:8192 | |

| [9:6] | ABS截位 | |

| [13:10] | 相位计算截位 | |

| [17:14] | DDC截位 | |

| Button | [0] | 复位信号,低电平(按下)有效 |

| [1] | 幅度截位加 | |

| [2] | 幅度截位减 | |

| Segmen7 | [0] | VGA输出数据截位 |

| [1] | FFT幅频截位 | |

| [2] | FFT相频截位 | |

| [3] | DDC截位 | |

| [5:4] | 带宽/MHz | |

| [7:6] | 载波/MHz | |

| ISSP | [0] | 脉宽/us |

| [1] | 带宽/MHz | |

| [2] | 脉冲重复周期/us | |

| [3] | 载波频率/MHz | |

| [4] | 幅度/除2^value | |

| [5] | Fir滤波器序号 |

4.2 FPGA工程子模块设计

4.2.1 lfm_gen:LFM波形产生模块

其中周期计数器从0~I_prp(us)*I_sys_clk(/MHz)循环计数,频率控制字计算块在周期计数器的时序控制下利用载频,脉宽计算NCO块的频率控制字,产生的LFM信号通过移位进行幅度控制并输出。由于ad时钟为60MHz,da时钟为120Mhz,所以时序同步信号O_ctrl_idle是长度为3个时钟周期的脉冲信号,与LFM信号的开始同步。

4.2.2 fir_lpf :FIR滤波器模块

模块主要由七个并行的FIR低通滤波器组成,最后还有一路直通信号方便测试使用,详细的参数见下表所示,这几路滤波后的数据通过滤波模式选择输出。

| 序号 | 通带截止频率/MHz | 阻带截止频率/MHz |

|---|---|---|

| 1 | 5 | 10 |

| 2 | 10 | 15 |

| 3 | 15 | 20 |

| 4 | 20 | 25 |

| 5 | 30 | 35 |

| 6 | 40 | 45 |

| 7 | 50 | 55 |

| 8 | / | / |

4.2.3 ddc:数字下变频模块

其中I_carry_i、I_carry_q为carry_gen模块产生的载频信号,频率为lfm信号的中频,carry_gen模块为简单的一个NCOIP核。ad采样的数据I_ad_data分别于载波相乘并通过一个FIR低通滤波器后输出数字下变频后的数据O_signal_i、O_signal_q。为了确保后续的FFT模块数据有效范围内有lfm信号,ddc输出数据是否有效O_signal_valid由ctrl_signal模块的采样使能O_sample_ena决定,而采样使能由lfm_gen输出的同步信号O_ctrl_idle控制。最后O_signal_start与O_signal_end分别为给fft模块的数据有效范围的起始和终止信号。

4.2.4 abs:FFT输出值求幅值模块

其中I_data_i、I_data_q为FFT IP核输出的完成2048点FFT后的数据。由于只要定性的显示幅频特性曲线,为了减少资源的占用以及程序的复杂度,所以只对数据进行了平方相加运算,没有进行开根号运算,这样可以大大减少处理的延时。I_cut由船型开关控制,调整输出数据的截位为合适的符号位。

4.2.5 phase_calc_cordic:相位计算模块

坐标旋转数字计算机CORDIC(COordinate Rotation DIgital Computer)算法,通过移位和加减运算,能递归计算常用函数值,如Sin,Cos,Sinh,Cosh等函数,由J.Volder于1959年提出,首先用于导航系统,使得矢量的旋转和定向运算不需要做查三角函数表、乘法、开方及反三角函数等复杂运算。J.Walther在1974年用它研究了一种能计算出多种超越函数的统一算法。

在本实验中,迭代的终止条件为固定次数进行15次迭代,精度可以达到0.0018度。

4.2.6 vga_disp:VGA显示模块

通过开关选择需要显示的数据,通过双口RAM实现乒乓处理操作,在vga读取其中一段ram时,数据将一直对另一段ram进行刷新操作,直到vga刷新一帧,切换段选地址,以此重复刷新。将VGA显示的行地址作为ram读取地址,将读出的数据进行截位并作为像素点的分界线,与数据值相近的列地址附近像素点根据数值赋予不同颜色深度的RGB888像素值,其他赋予全1(白色)。

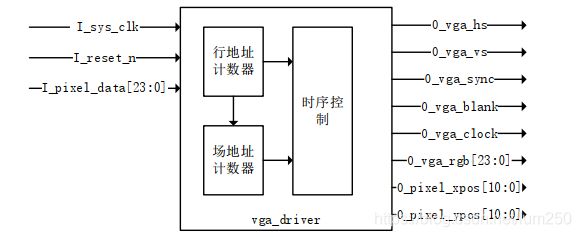

4.2.7 vga_driver:VGA驱动模块

VGA驱动模块在像素时钟I_sys_clk(64MHz)的驱动下,根据VGA时序的参数输出行同步O_vga_hs、场同步O_vga_vs信号。同时VGA驱动模块还需要输出像素点的纵横坐标,供VGA显示模块vga_disp调用,以绘制图案。

4.2.8 abs_cur_key_ctrl:VGA显示截位模块

首先采用延时采样的方法对按键的值进行消抖操作,然后根据不同按键的有效值对截位计数器进行加、减和复位操作,并输出当前截位值。

4.2.9 lcd1602_disp:LCD1602显示模块

通过一个状态机完成循环刷新,每次更新指令地址后,将指令查找表对应的指令或数据传递给驱动模块完成数据的发送,

4.2.10 seg7_disp:数码管显示模块

seg7_disp模块比较简单,就是将给每个数码管分配需要现实的数据,然后根据数据选择不同的编码并进行输出即可,注意数码管是共阳结构,FPGA输出低电压的时候,对应的字码段点亮。

4.3 基于Modelsim的RTL级仿真

在top模块中选择仿真模式,输入的参数如下表所示:

| 参数 | 值 | 单位 |

|---|---|---|

| W_tao | 32’d2 | us |

| W_bandwidth | 32’d5 | MHz |

| W_prp | 32’d10 | us |

| W_f_carry | 32’d5 | MHz |

| W_amplitude | 32’d13 | / |

| W_fir_mode | 32’d0 | / |

从上图可得,LFM按正常的时序产生了线性调频脉冲信号,并且在每个脉冲的起点输出了一个长度为三个时钟的同步信号,这与我们的预设相符。

从上图可得,DDC模块首先将ad信号与载波信号相乘,由于FIR IP核在仿真时存在bug,所以直接输出为滤波前的结果。在脉冲周期开始处,会输出一个指示数据开始的脉冲信号O_signal_start,数据有效指示信号O_signal_valid拉高。当有效数据长度达到2048点时,输出一个指示数据结束的脉冲信号O_signal_end。这与我们预设的功能相符。

- vga_driver模块仿真结果

从上图可知,VGA驱动模块在像素时钟的驱动下,根据VGA时序的参数输出行同步、场同步信号。同时VGA驱动模块还输出了像素点的纵横坐标,并根据像素值绘制彩色的像素点。

4.4 测试结果

4.4.1 LFM脉冲信号的产生

通过In-System Sources and Probes Editor功能来设置的值,使得这些参数在某些范围内变化,进而实现LFM信号的可控性。Source的编号与参数含义见表4–4 控制协议。

DAC的A通道输出DDS产生的LFM信号,B通道输出LFM信号经过滤波器滤波后的信号,用示波器观察两个通道输出的信号。同时,也可用QuartusII中的signaltap工具抓取产生的LFM信号,判断是否产生了正确的LFM信号。

- 设置如下参数(时):

示波器观测到的时域信号为:

频域信号为:

示波器显示脉宽为1us,脉冲重复周期为10us,带宽为5MHz,中频为5MHz的LFM脉冲信号,这与我们预设的值相符,验证了LFM产生功能的正确性。

- 改变脉冲重复周期、载波频率及带宽,设置如下参数(时):

示波器观测到的时域信号为:

频域信号:

示波器显示脉宽为4us,脉冲重复周期为20us,带宽为10MHz,中频为20MHz的LFM脉冲信号,这与我们预设的值相符,验证了参数改变功能的正确性。

4.4.2 FIR滤波器测试

使用QuartusII中的调试工具In-System Sources and Probes Editor来实时切换FIR滤波器的冲击响应。输入的滤波器编号与其对应的截止频率见表4–5。

为了测试所有滤波器的滤波效果,设置载频为25MHz,带宽为50MHz,使得信号频率范围为0~50MHz。即设置参数如下:

-

设置滤波器编号为0(Fc=5MHz,Fa=10MHz)

图 4–21 时域波形 从上图可知,滤波后波形高频的部分幅度变低了,说明信号的高频部分被滤波器滤除了。波形不为0的宽度约为0.8us,由于波形为线性调频信号,可以估算滤波器截止频率为: 这与滤波器阻带截止频率相符合图 4–22 时域波形 波形不为0的宽度约为1.6us,由于波形为线性调频信号,可以估算滤波器截止频率为:

这与滤波器阻带截止频率相符合

-

设置滤波器编号为6(Fc=50MHz,Fa=55MHz)

从上图可以看出,带宽内的信号都通过了滤波器。

4.4.3 ADC信号频谱分析结果

首先连接DA扩展板上的DAC-DA口ADC-DB口,这时,便能采集到ADC-DB口的信号。然后利用QuartusII的NCOip核设计本振信号(频率为LFM信号的载波频率,是一个可变值),对采集到的信号作正交下变频处理,并经过低通滤波,得到零中频复信号。最后,对零中频信号作FFT,得到被分析信号的幅频特性和相频特性。

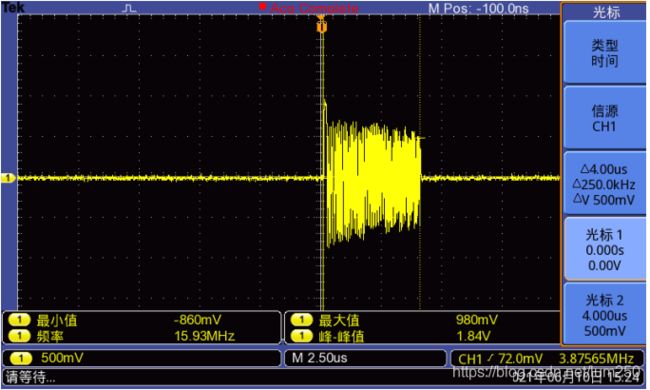

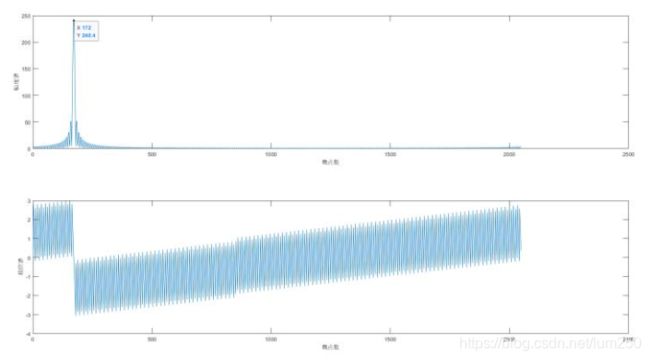

为了测试FFT相关模块的功能,首先设置LFM中频为15MHz,然后通过信号源产生频率为20MHz的点频信号,AD的通道A采集到的的信号为:

正交下变频输出:

幅度谱与相位谱输出:

从上图可以看出,FFT幅度谱尖峰在第335点,由于signalTap

II信号参考时钟为120MHz而fft时钟为60MHz,所以这个尖峰对应的频率为:

与理论值的误差为:

符合实验要求。

用matlab分析5MHz的点频信号的幅度谱和相位谱结果如下:

从上图可以看出,相位谱理论值与FPGA计算的结果变化规律类似,如果需要进一步的验证,需要将signalTap

II的数据导出比对分析。

4.4.4 拓展1:VGA显示测试

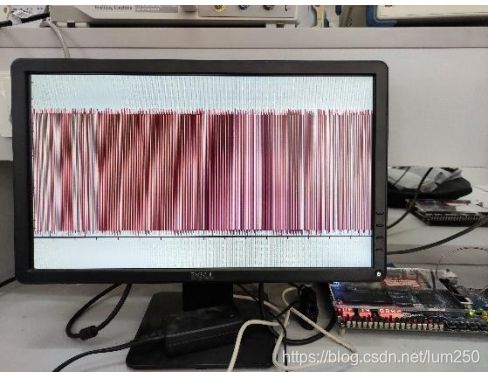

通过控制协议表 4–4指定的开关,选择VGA显示的模式,各模式的显示效果如下:

-

显示LFM波形模式

工作于LFM波形显示模式时,显示的点数也是可调的,由于显示器分辨率为1024*768,分别可以通过开关显示1024,2048,4096,8192点的时域波形,当然为了在1024点宽的显示器显示8192点的波形,必须通过抽取操做,这也会导致显示效果有一定程度的失真。

图 4–28 (a)1024点显示效果;(b)2048点显示效果;(c)4096点显示效果;(d)8192点显示效果 -

显示幅度谱模式

图 4–29 (a)点频信号频谱;(b)LFM信号频谱 从上图可以看出,除了具有坐标轴显示功能外,像素点还会根据数值的大小显示不同颜色,具有很好的视觉效果。

-

显示相位谱模式

相位谱的显示效果比较欠缺,有符号的数值与像素点的坐标的映射关系还做的不够好,这一点后面可以优化。

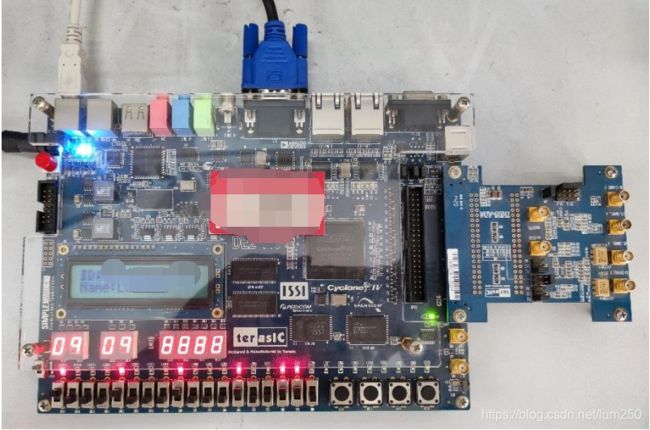

4.4.5 拓展2:LCD与数码管显示测试

从上图可以看出,LCD1602显示了学生姓名与学号,7段数码管分别显示了

中频(2位)、带宽(2位)、VGA输出数据截位(1位)、FFT幅频截位(1位)以及FFT相频截位(1位)。

每个LED灯也与船型开关的值对应,当开关的值为1时,对应位置的LED被点亮,反之开关为0则熄灭。

5 思考与讨论

5.1 遇到的问题及解决

在本次试验中,第一次使用 QuartusII软件进行Verilog HDL的设计,一开始犯了很多低级错误,通过不断的熟悉软件,渐渐减少了这些错误的发生。后面有许多设计上的错误,经过请教老师、同学与查阅资料等方式也都得到了解决。下面是针对一些典型问题的记录。

| 问题 | 解决 |

|---|---|

| 在进行Quartus II与Modelsim的联合仿真时,Modelsim无法正常加载仿真。 | 首先尝试把Modelsim版本换成Quartus II13.1配套的版本:Moselsim-altera 10.1d。仿真工程可以正常加载进去了,但是还是无法仿真。 然后经过查阅资料,发现需要把NCO与FFT IP核的.VO文件单独编译,然后可以正常仿真了,但是FIR还是报错,实在解决不了FIR的bug,只能 在仿真的时候跳过FIR了。 |

| 问题 | 解决 |

|---|---|

| FIR无法导入matlab生成的数据。 | 数据的格式不对,每个数据需要用逗号或者空格隔开。 |

5.2 实验的收获与感受

第一次使用altera系得片子实现这种复杂度的工程,还是收获挺多的,其中也有一些对altera的抱怨以及感悟,从使用它们的IDE可以体会到跟大哥Xilinx的差距,或许这也可以启发我们,做产品或者软件一定要有同一的标准,从用户的角度出发。End

5.3 未来的期望与要求

由于调试的时间比较仓促,部分功能调试的还不是很完善,还有如下方面可以进一步完善:

-

LCD1602显示部分:可以通过实时对需要显示的参数进行解码从而实现动态刷新,现在只实现了静态显示,还是挺遗憾的。

-

VGA对相频特性的显示:对有符号数的支持还不是很完善,需要加一个是否是有符号数的指示位,然后对幅值之类的无符号数以及相位之类的有符号数分开进行处理和显示。

-

VGA显示LFM波形部分,其实框架以及搭好了,还可以通过切换来显示下变频后等波形,毕竟只是改变写入RAM的数,并不会增加资源的消耗。

-

VGA显示波形部分:是不是可以增加类似示波器的控制呢?或许可以直接实现一个低指标的示波器。