STA环境

目录

- 1. CMOS逻辑门

- 2. 波形

- 3. 时钟

- 4. 时序路径

- 5. 外部属性

-

- 5.1. 输入端外接电阻

- 5.2. 输出端外接电容

- 6. SDC对象访问指令

-

- 6.1. 如何描述对象

-

- `*`

- `-hier`

- `-filter`

- `-of`

- `-regexp`

- `-nocase`

- 6.2. `all_clocks`、`get_clocks`

- 6.3. `all_inputs`、`all_outputs`、`get_ports`

- 6.4. `get_cells`

- 6.5. `get_nets`

- 6.6. `get_pins`

本文介绍在执行静态时序分析(Static Timing Analysis, STA)前需要配置的环境,并附上设计约束(Synopsys Design Constraints, SDC)如何描述

aaaaaaaa585 - vivado - CSDN专栏

1. CMOS逻辑门

CMOS逻辑门使用NMOS和PMOS晶体管搭建而成。如下图给出了CMOS非门的示例。

什么是MOS晶体管?MOS晶体管工作原理和VI特性详解

CMOS非门有两种稳定状态,具体取决于输入的电平状态。

当输入A为低电平(Vss或逻辑0)时,NMOS晶体管截止、PMOS晶体管导通,输出Z电平被上拉至逻辑为1的Vdd。

当输入A为高电平(Vdd或逻辑1)时,NMOS晶体管导通,而PMOS晶体管截止,输出Z电平被下拉至逻辑为0的Vss。

在CMOS逻辑门中,输出节点通过上拉结构(由PMOS晶体管构成)连接至Vdd,并通过下拉结构(由NMOS晶体管构成)连接至Vss,来构成输出的高电平和低电平。同时上拉和下拉结构是互补的,如果上拉结构开启,则下拉结构将关闭,反之相反。以此保证输出电平只有高电平和低电平两种情况,无一例外。

基于此,可将各种CMOS逻辑门级联起来以实现更复杂的逻辑功能。

而这些CMOS逻辑门可以组合成各种基本逻辑块或称标准单元,例如与或非门、异或门、触发器等等。这些标准单元是预先设计好的,可供设计人员搭积木式的组合拼凑,实现各种功能。

2. 波形

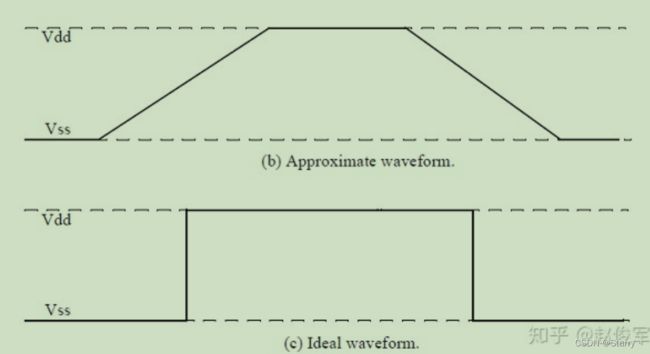

CMOS单元电平随时间变化构成了波形,波形如下图所示,

但在仿真或理想情况下常将波形等效为如下的折线。

3. 时钟

STA环境 - 时钟

4. 时序路径

STA环境 - 时序路径

5. 外部属性

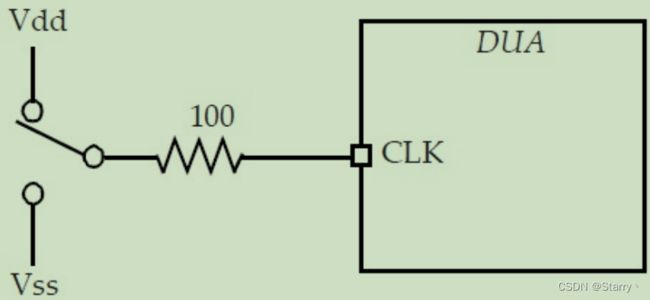

5.1. 输入端外接电阻

可通过指定输入端的外接电阻值,以计算输入端的过渡时间,反应驱动强度。理想情况下外接电阻值为0、过渡时间为0、驱动强度为无穷大

指令如下

# 指定外接电阻

set_drive 100 UCLK

set_drive -rise 3 [ all_inputs ]

set_drive -fall 2 [ all_inputs ]

# 指定输入端口类型

set_driving_cell -lib_cell INV3 -library slow [ get_ports INPB]

set_driving_cell -lib_cell INV2 -library tech13g [ all_inputs ]

set_driving_cell -lib_cell BUFFD4 -library tech90gwc [ get_ports {testmode[3]}]

# 指定输入端口过度时间

set_input_transition 0.85 [ get_ports INPC]

set_input_transition 0.6 [ all_inputs ]

set_input_transition 0.25 [ get_ports SD_DIN*]

5.2. 输出端外接电容

同样会影响输出端口的延迟

# 指定输出端口电容值

set_load 5 [ get_ports OUTX]

set_load 25 [ all_outputs ]

set_load -pin_load 0.007 [ get_ports {shift_write[31]}]

# 指定内部网络电容值

set_load 0.25 [ get_nets UCNT5/NET6]

6. SDC对象访问指令

上述主要介绍约束指令,约束指令需要指定访问对象,此处介绍对方访问指令

ug835 - vivado tcl commands

Vivado时序约束中详细的Tcl命令

6.1. 如何描述对象

介绍指令之前,先介绍如何描述对象的名称。SDC支持直接描述对象,也支持通过正则表达式、搜索条件等描述所有满足条件的对象。

直接描述对象,需要指明模块层级。

[get_pins {clk_gen_i0/clk_core_i0/CK}]

具体的模块层级可在vivado中的Open Implemention Design中查看

也可以通过限定条件描述所有满足条件的对象,下面介绍。

*

可以使用*描述该层级的子模块或对象。注意只能描述该层级,不包括更深的层级,也不能表示无层级。

# 获取顶层模块中,所有包含uart字符模块下 的所有pins

get_pins {*uart*/*}

# 获取U_UART模块中 所有子模块中名字包含rst的pins

# 注意没有获取:U_UART.rst和U_UART下子模块的子模块的rst信号

get_pins {U_UART/*/*rst*}

# 获取顶层模块的所有pins

get_pins *

-hier

加上该条件,将从工程顶层开始,在所有层次内搜索对象。如果没有该条件,则只会搜索顶层模块中,或者是current_instance约定的模块中的对象。

注意get_ports、get_clocks不能使用-hier

例如

# 所有层级下名字包含rst_global_reg的cells

get_cells -hier *rst_global_reg*

# U_CFG模块下所有层级中 名字包含rst_global_reg的cells

get_cells -hier U_CFG/*/*rst_global_reg*

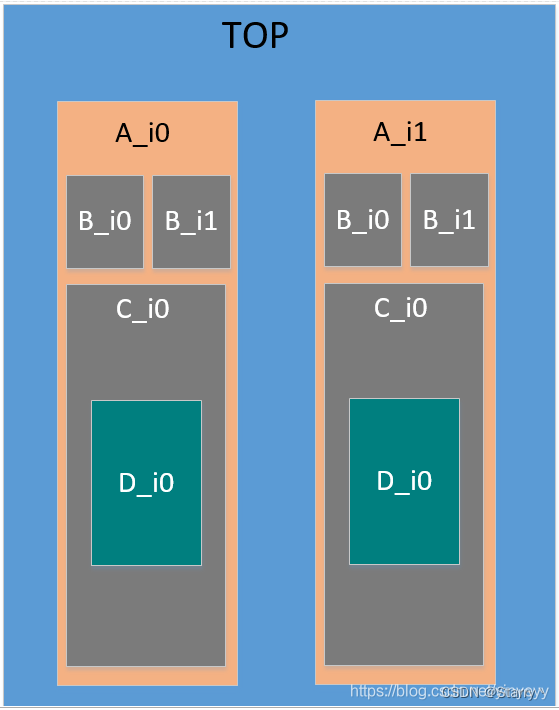

关于*和-hier的区别,例如下图中。所有模块中都有一个rst信号。

加了-hier之后*就可以跨层级了。

# 将获取 A_i0.B_i0.rst_reg、A_i0.B_i1.rst_reg、A_i0.C_i0.rst_reg

get_cells A_i0/*/*rst_reg

# 将获取 A_i0.B_i0.rst_reg、A_i0.B_i1.rst_reg、A_i0.C_i0.rst_reg和A_i0.C_i0.D_i0.rst_reg

# 加了-hier之后此处*可代表跨层级

get_cells -hier A_i0/*/*rst_reg

# 将获取 A_i0.rst_reg、A_i0.B_i0.rst_reg、A_i0.B_i1.rst_reg、A_i0.C_i0.rst_reg和A_i0.C_i0.D_i0.rst_reg

# 加了-hier之后此处*可代表跨层级

get_cells -hier A_i0/*rst_reg

正则表达式在Vivado约束文件(xdc)中的应用

-filter

表示根据属性搜索对象,需要通过大括号将属性涵盖进来,例如

# 当前模块中所有名字带有RST的输入pin

get_pins * -filter {DIRECTION == IN && NAME =~*RST*}

# 获取所有时序逻辑单元

get_cells * -hier -filter {IS_SEQUENTIAL== 1}

实际上,pins、ports、cells的属性各不相同,但-filter常用的有包括

==等于、!=不等于、=~匹配、!~不匹配、

> < >= <=不等号、

&& ||与或逻辑符、

DIRECTION == IN; DIRECTION ==OUT输入输出、NAME名称

-of

获取对象的某个类型的对象,例如

# 获取clk_gen_i0/clk_core_i0模块的输入引脚

get_pins -of [get_cells {clk_gen_i0/clk_core_i0}] -filter {DIRECTION == IN}

# 已知引脚名获取所在模块

get_cells -of [get_pins clk_gen_i0/clk_core_i0/clk_in1_n]

# 已知模块名获取与该模块相连的网线

get_nets -of [get_cells {clk_gen_i0/clk_core_i0}]

# 已知引脚名获取与该引脚相连的网线

get_nets -of [get_pins clk_gen_i0/clk_core_i0/clk_rx]

# 已知时钟引脚获取时钟引脚对应的时钟

get_clocks -of [get_pins clk_gen_i0/clk_core_i0/clk_rx]

-regexp

使用正则表达式描述对象。

常用的规则,例如*表示匹配前面的子表达式零次或多次、.表示匹配除换行符 \n 之外的任何单字符、?表示匹配前面的子表达式零次或1次。因此可使用.*表示任意数量的任意字符

正则表达式在Vivado约束文件(xdc)中的应用

-nocase

使用-regexp正则表达式时,不区分大小写

6.2. all_clocks、get_clocks

all_clocks用于指定create_clock生成的所有时钟

# 用于本设计中所有时钟

set_propagated_clock [all_clocks]

get_clocks 用于指定生成的特定时钟。

格式如下

get_clocks [-regexp] [-nocase][-filter <arg>][-of_object] [-include_generated_clocks]

6.3. all_inputs、all_outputs、get_ports

用于指定本顶层设计的端口

get_ports [-regexp] [-nocase][-filter <arg>][-of_object]

6.4. get_cells

用于获取综合后或者是布线后的模块、单元等内容,例如模块、LUT、FDRE等等都叫cell。

get_cells [-hier][-regexp] [-nocase][-filter <arg>][-of_object]

可打开Open Synthesis或Open Implemention后的Netlist中查看什么是cells

6.5. get_nets

用于获取cells之间相连的网线

get_nets[-hier][-regexp] [-nocase][-filter <arg>][-of_object][-top_net_of_hierarchcial_group]

可打开Open Synthesis或Open Implemention后的Netlist中查看什么是nets。某个cell的Cell Properties中也会列出与该cell相连的Nets

6.6. get_pins

用于获取cells上面的引脚

get_pins[-hier][-regexp] [-nocase][-filter <arg>][-of_object][-leaf]

可打开Open Synthesis或Open Implemention后的Netlist中选中某个cell,其Cell Properties中也会列出该cell的Cell Pins