ICer技能03Design Compile

目录

- 1.简介

- 2.三个大过程

- 3.DC具体流程

- 4.实际过程

-

- 4.1 打开DC

- 4.2 设置寻找路径

- 4.3 指定工艺库

- 4.4 指定设计文件

- 4.5 添加时序约束

- 4.6综合优化

- 4.7 查看报告

- 4.8 输出

- 5. 脚本运行

- 6.实战

1.简介

Design Compile是完成RTL代码编写且功能仿真之后的逻辑综合工具,其作用就是将前端设计工程师编写好的RTL代码,映射到指定的工艺库上,通过约束、优化,形成门级网表文件

2.三个大过程

- translation:将Verilog转化为GTECH网表

- gate mapping:再配合工艺库生成门级网表

- logic optimization:根据约束eda工具会做一些力所能及的优化

3.DC具体流程

- 指定工艺库(.db .lib)指定设计文件(.v)

- 添加时序约束(timing constraints)以及设计规则约束(design rules constraints,包括限载模型、功耗、面积等约束)

- 进行综合

- 分析:时序报告、面积报告、功耗报告等

- 导出ddc网表给到后端

4.实际过程

4.1 打开DC

当然打开前要先安装好DC工具。

-

使用界面打开

design_vision -

使用命令行打开

dc_shell -

使用tcl脚本

dc_shell -f syn.tcl | tee -i sys.log

4.2 设置寻找路径

-

DC会寻找search_path目录中指定的设计和库文件

-

通常包括Verilog、库和脚本的目录

-

用户可以将目录添加到默认列表中

set_app_var search_path "$search_path" ./rtl ./scripts ./libs"

4.3 指定工艺库

需要指定的库有两个

-

target library:生成门级网表用的,如台积电的90nm工艺库

set_app_var target_library 90nm_typical.db -

link library:一般和target library一样,修改工艺的时候用到link

set_app_var link library "* 90nm_typical.db" set_app_var link library "* $target_library " //将原有的工艺改为90nm工艺

4.4 指定设计文件

这里需要注意顶层(TOP)文件的设置

read_verilog "TOP.v a.v b.v c.v"

多个.v文件时设置顶层

current_design TOP(这个TOP是指模块的名字而不是文件的名字)

4.5 添加时序约束

时钟周期为2个时间单位,时间单位一般为ns

clock period create_clock -period 2 [get_ports ClK]

时钟误差±0.3

clock skew set_clock_uncertainty -setup 0.3 [get_clocks CLK]

时钟从0-1 1-0的变化时间max设置0.15

clock transition set_clock_transition -max 0.15 [get_clocks CLK]

晶振到CLK的延迟时间设置0.7

clock latency set_clock_latency -max 0.7 [get_clocks CLK]

IO口A输入延迟设置0.6

set_input_delay -max 0.6 -clock CLK [get_ports A]

IO口B输出延迟设置0.8

set_output_delay -max 0.8 -clock CLK [get_ports B]

IO口A输入从1-0 0-1延迟设置0.12

set_input_transition 0.12 [get_ports A]

4.6综合优化

综合时会自动进行优化,而优化包括以下3个方面:

- 架构优化

- 逻辑优化

- 门级映射优化

在满足时序约束的条件下,把面积做到最小,指令:

compile

compile_ultra //更大力度优化,时间更久

4.7 查看报告

包括前面说的时序、面积等

report_qor //report quality of result

report_timing

4.8 输出

-

sdc约束文件

-

ddc文件:网表+sdc的产出

-

gv文件:后仿真用到

-

sdf文件:时延文件,后仿真用到

write_sdc design.sdc write -f ddc -hier -output ddc.ddc write f verilog -hier -outout design.gv

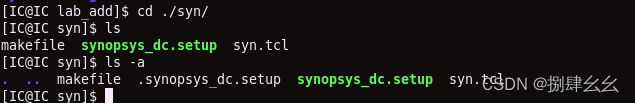

5. 脚本运行

上面说了这么多,那么脚本怎么跑呢?

- .synopsys_dc.setup :决定两个工艺库和路径

- syn.sdc:约束文件

- syn.tcl:真正的脚本文件

- 最后运行

dc_shell -f syn.tcl | tee -i sys.log

6.实战

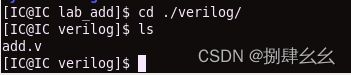

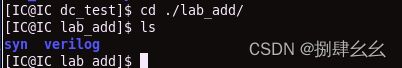

①首先工程文件夹dc_test

②接着建立lab_add和library文件夹

③然后在lab_add下建立测试文件夹verilog和综合文件夹syn

④在verilog中添加文件add.v

module add

(

input a,b,c_in,

output sum,c_out

);

assign sum = a ^ b ^ c_in;

assign c_out = (c_in & b)|(a & b)|(a & c_in);

endmodule

-

启动时选择工艺库的文件.synopsys_dc.setup,这个文件要用ls -a查看,内容如下

set design "sj" set company "s725" set_app_var search_path ". $search_path ../../library" set_app_var target_library typical.db set_app_var link_library "* typical.db" set symbol_library tsmc13fsg_6lm.sdb define_design_lib syn_ws -path ./syn_ws -

没啥用的synopsys_dc.setup文件(我不知道有什么用,会优先选择.开头的文件)

-

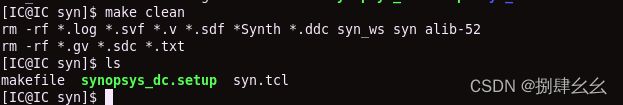

makefile文件,只写了clean一个功能,用make clean 来清理产生的文件,内容如下:

clean: rm -rf *.log *.svf *.v *.sdf *Synth *.ddc syn_ws syn alib-52 rm -rf *.gv *.sdc *.txt -

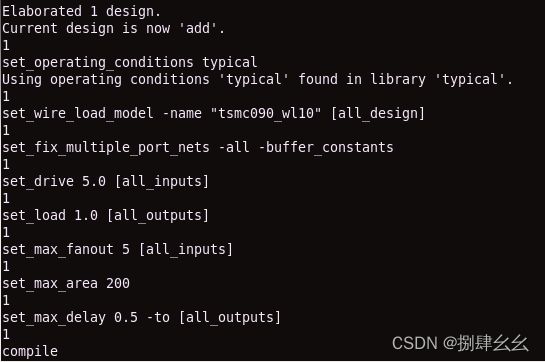

还有最重要的tcl文件,用来写约束,读取.v文件,设置限载模型,生成报告和其他文件等,内容如下:

set design "sj" set company "s725" set_app_var search_path ". $search_path ../../library" set_app_var target_library typical.db set_app_var link_library "* typical.db" set symbol_library tsmc13fsg_6lm.sdb define_design_lib syn_ws -path ./syn_ws analyze -work syn_ws -format verilog ../verilog/add.v elaborate -work syn_ws add set_operating_conditions typical set_wire_load_model -name "tsmc090_wl10" [all_design] set_fix_multiple_port_nets -all -buffer_constants set_drive 5.0 [all_inputs] set_load 1.0 [all_outputs] set_max_fanout 5 [all_inputs] set_max_area 200 set_max_delay 0.5 -to [all_outputs] compile report_timing report_area write -hierarchy -format ddc write -hierarchy -format verilog -output add_netlist.v write_sdf add.sdf exit -

理论上还有一个sdc的约束文件,但是我们这里综合的是纯组合逻辑电路一位全加器,所以时钟方面的约束并没有,上面tcl脚本中也给了一定的约束项

⑥在library下放入我们的工艺库文件(没有的可以私信我要),有如下几个文件,其中.db文件是给dc工具看的(打开是乱码),.lib文件是给我们开发者看的

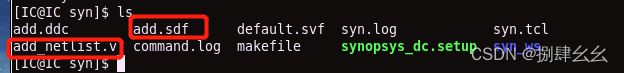

dc_shell -f syn.tcl | tee -i syn.log

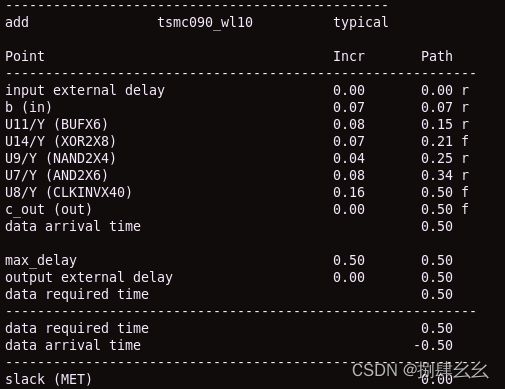

当然你不打后面的管道符命令也行,运行部分结果如下:

⑧这时候我们ls以下看看生成了什么新文件,红色框的是给到后端工程师用的