计算机组成原理习题-1

前言

本文通过记录几道题目,回顾和总结存储器、总线等计算机组成原理相关知识。内容涵盖闪速存储器、总线传输过程、CPU响应中断、存储保护等问题的解析,以及关于Cache、指令格式、微程序等的计算机系统设计案例,答案来自网络搜集和ChatGPT,可能不完全正确

一、回答下列问题

1. 什么是闪速存储器?它有哪些特点?

闪速存储器是高密度、非易失性存储器,可以用于存储数据和程序代码。从原理上看,它属于ROM,但是它又可随机改写信息;从功能上看,它又相当于RAM,所以传统ROM与RAM的定义和划分已失去意义。因而它是一种全新的存储器技术。 闪速存储器的特点为固有的非易失性、廉价的高密度、可直接执行和固态性能。

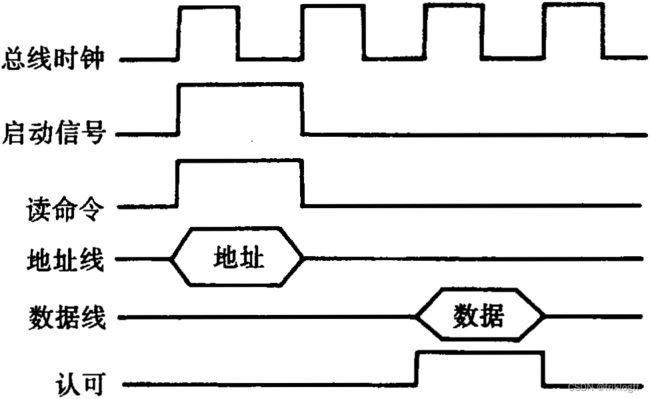

2. 总线的一次信息传送过程大致分为那几个阶段?若采用同步定时协议,请画出读数据的同步时序图。

分五个阶段:请求总线,总线仲裁,寻址(目的地址),信息传送,状态返回(错误报告),如图所示:

3. CPU 响应中断应具备哪些条件?

(1) CPU内部设置的中断屏蔽触发器必须是开放的。

(2) 外设有中断请求时,中断请求触发器必须处于“1"状态,保持中断请求信号。

(3) 外设(接口)中断允许触发器必须为“1",这样才能把外设中断请求送至CPU.

(4) 当上述三个条件具备时,CPU在现行指令结束的最后一个状态周期响应中断。

4. 什么是存储保护,通常采用什么方法?

当多个用户共享主存时,为使系统能正常工作,应防止由于一个用户程序出错而破坏其它用户的程序和系统软件,还要防止一个用户程序不合法的访问不是分给它的主存区域。为此,系统提供存储保护。通常采用的方法是:存储区域保护和访问方式保护。

5.何为通用串口I/O标准接口IEEE1394?简述其性能特点?

IEEE1394是串行I/O标准接口。与SCSI并行I/O接口相比,它具有更高的数据传输速率和数据传送的实时性,具有更小的体积和连接的方便性。IEEE1394的一个重大特点是,各被连接的设备的关系是平等的,不用PC介入也能自成系统。因此IEEE1394已成为因特尔、微软等公司联手制定的PC98系统设计指南的新标准。

二、设某计算机的cache-主存层次采用4路组相联映像方式,已知cache容量为32KB,主存容量为2MB,页面大小为16个字,每个字有32位,请问:

- 主存地址多少位(按字节编址)(1分);各字段如何划分(各需多少位)?

- 设cache起始为空,CPU从主存单元0、1、2、…80,依次读出81个字(主存一次读出一个字并重复按此次序读出10次),问命中率为多少?若cache速度是主存的5倍,问采用cache与无cache比较速度提升多少倍?

解:

(1) 主存容量为2MB,所以主存地址为21位(2^21字节)。各字段划分为:

主存地址:21位

页号:12位

页内偏移:9位

(2) 一开始cache无内容,第一轮全部不命中,以后九次全部命中,所以命中率是:9/10=90%

设cache读取时间为1,主存读取时间为5,

- 无cache的访问时间:10×5=50

- 有cache访问时间:第一次先访问cache,再访问主存,时间为1×(1+5),后9次只访问cache,时间为9×1

- 所以有cache的访问时间是9×1+1×(5+1) =15

所以速度提高的倍数是50/15=3.33倍

三、一台处理机具有如下指令格式

[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-btL2nl8N-1690460815963)(https://user-images.githubusercontent.com/45189006/221377482-c6ba31db-c819-43e9-a4c9-c16393a8ad87.png)]

格式表明有8个通用寄存器(长度16位),X指定寻址模式,主存实际容量为256K字。

- 设不用通用寄存器也能直接访问主存中的每一个单元,并假设操作码域为OP=6位,请问地址域应分配多少位?指令字长度应为多少位?

- 假设X=11时,指定的通用寄存器用做基址寄存器,请提出一个硬件设计规划,使得被指定的通用寄存器能访问1M主存空间中的每一个单元。

答:

(1) 主存256K字,每个字2字节,所以主存容量是256K * 2 = 512K字节 = 2^18字节。

采用字节寻址,需要18位地址码才能寻址每个字节。

操作码字段OP 6位。

所以指令长度应该是:18 + 3 + 3 + 6 + 2 = 32位

(2) 此时指定的通用寄存器用作基址寄存器(16位)但16位长度不足以覆盖1M字地址空间所以将通用寄存器左移4位低位补0形成20位基地址然后与指令字形式地址相加得有效地址,可访问主存1M地址空间中任何单元

四、某机采用微程序控制方式,已知全机有48个微命令,控制存储单元1024个,条件测试字占5位。

- 若采用直接控制的水平型微指令,请设计微指令的具体格式,并标明微指令字长。

- 若采用编码控制的水平型微指令,已知48个微命令构成4个相斥类,分别包含4个,16个,6个和22个微命令,其他条件不变,请设计微指令的具体格式,并标明所采用的译码器类型及微指令字长。

解:

1.采用直接控制的水平型微指令:

48条微命令需要48位,控制存储器容量为1024,即地址位为10位,加上条件测试字5位,则微指令位数总共为:

48 + 10 + 5 = 63

具体格式为:

2.采用编码控制的水平型微指令:

4个微命令需要2位,16个微命令需要4位,6个微命令需要3位,22个微命令需要5位,所以4类相斥微命令共需要14位。

控制存储器10位加上5位条件测试字,所以微指令位数总共为:

14 + 10 + 5 = 29

具体格式为:

![]()

总结

通过回答存储器、总线、中断、保护等计算机组成原理相关问题,并完成Cache、指令格式、微程序控制等计算机系统设计案例,全面复习和掌握了这部分知识要点。这为我们进一步学习更高级的计算机系统原理奠定了基础。