Arm Cortex R52与TC3xx Aurix上下文切换对比

目录

1.Arm Cortex R52上下文切换

2.英飞凌TC3xx的CPU上下午切换

2.1 上下文类型

2.2 Task Switching Operation

2.3 Context管理寄存器

2.4 各种事件的上下文切换

2.4.1 中断/Trap的上下文切换

2.4.2 函数调用的上下文切换

2.4.3 FCALL/FRET的上下文切换

2.5 Context Save、Restore操作

2.6 Context 切换性能特性

1.Arm Cortex R52上下文切换

R52采用Armv8-r 架构,因此根据Arm® Architecture Reference Manual Supplement Armv8:

- 发生异常

PE(Process element)将状态上下文保存到SP寄存器指向的堆栈。

保存的上下文状态如下:

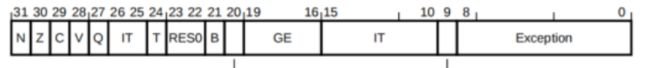

- RETPSR:Combined Exception Return Program Status Registers

- ReturnAddress.

- LR(R14):Link Register

- R12(General-Purpose Register)

- R3-R0.

- Task上下文切换

按照发生异常时硬件存储的内容,使用汇编代码来实现;

2.英飞凌TC3xx的CPU上下午切换

在嵌入式实时控制系统中,任务是一个独立的控制线程。任务的状态由其上下文定义。当一个任务被中断时,处理器使用该任务的上下文重新启用该任务的继续执行。

2.1 上下文类型

上下文类型可以分为:

- Upper Context:

- upper地址寄存器A[10]--A[15];

- upper数据寄存器 D[8]--D[15];

- PCXI

- PSW

- Lower Contex:

- Lower 地址寄存器A[2]--A[7]

- Lower 数据寄存器D[0]--D[7]

- A[11] Return Address

- PCXI

上下文存放在内存中,占16word,被称为Context Save Areas,举例如下:

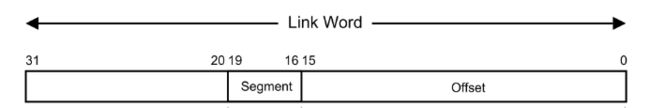

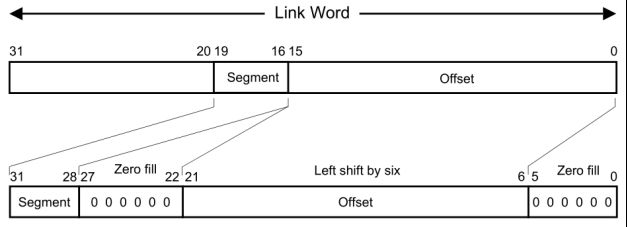

CSA使用的是固定大小的链表,通过LinkWord进行连接,从上图可以看到,LinkWord和PCXI的布局都在同一位置,而LinkWrod结构如下图所示:

根据芯片手册上PCXI的描述

可以看到LW只关注Segment和Offset,PCXI不仅关注上述内容,还要关注Context Tag、PIE和PCPN。

LW只关注Segment和Offset的原因是用于生成链接CSA的有效地址,生成方式如下:

2.2 Task Switching Operation

从上表可以看到,上述7种事件或指令触发时,upper/lower context会被保存或恢复;其中当外部中断、trap或函数调用时,upper context会自动保存;lower context通过软件指令保存。

SAVE操作是通过从LW中读取FCX的下一个值,存储在FCX(Free CSA List Head Pointer)寄存器中;

STORE操作是通过指令的有效地址来进行存储,不需要对CSA list或者FCX寄存器进行更改。

Restore是save的反向操作;load是store的反向操作。

需要注意的是upper和lower contexts在寄存器内容保持的角度上有较大差别。

Upper cotext 寄存器不能保证是静态硬件寄存器,例如函数调用、中断总是从私有的upper context 寄存器开始运行,并且不被继承。

Lower context 寄存器与全局寄存器类似;trap、interrupt、function里看到的值与调用前的寄存器值一样;在上述3个事件里对寄存器值的任何操作会在事件返回后仍然存在。所以可以使用 lower context向调用函数传递参数,并从这些函数里返回值。

2.3 Context管理寄存器

Context save和restore寄存器是context 管理寄存器的指针,如下:

- FCX(Free CSA List Head Pointer)

用于保存free CSA list 头指针,它总是指向一个可用的CSA,结构如下:

FCXO和FCXS一起使用,指向下一个可用的CSA.

- PCX(Previous Context Pointer)

PCX保存了上一个任务的CSA的地址。PCX是PCXI寄存器的一部分。

- LCX(Free CSA List Limit Pointer)

用于识别即将到来的free CSA list损耗。如果发生一个context save操作,并且FCX和LCX的值匹配,则自动识别条件“free context depletion”,完成context保存操作后立即触发FDC trap。LCX结构如下:

2.4 各种事件的上下文切换

2.4.1 中断/Trap的上下文切换

发生上述事件时,处理器首先保存当前任务的upper context到内存中,挂起当前任务,并开始执行中断或者trap。

2.4.2 函数调用的上下文切换

发生此类事件时,必须保存 calling routine的上下文并restore,以便在函数返回后恢复调用方的继续执行。整个硬件来保存upper上下文。此外,可以直接使用指令CALL来进行upper context保存并且调用跳转,RET指令恢复上下文,返回跳转。

2.4.3 FCALL/FRET的上下文切换

在不需要保存和恢复的upper context寄存器的情况下,可以优先使用FCALL指令。该指令执行跳转,并且并行地将当前返回地址A11保存到堆栈中,不保存其他状态

2.5 Context Save、Restore操作

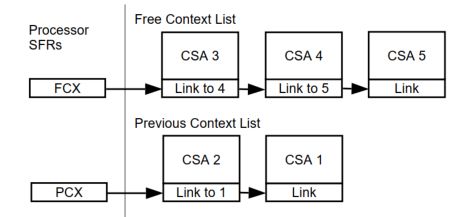

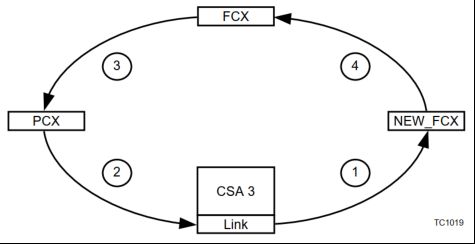

下图展示free 和 previous context 链表如何进行save操作。

上图可以看到FCX指向的是FreeContextList,分别是CSA3-4-5,PCX链表为PCX-CSA2-1。

当发生CSA操作时,FreeContextList的第一个CSA会被拉出放置到previous context list首端。

具体操作如下:

1.CSA3中链接字的内容被加载到NEW_FCX中。NEW_FCX现在指向CSA4。NEW_FX是内部缓冲区,用户无法访问。

2.PCX的内容被写入CSA3的链接字。CSA3链接字现在指向CSA2。

3.FCX的内容写入PCX。PCX现在指向CSA3,它位于先前上下文列表的前面。

4.NEW_FCX加载到FCX中

RESTORE操作为反向操作:

CSA3拉出来存取NEW_PCX,Linkto2给NEW_PCX,FCX中linkto4给CSA3的LW,PCX内容赋给FCX,FCX指向CSA3,NEW_PCX存取PCX。

2.6 Context 切换性能特性

Tricore对函数调用、trap、中断使用统一的上下文切换方式。在所有情况下,任务的Upper context都由硬件自动保存或恢复;对lower context的保存和恢复可由软件实现。上下文存储的位置有不同的性能表现。

CSA存放在DSPR或从DSPR恢复,花费4个cycle;

CSA存放在DLMU或从DLMU恢复,花费8个cycle;

CSA存放在cached 外部内存,最好的情况花费8个cycle。

下表为 CSA控制流指令耗时

实际时间需要根据时钟频率来估算,

例如时钟频率为100MHz,CSA存放在DSPR,产生中断时CSA保存耗费时间为4cycle*1/100000000 = 40ns,restore耗费时间为4cycle*1/100000000 = 40ns,总计80ns。