Verilog学习笔记 HDLBits——Vertors

提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

文章目录

- 前言

- 一、Vectors

-

- 1.Vectors

- 2.Vectors in more detail

- 3.Vertor part select

- 4.Bitwise operators

- 5.Four-input gates

- 6.Vector concatenation operator

- 7.Vector reversal1

- 8.Replication operator

- 9.More replication

- 总结

前言

矢量用于使用一个名称对相关信号进行分组,以使操作更方便。例如,wire[7:0] w;声明一个名为w的8位向量,它在功能上等价于拥有8条独立的w。声明向量时,需将维数(向量由信号组成,所以也可称位宽)放在向量名之前,且一般以 [n-1:0] 的格式来声明n维(位)的向量。注意,vector的声明将维数放在vector的名称之前,这与C语言相比是不同的。

一、Vectors

1.Vectors

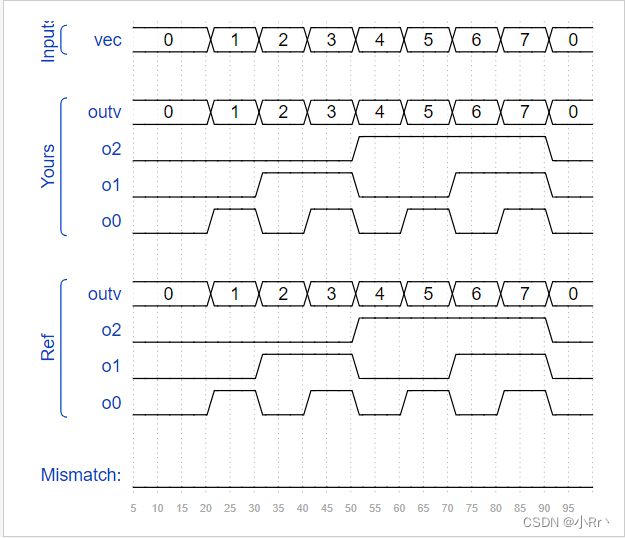

Practice: Build a circuit that has one 3-bit input, then outputs the same vector, and also splits it into three separate 1-bit outputs. Connect output o0 to the input vector’s position 0, o1 to position 1, etc.

翻译:构建一个有一个3位输入的电路,然后输出相同的矢量,并将其分成三个单独的1位输出。将输出o0连接到输入向量的位置0,o1连接到位置1,等等。

Solution(不唯一,仅供参考):

module top_module (

input wire [2:0] vec,

output wire [2:0] outv,

output wire o2,

output wire o1,

output wire o0 );

assign outv = vec;

assign o2 = vec[2];

assign o1 = vec[1];

assign o0 = vec[0];

endmodule

2.Vectors in more detail

Practice:Build a combinational circuit that splits an input half-word (16 bits, [15:0] ) into lower [7:0] and upper [15:8] bytes.

翻译:建立一个组合电路,将输入半字(16位,[15:0])分成下[7:0]和上[15:8]两个字节。

Solution(不唯一,仅供参考):

`default_nettype none // Disable implicit nets. Reduces some types of bugs.

module top_module(

input wire [15:0] in,

output wire [7:0] out_hi,

output wire [7:0] out_lo );

assign out_hi = in[15:8];

assign out_lo = in[7:0];

endmodule

Timing Diagram

3.Vertor part select

Practice:Build a circuit that will reverse the byte ordering of the 4-byte word.

AaaaaaaaBbbbbbbbCcccccccDddddddd => DdddddddCcccccccBbbbbbbbAaaaaaaa

翻译:建立一个电路,反转4字节字的字节顺序,即将abcd转换成dcba。

Solution(不唯一,仅供参考):

module top_module(

input [31:0] in,

output [31:0] out );//

assign out[31:24] = in[7:0];

assign out[23:16] = in[15:8];

assign out[15:8] = in[23:16];

assign out[7:0] = in[31:24];

endmodule

4.Bitwise operators

Practice:Build a circuit that has two 3-bit inputs that computes the bitwise-OR of the two vectors, the logical-OR of the two vectors, and the inverse (NOT) of both vectors. Place the inverse of b in the upper half of out_not (i.e., bits [5:3]), and the inverse of a in the lower half.

翻译:建立一个电路,有两个3位输入,计算两个向量的位或,两个向量的逻辑或,以及两个向量的反(NOT)。把b的反放在out_not的上半部分(也就是比特[5:3]),把a的反放在下半部分。

补充:位运算“&” 1011&1111=1011; 逻辑运算“&&”1011&&1111=1

Solution(不唯一,仅供参考):

module top_module(

input [2:0] a,

input [2:0] b,

output [2:0] out_or_bitwise,

output out_or_logical,

output [5:0] out_not

);

assign out_or_bitwise = a|b;

assign out_or_logical = a||b;

assign out_not[5:3] = ~b;

assign out_not[2:0] = ~a;

endmodule

Timing Diagram

5.Four-input gates

Practice:Build a combinational circuit with four inputs, in[3:0].

There are 3 outputs:

out_and: output of a 4-input AND gate.

out_or: output of a 4-input OR gate.

out_xor: output of a 4-input XOR gate.

翻译:建立一个4输入的与门、或门和异或门。

Solution(不唯一,仅供参考):

module top_module(

input [3:0] in,

output out_and,

output out_or,

output out_xor

);

assign out_and = & in;//或者in[3]&in[2]&in[1]&in[0];

assign out_or = | in;

assign out_xor = ^ in;

endmodule

6.Vector concatenation operator

Practice:Given several input vectors, concatenate them together then split them up into several output vectors. There are six 5-bit input vectors: a, b, c, d, e, and f, for a total of 30 bits of input. There are four 8-bit output vectors: w, x, y, and z, for 32 bits of output. The output should be a concatenation of the input vectors followed by two 1 bits:

翻译:给定几个输入向量,将它们连接在一起,然后将它们分成几个输出向量。有6个5位输入向量:a、b、c、d、e和f,总共有30位输入。有4个8位输出向量:w、x、y和z,对应32位输出。输出应该是两个1位输入向量的串联,如图所示。

提示:可使用连接操作符“{}”;

module top_module (

input [4:0] a, b, c, d, e, f,

output [7:0] w, x, y, z );

assign {w,x,y,z}={a,b,c,d,e,f,2'b11};

endmodule

7.Vector reversal1

Practice:Given an 8-bit input vector [7:0], reverse its bit ordering.

翻译:给定一个8位输入向量[7:0],反转它的位顺序。

Solution(不唯一,仅供参考):

module top_module(

input [7:0] in,

output [7:0] out

);

assign out = {in[0],in[1],in[2],in[3],in[4],in[5],in[6],in[7]};

endmodule

8.Replication operator

Practice:Build a circuit that sign-extends an 8-bit number to 32 bits. This requires a concatenation of 24 copies of the sign bit (i.e., replicate bit[7] 24 times) followed by the 8-bit number itself.

翻译:建立一个电路,将8位数字符号扩展到32位。这需要将符号位的24个副本串联起来(即,将位[7]向左复制24次),然后是8位数字本身。

提示:复制操作符可以将一个向量复制指定次数并将它们连接在一起:{ 复制次数 { 向量 } } 。复制次数必须是个常数,且复制操作符共有两组大括号。

Solution(不唯一,仅供参考):

module top_module (

input [7:0] in,

output [31:0] out );

assign out = {{24{in[7]}},in};

endmodule

9.More replication

Practice:Given five 1-bit signals (a, b, c, d, and e), compute all 25 pairwise one-bit comparisons in the 25-bit output vector. The output should be 1 if the two bits being compared are equal.

翻译:给定5个1bit信号(a、b、c、d和e),在25位输出向量中计算所有25个一对一的1位比较。如果被比较的两位相等,输出应该是1。

Solution(不唯一,仅供参考):

module top_module (

input a, b, c, d, e,

output [24:0] out );//

assign out = ~({{5{a}},{5{b}},{5{c}},{5{d}},{5{e}}}^{5{a,b,c,d,e}});

endmodule

Timing Diagram

总结

1、向量对多个相关信号进行分组,通过向量名可使这些信号更便于操作。向量的声明格式:类型 [高位:低位] 向量名; 如果是在声明输入或输出端口,则需在类型中加上端口的类型。例wire[0:3] w,则w[0]是最高位,w[3]是最低位。

2、在Verilog中,可以通过assign语句或将未声明的内容附加到模块端口来隐式地声明信号。综合器会把未声明的内容隐式地声明成1个bit宽的信号,如果你想把它当向量来用,就会产生bug。可以用宏定义`default_nettype none指令来禁止隐式声明功能。

3、位运算“&” 1011&1111=1011; 逻辑运算“&&”1011&&1111=1

4、题5使用的是缩减运算符,&in 等同于in[0]&in[1]&in[2]…

5、位拼接操作运算符“{}”,用这个运算符可以把两个或多个信号的某些位拼接起来进行运算操作。使用方法:{信号1的某几位,信号2的某几位…};

6、 复制操作符常用来扩展有符号数的位数,并保证其值不变。这可通过将其符号位(最高有效位)复制到它的左边来实现(例如,将4’b0101(符号位为0,值为5)扩展为8位的结果是8’b00000101(值仍为5),将4’b1101(符号位为1,值为-3)扩展为8位后是8’b11111101(-3),注意:这些有符号数是补码的形式,而非原码。

7、“^”是异或.

"~^"是同或。