STM32G474_FDCAN的普通CAN模式使用(寄存器开发)

由于鄙人比较懒,因此本文章只是对 FDCAN 的 经典模式 的简单使用介绍。对于我不需要使用的功能 我就没有深入研究,因此本文只是 CAN 的常用方式的笔记,深入研究的话可以详细阅读手册,本文章没有介绍。

如果有介绍错误的地方,希望各位大佬指正,鄙人一定修改,必要时删除本文章,防止误导他人。欢迎讨论!

例程功能:

波特率250k

接收滤波0x207 0x607 0x601

0.5s发送一次数据

- 发送内容: ID:0x222

- 数据帧

- 标准帧

- 数据长度8

- 内容 78 56 34 12 00 00 00 00

接收数据以中断形势接收,存放到buffer中

目录

- 1. FDCAN的框图

- 2. FDCAN的时钟与波特率

-

- 2.1 fdcan_clk

- 2.2 fdcan_tq_ck

- 2.3 波特率

- 3. FDCAN的地址分布

-

- 3.1 总体分布

- 3.2 Message RAM

- 4. FDCAN中断配置

-

- 4.1 中断寄存器

- 5. FDCAN的筛选器

-

- 5.1 筛选器的特征

- 5.2 11-bit 筛选器的格式

- 6. FIFO模式与Queue模式

-

- 6.1 TX FIFO 的寄存器格式

- 7. FDCAN的初始化

- 8. 发送操作

-

- 8.1 FDCAN帧模式

- 8.2 发送步骤

- 9. 接收操作

- 10. 故障

- 11. 参考资料传送门

-

- 11.1 代码下载(0积分)

- 11.2 其他 CAN 知识了解

- 附录1. FDCAN寄存器配置

- 附录2 发送函数

- 附录3 接收中断程序

FDCAN 与 经典CAN 的最直观差别就是数据帧部分,FDCAN的数据帧波特率可变,并且数据大小不局限于 8 Bytes ,最高支持 64 Bytes 的数据传输。详细差别见 传送门: CAN FD 与 CAN协议区别–简单易懂协议详解 。

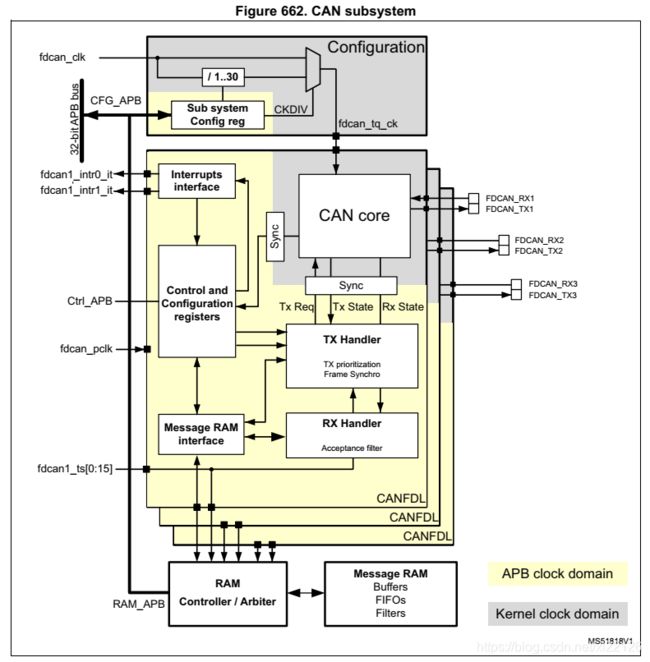

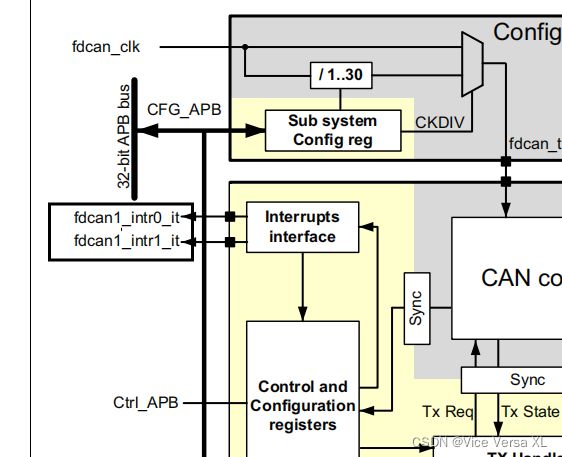

1. FDCAN的框图

根据上图可以看到,FDCAN 有两个时钟域,APB总线接口和CAN内核时钟。FDCAN的波特率取决于内核时钟;寄存器的配置、消息RAM等,走的是APB时钟。FDCAN的APB时钟在RCC_APB寄存器中配置,内核时钟在RCC_CCIPR寄存器中配置(下一章)。

FDCAN有两个中断线,这两个中断线可以单独的打开或关闭,在FDCAN_ILE寄存器中配置。

其他具体介绍参考DM00355726_ENV4手册的1947页(RM0440手册官方下载传送门)。

2. FDCAN的时钟与波特率

2.1 fdcan_clk

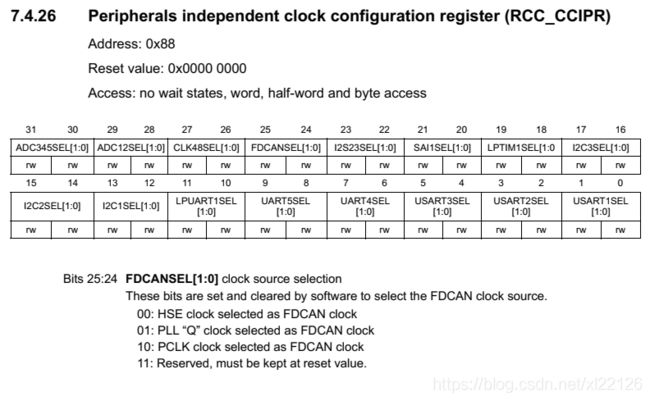

几乎所有通信都可在RCC中配置时钟选择,FDCAN的时钟(fdcan_clk)可在RCC_CCIPR寄存器中进行配置。

FDCAN1/2/3 的内核时钟是通用的,可以在配置FDCAN1的时候,配置 CKDIV 寄存器进行进一步的分频(INIT标志位置位才可配置该寄存器),这里配置的CKDIV影响到 FDCAN2 和 FDCAN3。

2.2 fdcan_tq_ck

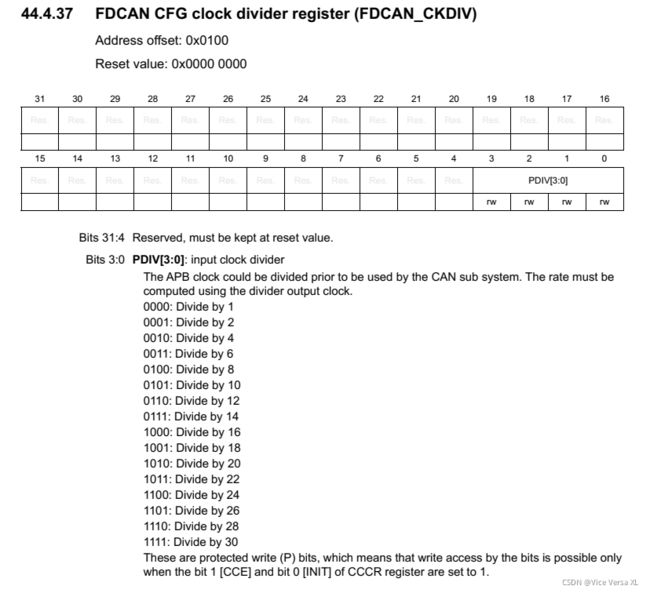

根据系统框图可看到,系统输入的时钟可通过 fdcan_clk 分频得到 fdcan_tq_ck ,在 FDCAN_CKDIV 寄存器中配置分频系数。

可以认为FDCAN内核用的时钟都是fdcan_tq_ck ,只不过 fdcan_tq_ck 为1分频时候认为是fdcan_clk 。

2.3 波特率

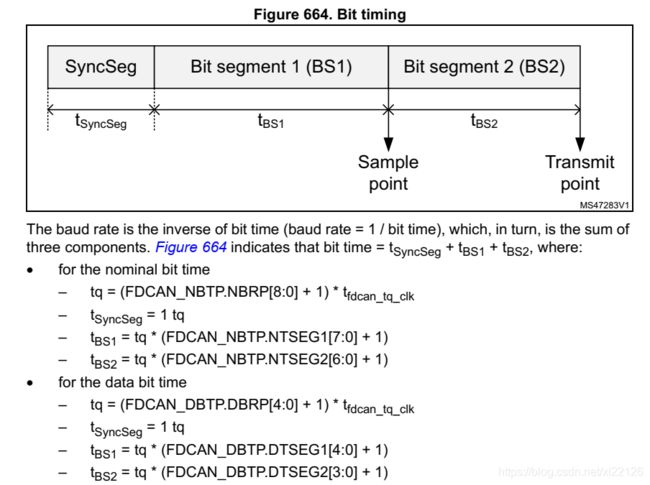

FDCAN模块的bit采样分三段:

波特率公式如下:

波特率 = 1 t q + t B S 1 + t B S 2 波特率 = \frac{1}{t_q + t_{BS1} + t_{BS2}} 波特率=tq+tBS1+tBS21

t q = ( B R P + 1 ) ∗ f d c a n _ c l k t_q = (BRP + 1)*fdcan\_clk tq=(BRP+1)∗fdcan_clk

注意:

1、由于 FDCAN 与 经典CAN 的帧格式有点差异,其数据帧波特率可变,因此在这里分出普通CAN和数据bit时间

2、数据 和 普通 bit 时间寄存器名称不一样,数据波特率寄存器 FDCAN_DBTP ,一般帧波特率寄存器为 FDCAN_NBTP 。当使用经典模式CAN时, FDCAN_DBTP 配置被忽略

3. FDCAN的地址分布

3.1 总体分布

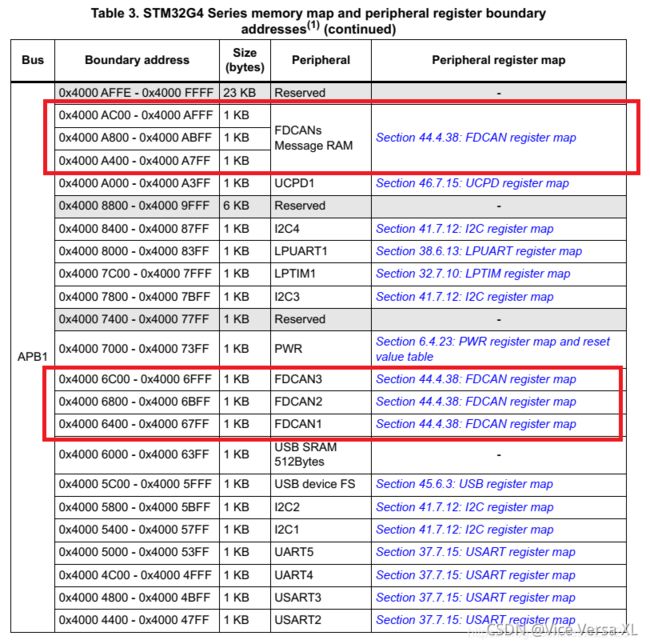

由于头文件中没有该寄存器的宏定义,因此需要自己建立宏定义。

G474的FDCAN外设一共有3组(FDCAN1,FDCAN2,FDCAN3),寄存器配置分为3个,消息RAM也分为3组。

3.2 Message RAM

1个 信息RAM 有 212 words 的大小,即 212 × 4 = 848 Bytes 。

根据3.1和3.2可以先把 消息RAM 的宏定义写好

#define FDCANs_MESSAGE_RAM_BASE 0x4000A400

#define FDCAN1_RAM_BASE (FDCANs_MESSAGE_RAM_BASE)

#define FDCAN2_RAM_BASE (FDCAN1_RAM_BASE + 0x00000350)

#define FDCAN3_RAM_BASE (FDCAN2_RAM_BASE + 0x00000350)

typedef struct

{

uint32_t FILTER_11BIT[28]; //0x4000A400 ~ 0x4000A470

uint32_t FILTER_29BIT[8][2]; //0x4000A470 ~ 0x4000A4B0

uint32_t Rx_FIFO_0[3][18]; //0x4000A4B0 ~ 0x4000A588

uint32_t Rx_FIFO_1[3][18]; //0x4000A588 ~ 0x4000A660

uint32_t Tx_FIFO[6]; //0x4000A660 ~ 0x4000A678

uint32_t Tx_BUFFER[3][18]; //0x4000A678 ~ 0x4000A750

}FDCAN_RAM_Struct;

#define FDCAN1_RAM ((FDCAN_RAM_Struct *)FDCAN1_RAM_BASE)

#define FDCAN2_RAM ((FDCAN_RAM_Struct *)FDCAN2_RAM_BASE)

#define FDCAN3_RAM ((FDCAN_RAM_Struct *)FDCAN3_RAM_BASE)

注意!!! 上面的代码第1行的宏定义部分,偏移为 0x350 而不是 0x400。

曾经我根据 3.1里面的图片进行配置(0x400也就是1KB),结果只有FDCAN1好用,FDCAN2和FDCAN3都不能使用,困扰了我一天来找这个问题,后来使用 0x350 就可以了,可能是手册写错了,也可能是我的理解与有误。

这里是个坑,希望大家能够规避一下。

4. FDCAN中断配置

4.1 中断寄存器

FDCAN中断配置中,涉及的寄存器为

- FDCAN_IE 与其他外设的IE一样,中断使能寄存器,在这里选择使用的中断,在代码中会注释

- FDCAN_ILE 中断总线使能。FDCAN中将中断分为了两个分支,即有两个中断函数

- FDCAN_ILS 中断总线选择。在这个寄存器中配置哪个中断归属于哪个中断分支,默认都为分支0.

5. FDCAN的筛选器

5.1 筛选器的特征

- 每个筛选器可配置为

• 范围筛选

• 指定ID筛选

• 屏蔽典型bit筛选- 每个过滤器元件可配置为接受或拒绝过滤

- 每个过滤器元素可以单独启用/禁用

- 过滤器是按顺序检查的,执行在第一个匹配的过滤器元素时停止

相关的寄存器:全局筛选配置(RXGFC)、拓展ID和掩码(XIDAM)

如果需要接收数据,一定要配置筛选器,否则会什么也接受不到。

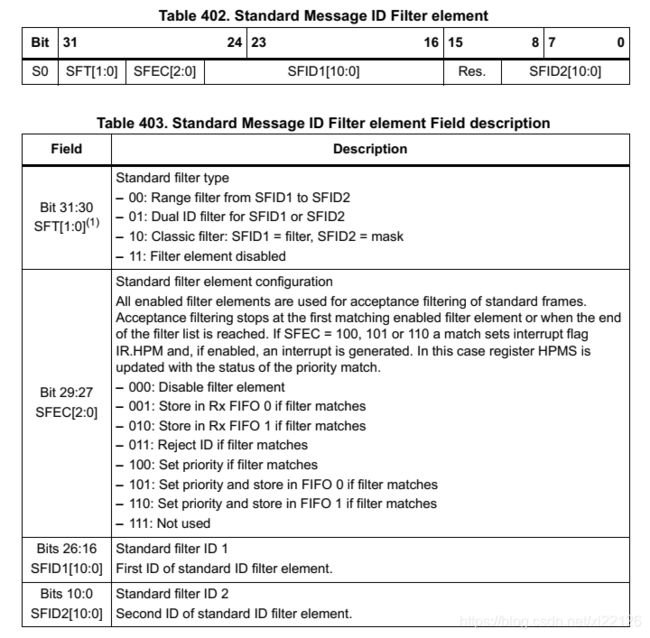

5.2 11-bit 筛选器的格式

这里根据手册的翻译进行配置就好,29-bit 的筛选器也是如此,手册里全有,我就不放图片了,太占地方。

对于筛选器的掩码模式,可通过传送门了解到:CAN通讯难点———验收筛选器

通过配置筛选器,可以使FDCAN外设接收其他模块发来的信息,在筛选器中配置接收消息的FIFO或者拒收消息。配置筛选器是FDCAN接收的关键。

筛选器的配置不受 INIT 和 CCE 标志位的限制,可随时配置。

6. FIFO模式与Queue模式

FIFO模式与队列模式的区别为:

- 队列模式的优先级遵循邮箱0优先级最高,其次是1,最后是2,如果当前3个邮箱全有数据,优先发送邮箱0的数据

- FIFO模式的优先级是遵循哪个数据先进入的邮箱,与其所在的索引地址无关,即:如果当前3个邮箱全有数据,邮箱2被最先写入,则优先发送邮箱2的数据。

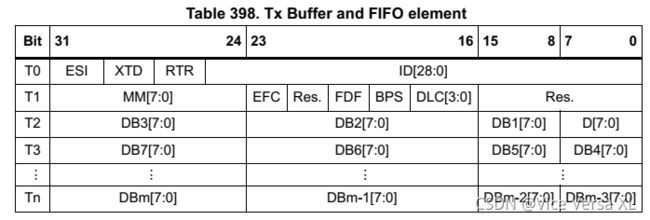

6.1 TX FIFO 的寄存器格式

具体说明见手册1969页,我就不复制了,翻一下就能懂每个BIT代表的意思。

根据上表,我们就可以写出对应各个标志位的结构体,方便后期指针使用。

由于其buffer支持 11-bit ID 和 29-bit ID

7. FDCAN的初始化

IO口配置我就不介绍了,想必大家都会配置IO。

- 首先在RCC->APB1RSTR1寄存器中使能RCC_APB1ENR1_FDCANEN,这样FDCAN的寄存器就可以配置了。

- 然后选择FDCAN内核时钟的时钟源,在RCC->CCIPR寄存器的RCC_CCIPR_FDCANSEL中配置。

- 置位INIT标志位,开始配置寄存器(只有INIT标志位置位,才可置位CCE标志位)

- 等待INIT标志位置位

- 置位CCE标志位,解锁受保护的寄存器

- 等待CCE标志位置位

- 配置时钟分频 (FDCAN_CKDIV 寄存器)

- 配置波特率

- 配置中断

- 使能筛选器

- 配置筛选器

- 清除INIT标志位

到此,FDCAN就配置完了,具体操作见代码

初始化代码见

附录1 FDCAN寄存器配置

8. 发送操作

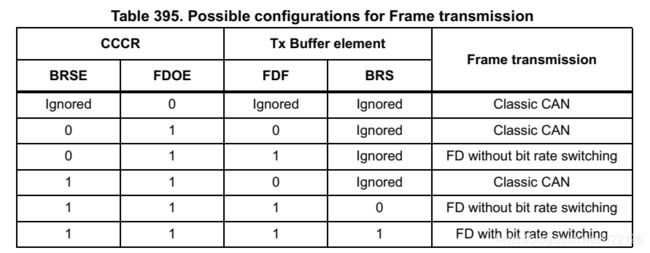

8.1 FDCAN帧模式

FDCAN帧模式由下表各个标志位配置:

根据上表所示,可以通过 CCCR寄存器 和 Tx Buffer 内部的标志位 配合,实现不同模式的CAN。

由于鄙人只想使用 经典CAN,因此将 CCCR寄存器 中的 FDOE 配置为 0,其他标志位我就不管了。

8.2 发送步骤

- 读取 FDCAN1->TXFQS 是否有可用信箱( FDCAN_TXFQS_TFQF 是否置位)

- 如果没置位邮箱满标志,则查询 FDCAN_TXFQS_TFQPI 索引,获得的索引就是可以写入的邮箱

- 将要发送的数据写入刚才读取的索引的 Tx Buffer 中(在这里可以配置发送长度、ID等信息)

- 置位发送请求

- 等待发送完成(可以不等待,配置发送完成中断使能后,在中断中置位发送完成标志来判断是否发送完毕)

示例代码见

附录2 发送函数

代码中的部分宏定义是根据手册定义的,由于太长就不放在这里了,完整代码在 代码下载

9. 接收操作

首先配置筛选器来选择接收的消息和接收后存放的FIFO。

接收分为 覆盖模式 和 阻塞模式 。

覆盖模式 顾名思义,就是当FIFO满了以后,接收到新消息后覆盖老消息。

阻塞模式 就是当FIFO满了之后,忽略新消息,保留老消息。

当 Rx FIFO 0 接收到消息后,将会在 FDCAN_RXF0S 寄存器中 F0GI 标志位指示新消息存储索引,当 CPU 读取这些消息后,务必将最后 F0GI 的值写入到 FDCAN_RXF0A 的 F0AI 标志位,来确认来读取完毕,这会将 FDCAN_RXF0S寄存器中的索引标志位 F0GI 设置为 F0AI + 1 并更新 FIFO 0 的存储计数 (FDCAN_RXF0S 寄存器中 F0FL 标志位,范围0~3),如果不确认读取完毕,将会导致指示索引 F0GI 失效。

接收操作可以在中断中进行,通过配置 FDCAN_IE 寄存器中的相应 中断使能标志位 来开启中断,具体示例见初始化代码。如:使能 FIFO0 接收新消息中断就置位 FDCAN_IE_RF0NE 标志位。

因此,接收操作的步骤为:

- 读取接收的数据

- 确认读取完毕

接收程序见

附录3 中断程序

接收中断配置见

附录1 FDCAN寄存器配置

10. 故障

故障处理这里就不介绍了,值得注意的是:

当CAN两个总线短接,超过一定时间后,FDCAN会因为不能检测到有效电平而置位故障标志,同时置位初始化 INIT 标志,导致CAN关闭,排除硬件故障后可直接复位 INIT 标志来恢复故障前的运行状态(也就是说可以正常收发数据了)。

11. 参考资料传送门

11.1 代码下载(0积分)

代码下载(0积分)

11.2 其他 CAN 知识了解

其他 CAN 知识了解

附录1. FDCAN寄存器配置

返回第7章 FDCAN的初始化

返回第9章 接收操作

/**

* @description: FDCAN1 初始化

* @param {*}

* @return {*}

* @author: XL

*/

void FDCAN1_Function_Init(void)

{

//在RCC_CCIPR寄存器中选择FDCAN时钟为HSE,即8MHz

//

FDCAN1->CCCR |= FDCAN_CCCR_INIT; //步骤3 置位INIT标志,开始配置寄存器(只有INIT标志位置位,才可置位CCE标志位)

while (!(FDCAN1->CCCR & FDCAN_CCCR_INIT)); //步骤4 等待INIT标志位置位

FDCAN1->CCCR |= FDCAN_CCCR_CCE; //步骤5 置位CCE标志位,解锁受保护的寄存器

while (!(FDCAN1->CCCR & FDCAN_CCCR_CCE)); //步骤6 等待CCE标志位置位

FDCAN_CONFIG->CKDIV = 0x0; //步骤7 配置时钟分频

//只允许在FDCAN1初始化中配置

//fdcan_clk = 168 / 1 = 168 MHz,影响到FDCAN2、3(FDCAN_CONFIG地址上来说,还是属于FDCAN1)

FDCAN1->CCCR |= 0

// |FDCAN_CCCR_NISO //bit15: 【0|ISO11898-1】【1|CANFD v1.0】

// |FDCAN_CCCR_TXP //bit14: 【1|在下上一个成功帧后暂停两个bit再起始】

// |FDCAN_CCCR_EFBI //bit13: 【1|同步检测边沿需要两个显性tq】

// |FDCAN_CCCR_PXHD //bit12: 【0|启动协议异常处理】【1|禁用协议异常处理】

// |FDCAN_CCCR_BRSE //bit09: 【1|启用波特率切换】

// |FDCAN_CCCR_FDOE //bit08: 【0|FD操作禁止】【1|FD操作使能】

// |FDCAN_CCCR_TEST //bit07: 【1|测试模式使能】

|FDCAN_CCCR_DAR //bit06: 【0|启用发送失败后自动重传】【1|禁止自动重传】

// |FDCAN_CCCR_MON //bit05: 【0|总线监控模式禁止】【1|总线监控模式使能】

// |FDCAN_CCCR_CSR //bit04: 【0|无时钟停止请求】【1|时钟停止请求,当时钟停止请求发生,先置位INIT在置位CSA在所有传输请求完成并且CAN总线空闲】

// |FDCAN_CCCR_CSA //bit03: 【0|没有时钟停止】【1|FDCAN可通过停止APB时钟和内核时钟来进行掉电】

// |FDCAN_CCCR_ASM //bit02: 【1|启用限制模式,限制模式下不会主动发送数据】

// |FDCAN_CCCR_CCE //bit01: 【1|允许配置受保护的寄存器,INIT标志位必须置位】

// |FDCAN_CCCR_INIT //bit00: 【1|初始化开始】

;

// FDCAN1->DBTP = 0 //数据帧的波特率(FDCAN模式需要配置,经典CAN不需要配置)

// |FDCAN_DBTP_TDC //bit23: 【1|收发延时补偿使能】

// |(0 << FDCAN_DBTP_DBRP_Pos) //bit[20:16]: tq = (BRP + 1)*fdcan_clk

// |(22 << FDCAN_DBTP_DTSEG1_Pos) //bit[12:08]: 一阶段采样 8000000

// |(7 << FDCAN_DBTP_DTSEG2_Pos) //bit[07:04]: 二阶段采样 波特率 = 8000000/(3+DTSEG1+DTSEG2) = 8000000/32 = 250k

// |(4 << FDCAN_DBTP_DSJW_Pos) //bit[03:00]: 同步脉宽

// ;

FDCAN1->NBTP = 0 //步骤8 配置波特率

|(4 << FDCAN_NBTP_NSJW_Pos) //bit[31:25]: 同步脉宽 必须小于SEG2

|(0 << FDCAN_NBTP_NBRP_Pos) //bit[24:16]: BRP tq = (BRP + 1)*fdcan_clk

|(22 << FDCAN_NBTP_NTSEG1_Pos) //bit[15:08]: 一阶段采样

|(7 << FDCAN_NBTP_NTSEG2_Pos) //bit[06:00]: 二阶段采样 波特率 = 8000000/(3+DTSEG1+DTSEG2) = 8000000/32 = 250k

;

//步骤9 配置中断

FDCAN1->IE |= 0

// |FDCAN_IE_ARAE //bit23: 访问保留地址使能

// |FDCAN_IE_PEDE //bit22: 数据阶段协议错误

// |FDCAN_IE_PEAE //bit21: 仲裁阶段协议错误

// |FDCAN_IE_WDIE //bit20: 看门狗使能

// |FDCAN_IE_BOE //bit19: 总线关闭使能

// |FDCAN_IE_EWE //bit18: 警告状态中断使能

// |FDCAN_IE_EPE //bit17: 错误被动中断使能

// |FDCAN_IE_ELOE //bit16: 错误记录语出中断使能

// |FDCAN_IE_TOOE //bit15: 超时中断使能

// |FDCAN_IE_MRAFE //bit14: 信息RAM访问失败中断使能

// |FDCAN_IE_TSWE //bit13: 时间戳重复中断使能

// |FDCAN_IE_TEFLE //bit12: TX事件FIFO元素丢失中断使能

// |FDCAN_IE_TEFFE //bit11: TX时间FIFO满中断使能

// |FDCAN_IE_TEFNE //bit10: TX事件FIFO新元素进入中断使能

// |FDCAN_IE_TFEE //bit09: TXFIFO空中断使能

// |FDCAN_IE_TCFE //bit08: 发送取消完成中断使能

// |FDCAN_IE_TCE //bit07: 传输完成中断使能

// |FDCAN_IE_HPME //bit06: 高优先级消息中断使能

// |FDCAN_IE_RF1LE //bit05: RXFIFO1报文丢失中断使能

// |FDCAN_IE_RF1FE //bit04: RXFIFO1消息满中断使能

|FDCAN_IE_RF1NE //bit03: RXFIFO1新消息中断使能

// |FDCAN_IE_RF0LE //bit02: RXFIFO0报文丢失中断使能

// |FDCAN_IE_RF0FE //bit01: RXFIFO0消息满中断使能

|FDCAN_IE_RF0NE //bit00: RXFIFO0新消息中断使能

;

FDCAN1->ILE = 0x00000000

|FDCAN_ILE_EINT1 //bit01: 中断总线 fdcan_intr1_it 使能

|FDCAN_ILE_EINT0 //bit00: 中断总线 fdcan_intr0_it 使能

;

FDCAN1->ILS = 0x00000000 //中断总线选择

// |FDCAN_ILS_PERR //bit06:

// ARAL: Access to reserved address line

// PEDL: Protocol error in data phase line

// PEAL: Protocol error in arbitration phase line

// WDIL: Watchdog interrupt line

// BOL: Bus_Off status

// EWL: Warning status interrupt line

// |FDCAN_ILS_BERR //bit05:

// ELOL: Error logging overflow interrupt line

// |FDCAN_ILS_MISC //bit04:

// TOOL: Timeout occurred interrupt line

// MRAFL: Message RAM access failure interrupt line

// TSWL: Timestamp wraparound interrupt line

// |FDCAN_ILS_TFERR //bit03:

// TEFLL: Tx event FIFO element lost interrupt line

// TEFFL: Tx event FIFO full interrupt line

// TEFNL: Tx event FIFO new entry interrupt line

// TFEL: Tx FIFO empty interrupt line

// |FDCAN_ILS_SMSG //bit02:

// TCFL: Transmission cancellation finished interrupt line

// TCL: Transmission completed interrupt line

// HPML: High-priority message interrupt line

|FDCAN_ILS_RXFIFO1 //bit01:当邮箱1的事件在 fdcan1_intr1_it 中断分支中处理

// RF1LL: Rx FIFO 1 message lost interrupt line

// RF1FL: Rx FIFO 1 full Interrupt line

// RF1NL: Rx FIFO 1 new message interrupt line

// |FDCAN_ILS_RXFIFO0 //bit00:当邮箱0的事件在 fdcan1_intr0_it 中断分支中处理

// RF0LL: Rx FIFO 0 message lost interrupt line

// RF0FL: Rx FIFO 0 full interrupt line

// RF0NL: Rx FIFO 0 new message interrupt line

;

//步骤9 结束

//步骤10 使能筛选器

FDCAN1->RXGFC |= 0

|(1 << FDCAN_RXGFC_LSE_Pos) //bit[27:24]: 列表信息拓展【0|无拓展消息过滤】【1|1~8拓展消息】【>8|被解释为8】

|(2 << FDCAN_RXGFC_LSS_Pos) //bit[20:16]: 【0|无标准消息ID过滤】【1~28|标准消息ID元素过滤数量】【>28|被解释为28】

// |FDCAN_RXGFC_F0OM //bit09: FIFO0模式:覆盖或者堵塞【0|阻塞模式】【1|覆盖模式】

// |FDCAN_RXGFC_F1OM //bit08: FIFO1模式:覆盖或者堵塞【0|阻塞模式】【1|覆盖模式】

|(2 << FDCAN_RXGFC_ANFS_Pos) //bit[05:04]: 定义如何处理接收到的id为11位且与筛选器列表中的任何元素不匹配的消息。【0|在FIFO0中接收】【1|在FIFO1中接收】【2~3|拒绝】

|(2 << FDCAN_RXGFC_ANFE_Pos) //bit[03:02]: 定义如何处理接收到的id为29位且与筛选器列表中的任何元素不匹配的消息。【0|在FIFO0中接收】【1|在FIFO1中接收】【2~3|拒绝】

|FDCAN_RXGFC_RRFS //bit01: 【1|拒绝所有11位ID远程标准帧】

|FDCAN_RXGFC_RRFE //bit00: 【1|拒绝所有29位ID远程标准帧】

;

// FDCAN1->XIDAM = 0x1FFFFFFF; //FDCAN 扩展 ID 和屏蔽寄存器

// FDCAN1->TXBTIE = 0

// // |0x00000004 //bit02: TxBuffer【1|发送中断使能】

// // |0x00000002 //bit01: TxBuffer【1|发送中断使能】

// |0x00000001 //bit00: TxBuffer【1|发送中断使能】

// ;

// FDCAN1->TXBCIE = 0

// // |0x00000004 //bit02: TxBuffer【1|取消中断使能】

// // |0x00000002 //bit01: TxBuffer【1|取消中断使能】

// // |0x00000001 //bit00: TxBuffer【1|取消中断使能】

// ;

//步骤11 配置筛选器

FDCAN1_RAM->FILTER_11BIT[0] = 0x00000000

|(1 << FDCANx_RAM_FILTER11_S0_SFT_Pos) //【0|范围过滤,从SFID1~SFID2】【1|单独滤波SFID1和SFID2】【2|经典滤波】【3|禁用过滤】

|(1 << FDCANx_RAM_FILTER11_S0_SFEC_Pos) //【0|禁用过滤元件】【1|匹配存储在FIFO0】【2|匹配存储在FIFO1】【3|匹配存就拒绝】【4|匹配设置优先级】【5|匹配设置优先级并存储到FIFO0中】【6|匹配设置优先级并存储到FIFO1中】【7|保留】

|(0x600 << FDCANx_RAM_FILTER11_S0_SFID1_Pos) //【SFID1】

|(0x609 << FDCANx_RAM_FILTER11_S0_SFID2_Pos) //【SFID2】

;//列表滤波,只接收 ID为0x600和0x609 的数据,并且这两个ID放入FIFO0中

FDCAN1_RAM->FILTER_11BIT[1] = 0x00000000

|(1 << FDCANx_RAM_FILTER11_S0_SFT_Pos) //【0|范围过滤,从SFID1~SFID2】【1|单独滤波SFID1和SFID2】【2|经典滤波】【3|禁用过滤】

|(2 << FDCANx_RAM_FILTER11_S0_SFEC_Pos) //【0|禁用过滤元件】【1|匹配存储在FIFO0】【2|匹配存储在FIFO1】【3|匹配存就拒绝】【4|匹配设置优先级】【5|匹配设置优先级并存储到FIFO0中】【6|匹配设置优先级并存储到FIFO1中】【7|保留】

|(0x209 << FDCANx_RAM_FILTER11_S0_SFID1_Pos) //【SFID1】

|(0x209 << FDCANx_RAM_FILTER11_S0_SFID2_Pos) //【SFID2】

;//列表滤波,只接收 ID为0x209 的数据,并且这个ID放入FIFO1中

FDCAN1_RAM->FILTER_29BIT[0][0] = 0x00000000

|(1 << FDCANx_RAM_FILTER29_F0_EFEC_Pos) //【0|禁止滤波】【1|匹配就保存FIFO1中】【2|匹配就保存FIFO2中】【3|拒绝匹配ID】【4|如果过滤器匹配,则设置优先级】【5|如果过滤器匹配,则设置优先级并存储在 FIFO 0 中】【6|如果过滤器匹配,则设置优先级并存储在 FIFO 1 中】【7|Reserve】

|(0x0CCCCCCC << FDCANx_RAM_FILTER29_F0_EFID1_Pos) //【EFID1】

;

// FDCAN1_RAM->FILTER_29BIT[0][1] = 0x00000000

// |(1 << FDCANx_RAM_FILTER29_F1_EFTI_Pos) //【0|EFID1到EFID2(EFID2>=EFID1)】【1|单独SFID1或者SFID2】【2|经典滤波】【3|EFID1到EFID2(EFID2>=EFID1),未使用XIDAM寄存器的掩码】

// |(0x00000000 << FDCANx_RAM_FILTER29_F1_EFID2_Pos) //【EFID2】

// ;

// FDCAN1_RAM->FILTER_29BIT[1][0] = 0x00000000

// |(1 << FDCANx_RAM_FILTER29_F0_EFEC_Pos) //【0|禁止滤波】【1|匹配就保存FIFO1中】【2|匹配就保存FIFO2中】【3|拒绝匹配ID】【4|如果过滤器匹配,则设置优先级】【5|如果过滤器匹配,则设置优先级并存储在 FIFO 0 中】【6|如果过滤器匹配,则设置优先级并存储在 FIFO 1 中】【7|Reserve】

// |(0x00000000 << FDCANx_RAM_FILTER29_F0_EFID1_Pos) //【EFID1】

// ;

// FDCAN1_RAM->FILTER_29BIT[1][1] = 0x00000000

// |(1 << FDCANx_RAM_FILTER29_F1_EFTI_Pos) //【0|EFID1到EFID2(EFID2>=EFID1)】【1|单独SFID1或者SFID2】【2|经典滤波】【3|EFID1到EFID2(EFID2>=EFID1),未使用XIDAM寄存器的掩码】

// |(0x00000000 << FDCANx_RAM_FILTER29_F1_EFID2_Pos) //【EFID2】

// ;

// FDCAN1_RAM->FILTER_29BIT[2][0] = 0x00000000

// |(1 << FDCANx_RAM_FILTER29_F0_EFEC_Pos) //【0|禁止滤波】【1|匹配就保存FIFO1中】【2|匹配就保存FIFO2中】【3|拒绝匹配ID】【4|如果过滤器匹配,则设置优先级】【5|如果过滤器匹配,则设置优先级并存储在 FIFO 0 中】【6|如果过滤器匹配,则设置优先级并存储在 FIFO 1 中】【7|Reserve】

// |(0x00000000 << FDCANx_RAM_FILTER29_F0_EFID1_Pos) //【EFID1】

// ;

// FDCAN1_RAM->FILTER_29BIT[2][1] = 0x00000000

// |(1 << FDCANx_RAM_FILTER29_F1_EFTI_Pos) //【0|EFID1到EFID2(EFID2>=EFID1)】【1|单独SFID1或者SFID2】【2|经典滤波】【3|EFID1到EFID2(EFID2>=EFID1),未使用XIDAM寄存器的掩码】

// |(0x00000000 << FDCANx_RAM_FILTER29_F1_EFID2_Pos) //【EFID2】

// ;

// FDCAN1_RAM->FILTER_29BIT[3][0] = 0x00000000

// |(2 << FDCANx_RAM_FILTER29_F0_EFEC_Pos) //【0|禁止滤波】【1|匹配就保存FIFO1中】【2|匹配就保存FIFO2中】【3|拒绝匹配ID】【4|如果过滤器匹配,则设置优先级】【5|如果过滤器匹配,则设置优先级并存储在 FIFO 0 中】【6|如果过滤器匹配,则设置优先级并存储在 FIFO 1 中】【7|Reserve】

// |(0x00000000 << FDCANx_RAM_FILTER29_F0_EFID1_Pos) //【EFID1】

// ;

// FDCAN1_RAM->FILTER_29BIT[3][1] = 0x00000000

// |(1 << FDCANx_RAM_FILTER29_F1_EFTI_Pos) //【0|EFID1到EFID2(EFID2>=EFID1)】【1|单独SFID1或者SFID2】【2|经典滤波】【3|EFID1到EFID2(EFID2>=EFID1),未使用XIDAM寄存器的掩码】

// |(0x00000000 << FDCANx_RAM_FILTER29_F1_EFID2_Pos) //【EFID2】

// ;

// FDCAN1_RAM->FILTER_29BIT[4][0] = 0x00000000

// |(2 << FDCANx_RAM_FILTER29_F0_EFEC_Pos) //【0|禁止滤波】【1|匹配就保存FIFO1中】【2|匹配就保存FIFO2中】【3|拒绝匹配ID】【4|如果过滤器匹配,则设置优先级】【5|如果过滤器匹配,则设置优先级并存储在 FIFO 0 中】【6|如果过滤器匹配,则设置优先级并存储在 FIFO 1 中】【7|Reserve】

// |(0x00000000 << FDCANx_RAM_FILTER29_F0_EFID1_Pos) //【EFID1】

// ;

// FDCAN1_RAM->FILTER_29BIT[4][1] = 0x00000000

// |(1 << FDCANx_RAM_FILTER29_F1_EFTI_Pos) //【0|EFID1到EFID2(EFID2>=EFID1)】【1|单独SFID1或者SFID2】【2|经典滤波】【3|EFID1到EFID2(EFID2>=EFID1),未使用XIDAM寄存器的掩码】

// |(0x00000000 << FDCANx_RAM_FILTER29_F1_EFID2_Pos) //【EFID2】

// ;

//步骤12 清除INIT标志位

FDCAN1->CCCR &= ~FDCAN_CCCR_INIT;//退出初始化模式,CCE会自动清除

while (FDCAN1->CCCR & FDCAN_CCCR_INIT);//等待退出

}

返回第7章 FDCAN的初始化

返回第9章 接收操作

附录2 发送函数

返回第8章 发送操作

/**

* @description: 发送11位地址的报文

* @param {uint8_t} FDCAN_Index FDCANx 1~3 FDCAN外设索引使用FDCAN1/2/3

* @param {uint16_t} ID 11位ID发送

* @param {uint8_t} RTR 0-数据帧 1-远程帧

* @param {uint8_t} DLC 数据长度 0~8

* @param {Buffer_72Byte_Struct} *buffer 发送数组地址

* @return {uint8_t} SUCCEED/FAILED/ERROR

* @author: XL

*/

uint8_t FDCAN_11ID_SendData(uint8_t FDCAN_Index, uint16_t ID,uint8_t RTR,uint8_t DLC,Buffer_72Byte_Struct *buffer)

{

uint8_t Free_Mailbox;//空闲邮箱索引

FDCAN_RAM_Struct* FDCAN_RAM;//FDCANx_RAM指针

FDCAN_GlobalTypeDef* FDCAN;//FDCANx指针

switch (FDCAN_Index)//根据索引确定使用FDCANx

{

case 1:

FDCAN_RAM = FDCAN1_RAM;

FDCAN = FDCAN1;

break;

case 2:

FDCAN_RAM = FDCAN2_RAM;

FDCAN = FDCAN2;

break;

case 3:

FDCAN_RAM = FDCAN3_RAM;

FDCAN = FDCAN3;

break;

default:

return ERROR;//输入索引错误,无效

break;

}

if(FDCAN->TXFQS & FDCAN_TXFQS_TFQF)

{ //CanBus判断是否有空闲的发送寄存器,然后发送,否则等待

return FAILED;//没有空闲邮箱

}

else

{ //只要第一个邮箱空闲,始终先使用第一个,然后是第二个,第三个邮箱

Free_Mailbox = ((uint8_t)(FDCAN->TXFQS >> 16)) & 0x03;//获取空闲邮箱

FDCAN_RAM->Tx_BUFFER[Free_Mailbox][0] = ((uint32_t)ID << FDCANx_RAM_TxBuffer_T0_11ID_Pos);//写入地址

FDCAN_RAM->Tx_BUFFER[Free_Mailbox][1] = (DLC << FDCANx_RAM_TxBuffer_T1_DLC_Pos);//发送长度

FDCAN_RAM->Tx_BUFFER[Free_Mailbox][2] = buffer->DataWord[0];//发送的数据

FDCAN_RAM->Tx_BUFFER[Free_Mailbox][3] = buffer->DataWord[1];//发送的数据

FDCAN->TXBAR |= (0x0001 << Free_Mailbox);//置位发送请求

return SUCCEED;//返回成功

}

}

返回第8章 发送操作

附录3 接收中断程序

返回第9章 接收操作

/**

* @description: fdcan1_intr0_it 中断分支

* @param {*}

* @return {*}

* @author: XL

*/

void FDCAN1_IT0_IRQHandler(void)

{

if(FDCAN1->IR & FDCAN_IR_RF0N)//邮箱0有新消息

{

FDCAN1->IR |= FDCAN_IR_RF0N;//清除新消息状态标志

switch((FDCAN1->RXF0S & FDCAN_RXF0S_F0GI) >> FDCAN_RXF0S_F0GI_Pos)//获取索引

{

case 0:

FDCAN1_Rxbuffer0.DataWord[0] = FDCAN1_RAM->Rx_FIFO_0[0][0];//获取数据

FDCAN1_Rxbuffer0.DataWord[1] = FDCAN1_RAM->Rx_FIFO_0[0][1];//获取数据

FDCAN1_Rxbuffer0.DataWord[2] = FDCAN1_RAM->Rx_FIFO_0[0][2];//获取数据

FDCAN1_Rxbuffer0.DataWord[3] = FDCAN1_RAM->Rx_FIFO_0[0][3];//获取数据

FDCAN1->RXF0A = 0;//确认接收完毕

break;

case 1:

FDCAN1_Rxbuffer0.DataWord[0] = FDCAN1_RAM->Rx_FIFO_0[1][0];

FDCAN1_Rxbuffer0.DataWord[1] = FDCAN1_RAM->Rx_FIFO_0[1][1];

FDCAN1_Rxbuffer0.DataWord[2] = FDCAN1_RAM->Rx_FIFO_0[1][2];

FDCAN1_Rxbuffer0.DataWord[3] = FDCAN1_RAM->Rx_FIFO_0[1][3];

FDCAN1->RXF0A = 1;

break;

case 2:

FDCAN1_Rxbuffer0.DataWord[0] = FDCAN1_RAM->Rx_FIFO_0[2][0];

FDCAN1_Rxbuffer0.DataWord[1] = FDCAN1_RAM->Rx_FIFO_0[2][1];

FDCAN1_Rxbuffer0.DataWord[2] = FDCAN1_RAM->Rx_FIFO_0[2][2];

FDCAN1_Rxbuffer0.DataWord[3] = FDCAN1_RAM->Rx_FIFO_0[2][3];

FDCAN1->RXF0A = 2;

break;

default:break;

}

}

}

/**

* @description: fdcan1_intr1_it 中断分支

* @param {*}

* @return {*}

* @author: XL

*/

void FDCAN1_IT1_IRQHandler(void)

{

if(FDCAN1->IR & FDCAN_IR_RF1N)//邮箱1有新消息

{

FDCAN1->IR |= FDCAN_IR_RF1N;//清除新消息状态标志

switch((FDCAN1->RXF1S & FDCAN_RXF1S_F1GI) >> FDCAN_RXF1S_F1GI_Pos)//获取索引

{

case 0:

FDCAN1_Rxbuffer1.DataWord[0] = FDCAN1_RAM->Rx_FIFO_1[0][0];//获取数据

FDCAN1_Rxbuffer1.DataWord[1] = FDCAN1_RAM->Rx_FIFO_1[0][1];//获取数据

FDCAN1_Rxbuffer1.DataWord[2] = FDCAN1_RAM->Rx_FIFO_1[0][2];//获取数据

FDCAN1_Rxbuffer1.DataWord[3] = FDCAN1_RAM->Rx_FIFO_1[0][3];//获取数据

FDCAN1->RXF1A = 0;//确认接收完毕

break;

case 1:

FDCAN1_Rxbuffer1.DataWord[0] = FDCAN1_RAM->Rx_FIFO_1[1][0];

FDCAN1_Rxbuffer1.DataWord[1] = FDCAN1_RAM->Rx_FIFO_1[1][1];

FDCAN1_Rxbuffer1.DataWord[2] = FDCAN1_RAM->Rx_FIFO_1[1][2];

FDCAN1_Rxbuffer1.DataWord[3] = FDCAN1_RAM->Rx_FIFO_1[1][3];

FDCAN1->RXF1A = 1;

break;

case 2:

FDCAN1_Rxbuffer1.DataWord[0] = FDCAN1_RAM->Rx_FIFO_1[2][0];

FDCAN1_Rxbuffer1.DataWord[1] = FDCAN1_RAM->Rx_FIFO_1[2][1];

FDCAN1_Rxbuffer1.DataWord[2] = FDCAN1_RAM->Rx_FIFO_1[2][2];

FDCAN1_Rxbuffer1.DataWord[3] = FDCAN1_RAM->Rx_FIFO_1[2][3];

FDCAN1->RXF1A = 2;

break;

default:break;

}

}

}

返回第9章 接收操作