【翻译】Nios design contest 2007-002

2等奖

使用FPGA实现H.264可变区块比对硬体

Institution: 清云大学电子工程系

Participants: Wenxian Qian, Songzhi Gu

Instructor: Ou Qianmin

设计简介

区块比对法常用于运动估计,是电影图像编码系统重要组成部分。用H.264大小可变区块比对法(VBS-BMA)代替区块固定大小的区块比对法(FBS-BMA)解决了视频变化不能有效处理的问题,视频压缩率进一步提高。我们的设计减少了复杂的H.264 VBS-BMA的计算与特性延迟,低功耗,高吞吐量,提供更好的编码性能。

H.264 VBS-BMA支持4X4,4X8,8X4,8X8,8X16,16X8,16X16块。当串行数据帧通过网络传输时,用户可根据当前带宽选择最恰当的块比对,从而,获得最佳传输速度和画质。但是,H.264 VBS-BMA计算比较复杂。因此,我们设计一个有效的超大规模集成(VLSI)硬件结构,其高计算吞吐量特性将复杂的计算按照H.264视频编码的要求分割,减少计算次数,提高编码性能。我们的设计使用了以下元素:

l 硬件—因为设计含有众多用于压缩的计算,我们需要一个有效系统实时处理图像。要有效处理指定大小和频率的串行图像帧,我们使用Altera的Nios II开发套件。Nios II是一个基于RISC架构的软核处理器。它在FPGA里综合成一个处理器电路(非硬核),可扩展开发。Nios II处理器可以看做是层次化的内存设置,加上执行指定计算的处理器指令。在使用Altera的开发板和FPGA开发硬件时,我们使用Quartus II软件和SOPC Builder,开发测试平台。除了用SOPC Builder添加区块比对电路外,也使用以太网嵌入式控制硬件和组件,然后将这些下载到开发板构建原型。

l 软件—我们使用Nios II 集成开发环境(IDE)写和编译测试软件,实现pc间的网络传输,移植uC/OS-II到Nios II处理器系统。

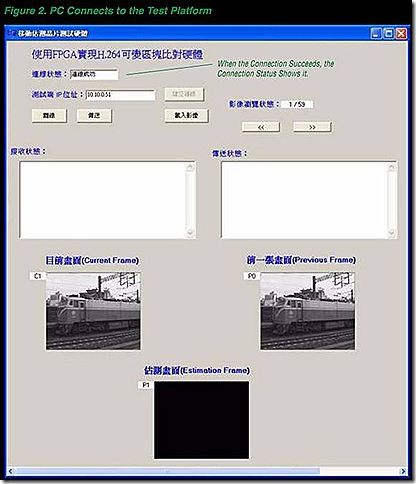

l PC—我们设计了一个可在Windows平台执行的图形界面程序。PC通过网络连接到测试平台,传送图像和变量,完成计算,估值,补偿和译码。画面实时显示在PC屏幕便于用户查看。

功能描述

如图1所示,用户通过GUI加载串行数据帧。然后,测试平台的连接状态如图2所示。当通过网络将画面传到测试平台,系统执行运动矢量计算,运动估计和运动补偿。然后,通过网络将估计画面送回PC并显示(图3)。

性能参数

本设计使用以下性能参数。

l 设计使用Cyclone EP1C20F400C7,它有20,060个逻辑单元(Les),294,912位内存,301个引脚。设计用了8,881(44%)LEs,110,352(34%)bit内存,176(58%)个引脚。

l 在Nios II处理器添加一些必要的接口模块提高系统的集成度。因为大多数外围接口和设备与经过验证的IP核相关,可加速硬件验证和软件开发。我们使用了很多Altera的IP核,包括SDRAM,Ethernet PHY chip,UART,SRAM,和flash。另外,32-bit的Nios II处理器增强了图像处理和网络,提高可用性。

l Nios II处理器作为设计控制和运算核。因为很多IP核都可以作为外围设备添加,系统更加灵活。

l 使用运动估计测试功能,测试完后,就可以实时得到估计画面。

l 当前,实现4X4区块比对。将来使用同样的概念可以添加其他区块。

设计架构

图4显示了H.264 VBS-BMA FPGA硬件架构的设计概念。用户通过GUI加载串行数据帧,通过网络发送到测试平台,测试H.264区块比对电路,通过网络接收数据,并(在测试完成后)在PC上实时显示画面。

图5显示PC操作。当前画面通过网络以TCP包的形式传送。然后PC接送测试平台发回的运动矢量并译码得到新的估值画面。

图6显示了测试平台的操作。首先,TCP接口接收PC从网络发送的帧数据并存储在接收数据缓存里。接收的第1帧作为先前帧存在先前帧内存,最后1帧作为当前帧存在当前帧内存。当接收到当前帧,当前帧和先前帧传送到区块比对电路做运动估值和运动矢量计算。DMA设备加速从内存到区块比对电路的数据传送。计算的运动矢量存在发送数据缓存并通过TCP接口送回PC。在传送到PC的过程中,使用原本的先前帧将运动矢量译码并重建为估值帧。新的估值帧放在先前帧内存替代原本的先前帧以备下次计算所用。

如图7所示,在测试平台连接到PC后,通过网络接收来自PC的帧数据(Cx)。第1帧直接送到先前帧缓存以初始化;其他所有帧送到当前帧缓存。接收到当前帧后,当前帧和先前帧发送到运动估值设备做运动矢量计算。在测试平台做关于运动矢量和先前帧的运动补偿之后,产生的估值帧(Px)作为下一个运动估值发送到先前帧缓存。同时,通过网络送回运动矢量。Px和Px-1(先前帧)存在PC里。然后,系统判断数据传送是否结束;如果没有,继续传送Cx并重复整个操作直至完成。

图8是测试平台的硬件结构。Nios II处理器创建比对电路的硬件结构。使用Avalon总线连接外围设备;比如,显示测试平台的IP地址的LCD,以太网MAC/PHY发送和接收数据包,存储先前和当前帧的SDRAM。外围设备和内存之间用DMA模块传送数据。

图9是测试平台的软件结构。它提供从内到外的支持。最内层是比对电路的硬件结构,是整个软件架构实现的基础。第2层是硬件驱动,第3层是Altera硬件抽象层(HAL)库,使得外层组件可以使用硬件。其他2层是嵌入式操作系统和堆栈协议。最后是应用程序。

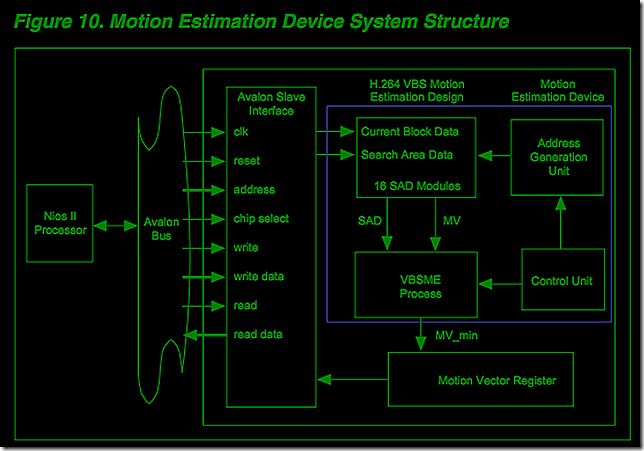

图10是运动估值设备的系统结构。Avalon总线发送帧到比对电路。经过计算,Avalon总线从运动矢量寄存器读取运动矢量并发送到PC。

运动估值架构包含16个绝对差和(SAD)模块,一个VBSME处理器,一个地址生成单元(AGU),一个控制单元。这些模块操作如下:

l 每个SAD模块处理基于子块和搜寻范围的SAD计算。

l VBSME处理器将16个SAD模块生成的SAD计算结果求和。

l AGU控制内存的读、写。

l 控制单元控制和其他模块的协调。

设计方法

图11是硬件和软件的设计流程图。

硬件设计

如图11所示,我们使用基于Nios II范例的标准项目,用硬件概念名称编写硬件程序。经过编译之后,打开SOPC Builder,集成用户自定义的IP,添加一个DMA设备增强系统性能。构建完硬件架构,SOPC Builder自动组织硬件设备并生成相关的驱动和软件开发所需的文件。用Quartus II将编译的测试平台下载到开发板,使用FPGA和其他硬件构成测试平台的快速原型。

然后,使用Nios II IDE测试软件代码并在测试平台编译测试软件。Nios II IDE包含uC/OS-II(一个实时OS)和协议栈(light-weight IP),和一个用于嵌入式系统的TCP/IP协议,有助于在TCP 服务接口和PC之间实现网络通信。uC/OS-II提供快速响应,我们将其移植到Nios II处理器。

软件设计

软件设计部分,我们修改了Altera提供的简单IP服务结口。设置IP地址,子网掩码和端口名,修改读,接收,写,和传送程序,设置系统库的发送和接收缓存的大小,并下载编译的项目到测试平台。

要让用户测试平台,我们使用Borland C++ Builder 6.0写了在Windows下运行的图形界面程序。因为使用TCP/IP,在测试平台里使用客户端的TCP接口连接PC。然后,可以传送运动帧和矢量,加载串行数据帧以测试区块比对电路,将测试平台生成德估值图像送回PC并实时显示。

设计特点

本设计有以下特点:

l H.264 区块比对电路使用Altera的DMA设备管理区块比对电路和SDRAM之间的传送,比如,不用Nios II处理器提供有效的传送。

l 使用SOPC Builder添加以太网控制硬件并自动生成相应的驱动。

l SOPC Builder里集成的用户自定义IP实现复杂的运算。另外,模块化的硬件设计减少复杂度并允许用户自定义设计。

总结

早期的软件,设计者通常花大量的精力去学习和开发软件,但是,我们的设计表明用于软件的H.264 VBS-BMA算法也可用硬件是想,并具有更好的性能。另外,Altera的简单IP服务接口使用户可以实时观察估值帧而不需要使用逻辑分析仪和信号发生器加上书写复杂的测试台处理复杂的引脚。

Nios II处理器允许用户创建多重设备—比如SDRAM,以太网PHY,UART,SRAM,flash—和在处理器里嵌入它们。用户可用SOPC Builder直接开发这些模块,减少外围设备设计的复杂度和开发周期。

在竞赛设计时为了进一步了解Nios II处理器,我们学会如何解决问题和平心静气,这些都是在课堂上学不到的宝贵财产。

Reference

H.264 VBS-BMA-Based Hardware Infrastructure Implementation on an FPGA