FPGA/数字IC求职笔试面试(1)之IIC协议详解

FPGA/数字IC求职笔试面试(1)之IIC协议详解

文章目录

- FPGA/数字IC求职笔试面试(1)之IIC协议详解

- 前言

- 一、概述:

- 二、具体协议

-

- 1.先来大致猜测

- 2.IIC协议时序

- 三、协议实现步骤(以读写EEPROM为例)

-

- 1.单字节写时序

-

- 1.单字节地址单字节数据写入

- 2.两字节地址单字节数据写入

- 2.单字节读时序

-

- 1.字节地址段器件单字节数据读操作时序

- 2字节地址段器件单字节数据读操作时序

- 四、扩展

前言

从今天起,就要正式入驻CSDN,更新关于FPGA/数字IC的求职相关知识,今天讲解的内容是IIC协议。

本文首发于微信公众号“FPGA学习者”,更多精彩内容敬请关注。

一、概述:

IIC(Inter-Intergrated Circuit),有时候写作“I2C”(注意:此处2为上标),中文一般读作“I方C”。

IIC总线由两根线组成,①SCL(Serial Clock),②SDA(Serial Data Line);且两根线均为双向线,不过多数情况下,将SCL使用为单向线。IIC总线是一种串行扩展技术,最早由Philips公司推出,广泛应用于电视,录像机和音频设备。

SCL可以理解为时钟信号线,可以说任何一个通信协议都离不开时钟驱动;

SDA为双向的数据线,既可以从A端发送数据到B端,也可以从B端发送数据到A端,但是由于只有一根线,则很明显,IIC通信方式是一种半双工通信。

虽然,IIC总线总共只有两根,但是却是一种1对多的通信方式,IIC总线上可以挂载很多的具有IIC接口的芯片。有多多呢?反正就是很多!

IIC总线数据传输速率在标准模式下可达100kbit/s,快速模式下可达 400kbit/s,高速模式下可达3.4Mbit/s。一般情况下,最多使用到400kbit/s。IIC总线上的主设备与从设备之间以字节(8 位)为单位进行双向的数据传输。

二、具体协议

1.先来大致猜测

既然IIC总线只有两根线,却又具有强大的功能,那通信协议一定不简单,那我们来继续看一看:

下图所示的是一个IIC总线的使用模型,分为主设备和从设备;

上图中,蓝色的为主设备,黄色的均为从设备,SCL和SDA两根线均接上拉电阻;上面说了,从设备可以有很多,那该怎么区分这些从设备呢?每个设备都有自己的ID,即器件地址,所以主控制器就是通过不同的地址来选择相应的设备做出不同的动作;

除此之外,协议什么时候开始呢?所以需要一个起始信号;同理,也需要一个结束信号;

比如,我现在想对从设备中的EEPROM进行数据的写入和读取操作,那么协议不仅要能找的出EEPROM这个器件,还要能告知往EEPROM中的哪个地址去写入或者读取数据;

好了,我们对协议的大致猜测到此结束,接下来正式看看,协议是怎么操作的吧。

2.IIC协议时序

| IIC协议状态 | SCL与SDA电平变化 |

|---|---|

| 总线空闲状态 | SCL为高电平,SDA为高电平; |

| IIC协议起始位 | SCL为高电平,SDA出现下降沿; |

| IIC协议结束位 | SCL为高电平,SDA出现上升沿; |

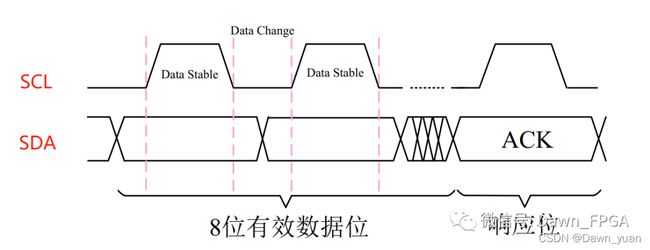

| IIC读写数据状态 | 具体见下图 |

|

|

| 上图所示为IIC协议读写数据状态时序图,可以看到,当SCL(时钟信号)为高电平时,SDA(数据信号必须保证在稳定状态),而SCL为低电平时,SDA可以发生变化; |

若在主机向从机发送数据过程中,处于8为数据有效位状态时,SDA的方向为主机→从机;处于响应位状态时,SDA的方向为从机→主机;所以,此时ACK为从机向主机的应答信号。

若在主机向从机读取数据(也就是,从机向主机发送数据)时,上图中SDA的方向均与上一个状态相反。

值得注意的是,有效应答信号规定为低电平,应答信号为高电平时,规定为非应答位(NACK)。NACK情况下表明接收数据的一方并没有正确的接收数据。

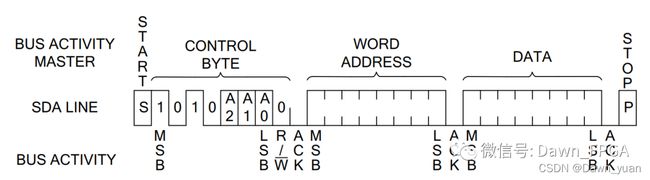

如上图,在起始位之后,应答位之前的8bit数据为控制信号,其中7位为实际有效的器件地址信号(为了编程方便,常当做8位去编写),最后一位决定着是写数据,还是读数据。当最后一位为0时,表明接下来的操作为写入数据;当最后一位为1时表明接下来的操作为读出数据。

三、协议实现步骤(以读写EEPROM为例)

1.单字节写时序

因为不同的存储器件,容量大小不同,所以有不同的数据可以写入的地址位(有的一个字节,有的两个字节),所以写入单个字节的时序也略有不同:

1.单字节地址单字节数据写入

2.两字节地址单字节数据写入

步骤如下:

1️⃣主机设置SDA为输出,并且产生起始位信号;

2️⃣主机传输器件地址信号,其中最低位为0,表明当前为写入操作;

3️⃣主机设置SDA为三态门输入,读取从机应答信号;

4️⃣读取应答信号成功后,主机设置SDA为输出,传输地址数据信号;

<此处传输的地址为数据即将写入存储器中的某个位置的地址,根据存储器内存容量大小不同,有的地址8bit即可完全表示,有的则需16bit>

5️⃣主机设置SDA为三态门输入,读取从机应答信号;

6️⃣读取应答信号成功后,主机设置SDA为输出,传输待写入的数据信号。

7️⃣主机设置SDA为三态门输入,读取从机应答信号。

8️⃣读取应答信号成功后,主机产生STOP位信号,终止数据传输。

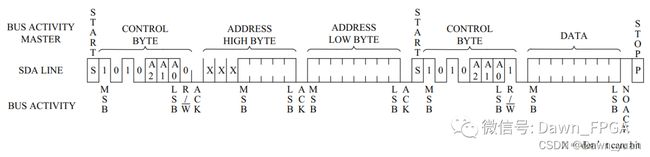

2.单字节读时序

根据地址字节数的多少,单字节读取数据的时序也略有不同,其时序图如下图所示:

1.字节地址段器件单字节数据读操作时序

2字节地址段器件单字节数据读操作时序

步骤如下:

1️⃣主机设置SDA为输出,并且主机发送起始信号;

2️⃣主机传输器件地址的字节,其中最低位为0,表明为写操作。(没错,就是写操作)。

3️⃣主机设置SDA为三态门输入,读取从机的应答信号;

4️⃣读取应答信号成功后,主机设置SDA为输出,传输地址数据信号;

<此处传输的地址为数据即将写入存储器中的某个位置的地址,根据存储器内存容量大小不同,有的地址8bit即可完全表示,有的则需16bit>

5️⃣主机设置SDA为三态门输入,读取从机应答信号;

<以上步骤和写入数据时基本相同,接下来发生变化>

6️⃣主机再次发起起始信号;并且设置SDA为输出。

7️⃣主机传输器件地址字节,其中最低位为1!表明接下来为读操作。

8️⃣将SDA设置为三态门输入,读取从机的应答信号;

9️⃣读取应答信号成功后,主机设置SDA为三态门输入,读取SDA总线上的一个字节的数据。

1️⃣0️⃣主机产生无应答信号(高电平)(无需设置为输出高电平,因为总线会被自动拉高)。

1️⃣1️⃣主机产生STOP停止位,终止传输。

总结一下读数据操作就是先要写入器件地址、写入需要读数据的地址、然后重新起始传输,写入器件地址并且此时设置为读状态,那么接下来SDA上输入的信号即为读出的EEPROM中特定地址上的数据信号。

四、扩展

EEPROM是什么呢?

EEPROM是一种掉电后数据不丢失的存储器,常常用来存储一些配置信息,用于上电后的自动数据获取;其使用IIC通信协议与主控制器之间进行数据交互。

常见EEPROM芯片有AT24CXX系列,其命名规则以及存储空间大小的关系如下:

型号 存储大小

AT24C01 1Kb

AT24C02 2Kb

AT24C04 4Kb

AT24C08 8Kb

AT24C16 16Kb

下面不写应该也能猜到其余AT24C系列的EEPROM 器件的内存大小了。

【注:参考内容:小梅哥FPGA等各大网络平台文章,在此一并表示感谢】

关注公众号:FPGA学习者,获取更多精彩内容。