ADRV9002 datasheet 笔记

ADRV9002支持的信号带宽为12K Hz到40M Hz。1M以下的信号,被认为是窄带信号;否则,被认为是宽带信号。

ADRV9002的单个接收通道有两个ADC可选,一个是高性能Σ-△ ADC和低功耗ADC。

ADRV9002支持低IF模式;通过一种下变频机制,可以接收偏离载频的信号。跟在模拟接收路径后面的一个数字NCO和混频器可以将这个中频信号转换到基带上。DownConverting这个中频信道到基带信号,可以降低数据总线上的采样率。ADRV9002对高边带或低边带的注入不做任何假设。

运行理论

RF PLL

在AD9361中,接收路径上有一个专用的PLL,发射路径上也有一个专用的PLL。与AD9361不同,ADRV9002中的两个RF PLL可以给接收支路提供源,也可以给发射路径提供源,也可以给两条路径都提供源,也可以不给任何一条路景提供源。

ADRV9002支持多种格式的快速跳频(FFH: fast frequency hopping)。不同个格式之间,频率驻留时间和转换时间是主要的区别。随着频率转换时间的减少,RF PLL相位噪声和QEC、LOL算法的性能会变差。FFH模式支持的跳动频率,是上电时预先加载或用户通过流配置到ADRV9002上的。FFH模式下的频率间的跳动,可以通过翻转一个GPIO管脚的电平或者执行一条API命令,来触发。

基带PLL

ADRv9002包含一个基带PLL合成器,可以用来生成所有的基带和数据相关时钟。有两个选项可选,一个是高性能基带PLL,一个是低功耗基带PLL。高性能基带PLL产生的时钟,可以支持更大范围的采样率。低功耗基带PLL,支持的采样率优先,但是工号更低。高性能PLL、低功耗PLL,都是基于系统的数据速率和采样率需求而自动编程的。

SPI

ADRV9002采用SPI来与基带处理器(译者注释:如FPGA)通信。这个接口可以配置为4线(收发各自用专用的端口),或者3线(数据线是双向的)。通过使用一个简单的地址数据串行总线协议,这条总线允许基带处理器设置所有的器件(译者注释:ADRV9002)控制参数。

写命令(译者注释:W命令)遵循24bit格式。第1个bit设置了总线传输的方向;接下来的15个bits设置数据的地址;最后的8bits包含了传输到特定地址上的数据。读命令(译者注释:R命令)遵循类似的格式;不同的是,前16bits是在SPI_DIO线上(译者注释:即从基带处理器到ADRV9002),最后的8bits是从ADRV9002到基带处理器(4线制下是在SPI_DO上;3线制下是在SPI_DIO上)。

应用信息

供电顺序

ADRV9002需要一个特定的上电顺序,来避免不需要的上电电流。最优的供电顺序需要VDD_1P0先上电。VDDA_1P3和VDDA_1P8在VDD_1P0上电后必须立即上电。如果使用了VDDA_1P0,则VDD_1P0必须在VDDA_1P3和VDDA_1P8上电后上电。

数据接口

ADRV9002数据接口支持CMOS和LVDS两种电气接口。CSSI(CMOS Synchronous Serial Interface)用于窄带信号;LSSI(LVDS Synchronous Serial Interface)支持ADRV9002的全部RF带宽。表20提供了顶层概述;如果想要更多的信息,需要参阅ADRV9001系统开发用户手册。

所有的信号通道支持两种电气接口,但是不支持两种接口同时运行。此外,每个收发通道有一组专用的lanes(通道)来传输信息。收发通道不能被重新配置成不同于(原始)设计(本来就)被赋予的另一组ball配置。

CSSI

CSSI支持两种运行模式,1-lane串行数据或者4-lane数据。无论哪种模式,CMOS配置下的最大时钟频率都是80MHz。

对于1-lane数据模式下的CSSI,16bit的I数据和16bit的Q数据(总共32bit)在一个lane上被串行化。图363展示了1-lane数据模式下CSSI。

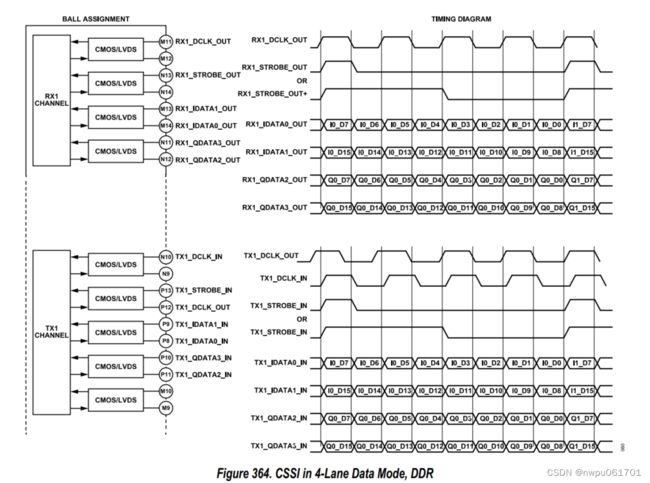

对于4-lane数据模式下的CSSI,I和Q路数据分布于4个数据lane。16bit的I和Q数据被分成8bit一组,分布于4个lane。例如,lane 0包含I数据的低八位,lane 1包含I数据的高8位,lane 2包含Q数据的低八位,lane 3包含Q数据的高八位。

4-lane数据模式的CSSI即支持全速率时钟,也支持双速率时钟(DDR clock)。DDR时钟模式允许数据在上升沿和下降沿被锁存;这允许RF的可用带宽加倍,如图364所示。

CSSI接收器

在CMOS接收配置下,除1-lane模式下的CSSI和4-lane模式下的CSSI所需要的数据通道,还需要两个信号lane,用于strobe(数据同步)信号和时钟信号。因此,1-lane模式下的CSSI需要3个信号lane,而4-lane模式下的CSSI需要6个信号lane。

RXx_DCLK_OUT是时钟输出,用于同步数据和strobe输出信号。RXx_DCLK_OUT是strobe信号,用于指示串行数据流的第一个bit。RXx_DCLK_OUT可以配配置成指示I或Q数据的起始位置。对于16bit数据,RXx_DCLK_OUT在一个时钟是高,其余31个时钟是低。或者,RXx_DCLK_OUT信号可以被配置成I数据期间为高,Q数据期间为低。在这种情况下,对于16bit数据,RXx_DCLK_OUT在16个时钟周期(I数据)上是高,在16个数据周期(Q数据)为低。

CSSI发射器

对于CMOS配置的发射器,除1-lane数据模式和4-lane数据模式所需要的data lane之外,还需要三个信号lane,用于strobe、时钟输入和时钟输出。因此,对于1-lane模式的CSSI需要4个信号lane,而4-lane模式下的CSSI需要7个信号lane。

TXx_DCLK_IN是ADRV9002的输入,用于同步数据(TXx_DATA_IN)和strobe(TXx_STROBE_IN)。TXx_STROBE_IN是输入信号,用于描述串行数据的第1个bit。类似接收路径,发射strobe也有两种配置。TXx_DCLK_OUT是ADRV9002的输出时钟,用于给外部的基带设备来产生TXx_DCLK_IN、TXx_STROBE_IN和TXx_DATA_IN。

LSSI

LSSI支持更高的RF带宽,需要使用差分对。在LSSI模式下,有两种数据传输格式,一种是1-lane数据模式,I和Q路数据在一个差分对上被串行化;另一种是2-lane数据模式,I路和Q路数据占用不同的差分对。1-lane模式或者2-lane模式的选择,依赖于RF通道带宽。为了获取ADRV9002最大的40MHz RF带宽,选择2-lane的LSSI模式。在两种模式下,LSSI所支持的最大时钟是491.52MHz,而且时钟类型是DDR。更多信息,请看图365。