【51单片机快速入门指南】2.5:并行I/O扩展与8255A

目录

- 硬知识

-

- 单片机I/O扩展基础知识

-

- I/O接口电路的功能

-

- 速度协调

- 输出数据锁存

- 数据总线隔离

- 数据转换

- 增强驱动能力

- 单片机并行扩展总线

-

- 并行扩展总线的组成

- 80C51单片机并行扩展总线

- I/O编址技术

- 可编程并行接口芯片8255

-

- 8255硬件逻辑结构

-

- 口电路

- 总线接口电路

- A组和B组控制电路

- 中断控制电路

- 8255工作方式

-

- 方式0(基本输入/输出方式)

- 方式1(选通输入/输出方式)

- 方式2(双向数据传送方式)

- 8255的编程内容

-

- 工作方式命令

- C口位置位/复位命令

- 8255A端口地址的确定

- 上手编程

-

- 仿真原理图

- 确定相关地址

- 测试源码

-

- 8255A.c

- 8255A.h

- main.c

- 仿真效果

Windows 10 20H2

Proteus 8 Frofessional v8.9 SP2

Keil uVision V5.29.0.0

PK51 Prof.Developers Kit Version:9.60.0.0

硬知识

摘自《单片机基础》(第3版) —— 李广弟 朱月秀 冷祖祁编著

单片机I/O扩展基础知识

使用单片机本身的I/O (Input/Output)口,可以实现一些简单的数据输入/输出传送,例如,开关状态的输入,发光二极管的驱动输出等。但是对于复杂的I/O操作,必须有接口电路的协调与控制才能进行。所以I/O扩展的主要内容是接口问题。

I/O接口电路的功能

在单片机系统中,主要有两类数据传送操作,一类是单片机和存储器之间的数据读/写操作,另一类是单片机和外部设备之间的数据传送操作。由于存储器与单片机具有相同的电路和信号形式,能相互兼容直接使用,因此,存储器与单片机之间采用同步定时工作方式,它们之间只要在时序关系上能相互满足就可以正常工作。所以存储器与单片机之间的信号可直接连接,不存在接口的问题。

而外部设备的速度十分复杂,必须通过I/O接口电路实现。面对复杂的接口要求,接口电路应具有如下基本功能。

速度协调

外部设备之间的速度差异很大,对于慢速设备,例如,开关、继电器和机械传感器等,每秒产生不了一个数据;而对于高速采样设备,每秒要传送成千上万个数据位。面对各种设备的速度差异,单片机无法按固定的时序以同步方式进行I/O操作,只能以异步方式进行,也就是只有在确认设备已为数据传送做好准备的前提下才能进行I/O操作。为此需要接口电路产生状态信号或中断请求信号,表明设备是否做好准备。即通过接口电路来进行单片机与外部设备之间的速度协调。

输出数据锁存

由于CPU的速度快,数据信号在总线上维持的时间十分短暂,以至于输出设备还来不及接收,数据信号就消失了。为此,需要有接口电路把输出数据先锁存起来,待输出设备为接收数据做好准备后,再把数据传送给它。这就是接口电路的数据锁存功能。

数据总线隔离

数据总线上可能连接着多个数据源(输入设备)和多个数据负载(输出设备)。但在任一时刻,总线上只能进行一个源和一个负载之间的数据传送,当一对源和负载的数据传送正在进行时,所有其他不参与的设备在电性能上必须与总线隔开。如何使这些设备在需要时与数据总线接通,而在不需要时又能及时断开,这就是接口电路的总线隔离功能。

为了实现总线隔离,需要有接口电路提供具有三态缓冲功能的三态缓冲电路。所谓三态,是指低电平状态、高电平状态和高阻抗状态。实际上三态缓冲电路是具有三态输出的门电路,所以也称三态门(TSL),当其输出为高或低电平时,是对数据总线的驱动方式;当其输出为高阻抗时,是对总线的隔离方式(也称浮动状态)。这时,缓冲器对数据总线不产生影响,犹如缓冲器与总线隔开一样。驱动方式和隔离方式是可控的,有专门的控制信号控制缓冲器的输出是驱动方式还是隔离方式。

数据转换

外部设备种类繁多,不同设备之间的性能差异很大,信号形式也多种多样。例如,既有电压信号,也有电流信号;既有数字信号,还有模拟信号等。而单片机只能使用数字信号,如果外部设备所提供或需要的不是电压形式的数字信号,就需要有接口电路进行转换,其中包括模/数转换和数/模转换等。

增强驱动能力

通过接口电路为输出数据提供足够的驱动功率,以保证外部设备能正常、平稳地工作。

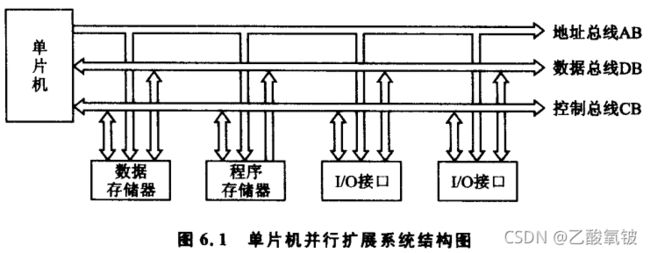

单片机并行扩展总线

单片机系统扩展是以单片机芯片为核心进行的,存储器扩展中包括程序存储器和数据存储器,其余所有扩展内容统称为I/O)扩展。单片机并行扩展系统结构如图6.1所示。

由扩展系统结构图可知,扩展是通过系统总线进行的。所谓总线就是连接单片机各扩展部件的一组公共信号线,是系统共享的通路,通过总线把各扩展部件连接起来,以进行数据、地址和控制信号的传送。

并行扩展总线的组成

并行扩展总线包括3个组成部分,即地址总线、数据总线和控制总线。

地址总线

在地址总线(Address Bus,简写AB)上传送的是地址信号,用于外扩展存储单元和I/O端口的寻址。地址总线是单向的,因为地址信号只能从单片机向外传送。

一条地址线提供一位地址,所以地址线数目决定可寻址存储单元的数目。例如,n位地址,可以产生2"个连续地址编码,可访问 2 n 2^n 2n个存储单元,即寻址范围为 2 n 2^n 2n地址单元。80C51单片机外扩展空间为64 KB,即 2 16 2^{16} 216个地址单元,因此,地址总线有16位。

数据总线

数据总线(Data Bus,简写DB)用于传送数据、状态、指令和命令。数据总线的位数应与单片机字长一致。例如,80C51单片机是8位字长,所以数据总线的位数也是8位。数据总线是双向的,即可以进行两个方向(读/写)的数据传送。

控制总线

控制总线(Control Bus,简写CB)是一组控制信号线,其中既有单片机发出的,也有外扩展部件发出的。虽然一个控制信号的传送是单向的,但是由不同方向信号组合的控制总线则应表示为双向。

80C51单片机并行扩展总线

虽然系统扩展需要地址总线和数据总线,但在单片机芯片上并没有为此提供专用的地址引脚和数据引脚,实际扩展时都是用I/O口线来充当地址线和数据线。

80C51单片机并行扩展总线的构成如图6.2所示。

以P0口的8位口线充当低位地址线/数据线

低位地址线是指低8位地址A7 ~ A0。而数据线为D7 ~ D0。由于P0口一线两用,既传送地址又传送数据,所以要采用分时技术对它上面的地址和数据进行分离。

使用分时技术被分离出的是低8位地址。因为CPU对扩展系统的操作总是先送出地址,然后再进行数据读/写操作,所以应把首先出现的地址分离出来,以便腾出总线供其后的数据传送使用。为保存分离出的地址,需另外增加一个8位锁存器,并以ALE作为锁存控制信号。因为从时序上看,在CPU送出地址时,ALE信号正好有效。为了与ALE信号相适应,应选择高电平或下降沿选通的锁存器,例如74LS373等。

低8位地址进入锁存器,经另一途径提供给扩展系统。在其后的时间里,P0口线即作为数据线使用,进行数据传送。其实在P0口的电路逻辑中已考虑了这种需要,其中的多路转接电路MUX以及地址/数据控制就是为此而设计的。

以P2口的口线作高位地址线

P2口只作为高位地址线使用。如果使用P2口全部8位口线,再加上P0口提供的低8位地址,就形成了完整的16位地址总线。使单片机外扩展的寻址范围达到64K单元。在实际应用中,高位地址线是根据需要从P2口中引出,需要用几位就引出几条口线。极端情况下,若外扩展容量小于256个单元,则不需要高位地址线。

控制信号

除地址线和数据线外,系统扩展时还需要单片机提供一些控制信号线,这就是扩展系统的控制总线。这些控制信号包括:

I/O编址技术

为了对I/O接口电路中的寄存器(端口)进行读/写操作,就需要对它们进行编址,所以就出现了I/O编址问题。有两种I/O编址方式:统一编址方式和独立编址方式。

在80C51单片机系统中,采用统一编址方式。所谓统一编址方式,就是把I/O接口中的寄存器与外扩展的数据存储器中的存储单元同等对待,合在一起使用同一个 64 KB的外扩展地址空间。I/O和存储器的统一编址,使得I/O口也得采用16位地址编址,并使用数据存储器读/写指令进行I/O操作,而不需要专门的I/O指令,这不但方便而且也增强了I/O操作的功能。所以现在大部分单片机都采用统一编址方式。

可编程并行接口芯片8255

8255硬件逻辑结构

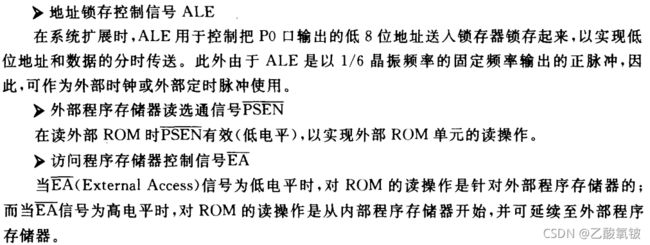

8255的全称是“可编程并行输入/输出接口芯片”,是一个40引脚的双列直插式集成电路芯片,其引脚排列如图7.1所示。

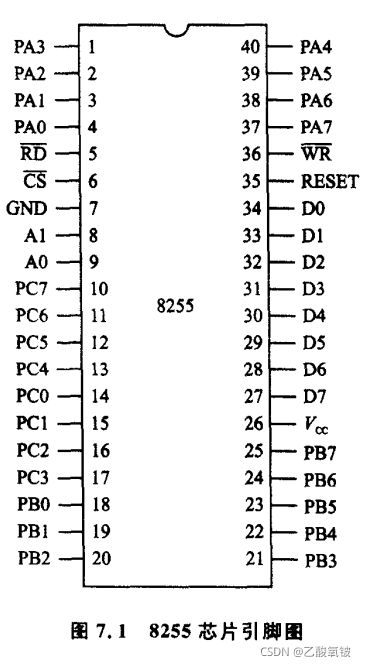

按功能可把8255的内部结构分为3个逻辑电路部分,分别为:口电路、总线接口电路和控制逻辑电路。如图7.2所示。

口电路

8255共有3个8位口,其中A口和B口是单纯的数据口,供数据输入/输出使用。而C口则既可以作数据口使用,又可以作控制口使用,主要用于实现A口和B口的控制功能。因此,在使用中常把C口分为两部分,即C口高位部分(PC7 ~ PC4)和C口低位部分(PC3 ~ PCO)。

数据传送中A口所需的控制信号由C口高位部分提供,因此,把A口和C口高位部分合在一起称为A组;同理,把B口和C口低位部分合在一起称为B组。

总线接口电路

总线接口电路用于实现8255和单片机芯片的信号连接。其中包括:

①数据总线缓冲器。数据总线缓冲器为8位双向三态缓冲器,可直接与系统数据总线相连,与I/O操作有关的数据、控制字和状态信息都是通过该缓冲器进行传送的。

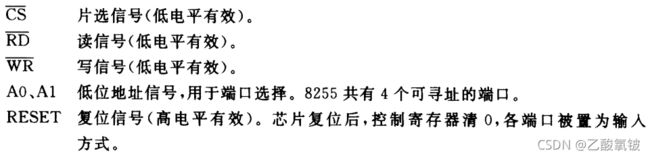

②读/写控制逻辑。读/写控制逻辑用于实现8255的硬件管理,其内容包括:芯片的选择,口的寻址以及规定各端口和单片机之间的数据传送方向等。相关的控制信号有:

A组和B组控制电路

A组控制和B组控制合在一起构成8255的控制电路,其中包括一个8位控制寄存器,用于存放编程命令和实现各口操作控制。

中断控制电路

8255逻辑电路中还包含一个中断控制电路(在图中没有画出),中断控制电路中对应A、B两个口各有一个中断触发器,即触发器A和触发器B,用于对中断的允许和禁止进行控制。置位为允许,复位为禁止。对两个触发器的置位和复位控制是通过口C的有关位进行的,具体划分是:在输入方式下,PC4对应触发器A,PC2对应触发器B;在输出方式下,PC6对应触发器A,PC2对应触发器B。

8255工作方式

8255共有3种工作方式:方式0、方式1及方式2。

方式0(基本输入/输出方式)

方式0适用于无条件数据传送,因为没有条件限制,所以数据传送可随时进行。两个8位口(A口和B口)和两个4位口(C口高位部分和C口低位部分)都可以分别或同时设置为方式0。

在方式0下,4个口可以有16种输入/输出组合,分别为:"A输人B输入C高位输入C低位输入”、“A输入B输入C高位输入C低位输出”…"A输入B输出C高位输出C低位输出”、“A输出B输出C高位输出C低位输出”等。

方式1(选通输入/输出方式)

方式1是选通输入/输出方式。8255的“选通”是通过信号的“问”与“答”,以联络方式(或称握手方式)实现的。所以这种数据传送方式是有条件的,适用于以查询或中断方式进行控制。

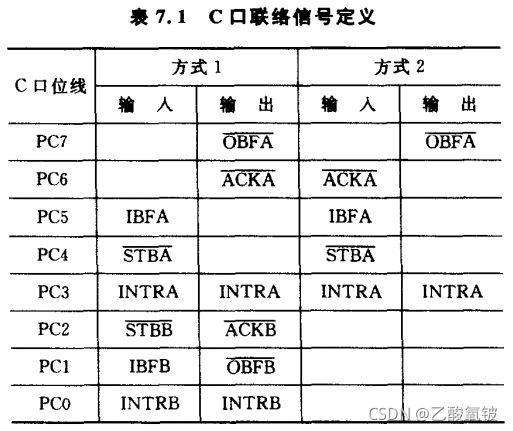

在方式1下,A口和B口是数据口,C口是控制口,用于传送和保存数据口所需要的联络信号。这些联络信号如表7.1所列。

在该方式下,A口和B0的联络信号都是3个。在具体应用中,如果只有一个口按方式1使用,需占用11位( 8 + 3 = 11 8+3=11 8+3=11)口线,剩下的13位口线可按其他方式使用;如果两个口都按方式1使用,则只剩下2位口线可作它用。

方式2(双向数据传送方式)

方式2是在方式1的基础上加上双向传送功能,但只有A口才能选择这种工作方式,这时A口既能输入数据又能输出数据。如果把A口置于方式2下,则B口只能工作于方式0。方式2适用于查询或中断方式的双向数据传送。在这种方式下需使用C口的5位口线作控制线。

8255的编程内容

8255是可编程接口芯片,主要编程内容是两条控制命令,即工作方式命令和C口位置位/复位命令。编程写入的命令保存在它的控制寄存器中。由于这两条命令是通过标志位(最高位)状态进行区别,所以可按同一地址写入且不受先后顺序限制。

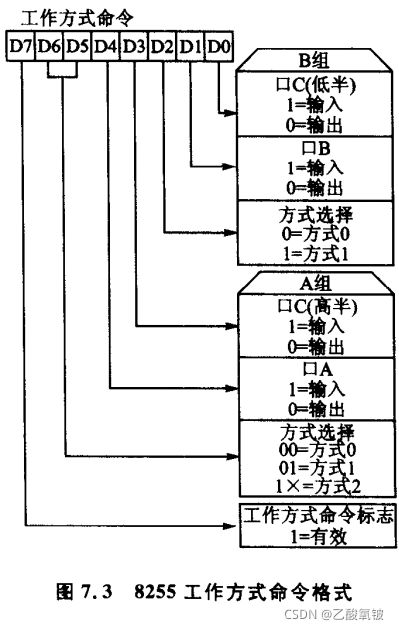

工作方式命令

工作方式命令用于设定各数据口的工作方式及数据传送方向。命令的最高位(D7)标志位,其状态固定为1。命令格式如图7.3所示。

对工作方式命令有如下两点说明:

- A口有3种工作方式,而B口只有两种工作方式;

- 在方式1和方式2下,对C口的定义(输入或输出)不影响作为联络信号使用的C口各位的功能。

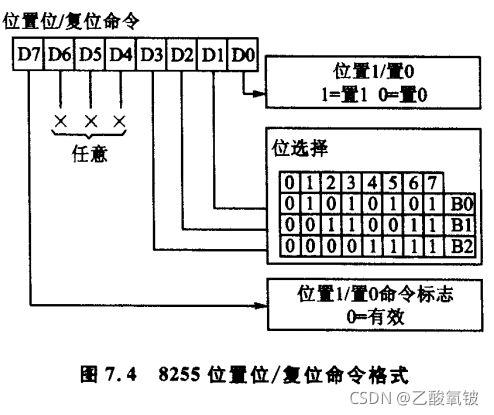

C口位置位/复位命令

在方式1和方式2下,C口用于定义控制信号和状态信号,因此,c口的每一位都可以进行置位或复位。对C口各位的置位或复位是由位置位/复位命令进行的。8255的位置位/复位命令格式如图7.4所示。

其中D7为该命令的标志,其状态固定为0。在使用时,该命令每次只能对C口中的一位进行置位或复位。

8255A端口地址的确定

上手编程

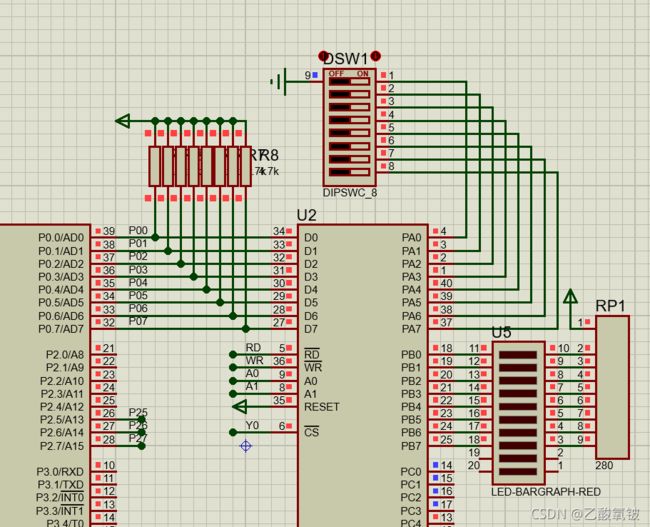

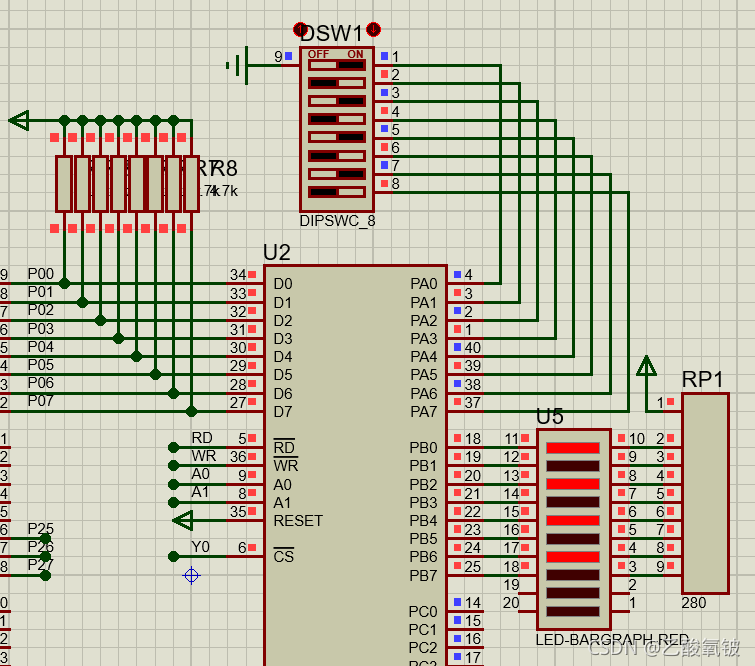

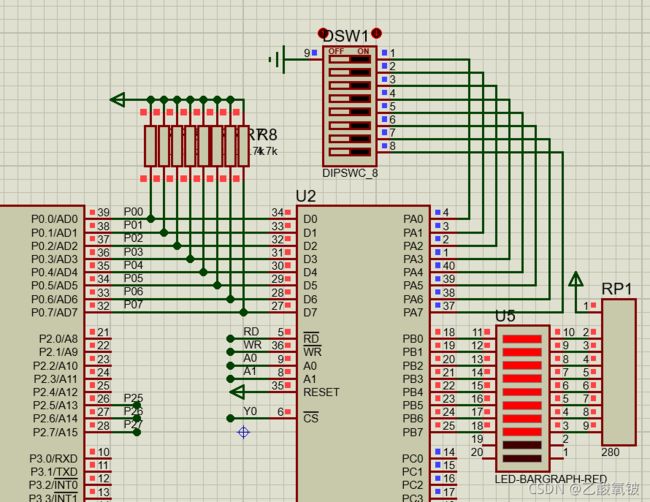

仿真原理图

确定相关地址

由原理图可知,当P25 = P26 = P27 = 0时,8255A被74LS373选通,且P00 与 A0相连,P01与A1相连,则有

8255A的地址: 000xxxxx 000000 A1 A0,没接的地址线设为1,则4个端口地址为:

PA口:0x1F00

PB口:0x1F01

PC口:0x1F02

控制口:0x1F03

测试源码

8255A.c

#include "8255A.h"

void Init_8255A(unsigned char A_Group_Mode, bit PA_Mode, bit PCH_Mode, bit B_Group_Mode, bit PB_Mode, bit PCL_Mode)

{

A_Group_Mode = (A_Group_Mode & 3) << 5;

A_Group_Mode = A_Group_Mode | 0x80 | (unsigned char)PA_Mode << 4 | (unsigned char)PCH_Mode << 3 | (unsigned char)B_Group_Mode << 2 | (unsigned char)PB_Mode << 1 | PCL_Mode;

COM_8255A = A_Group_Mode;

}

8255A.h

#ifndef _8255A_H_

#define _8255A_H_

#include main.c

将A组、B组均配置为模式0,PA口输入,PB口输出,PB口跟随PA口的电平状态。

#include