PCIe物理层及链路训练

PCIe物理层及链路训练之一

http://www.bnc.com.cn/gygj/xwzx/491.html

PCIe总线凭借其优良的传输性能和强大的扩展性和兼容性在各种数字系统中得到了广泛的应用,其最新的规范PCIe 5.0速率已提升至32GT/s,具有强大的应用潜力和前景。我司的板卡同样大量应用该总线实现系统的简化和扩展。实际经验中,大量的相关问题,如协商问题、降速、降lane、误码等,都发生在物理层。因此专题介绍PCIe物理层和链路协商的过程,同时配以实际应用中常见的相关问题,使读者深入理解PCIe物理层,并且得到依据这些知识进行问题定位的经验。

- PCIe物理层

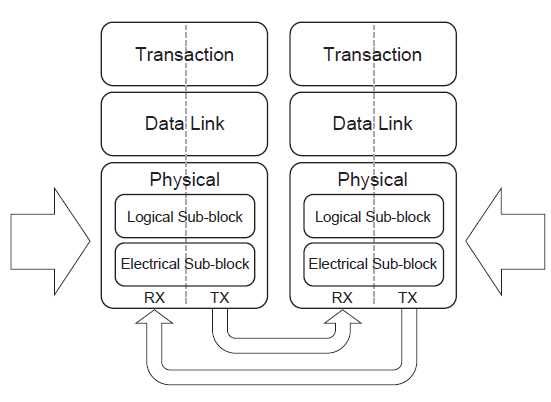

PCIe总线分为3个传输层,分别是物理层、数据链路层和传输层,其中物理层负责处理物理信号并与数据链路层进行数据交换,如下图所示:

图1 物理层示意图

物理层的主要功能包括:串并转换、 编解码(2.5GT/s\5GT/s速率下采用8b/10b编码,而8GT/s以上采用128b/130b编码)、差分信号的发送和接收、生成物理层报文PLP、链路初始化和链路训练。

- 8b/10b编码

2.5GT/s、5GT/s速率下采用8b/10b编码,而8GT/s以上采用128b/130b编码,本文以8b/10b编码为例讲解。链路进行编码的目的在于避免在链路上输出连续的“0”或连续的“1”,其原因如下:

- 接收器需要从链路上恢复时钟,该时钟用于接收器的采样等功能,而连续的“0”或 “1”会导致接收器无法稳定的恢复时钟。

- 发送器和接收器之间通过串接电容交流耦合,连续的“0”或 “1”包含的直流分量会受到耦合电容的衰减,导致在接收测无法分辨高低电平,从而造成误码。

- 链路需要保持直流平衡。

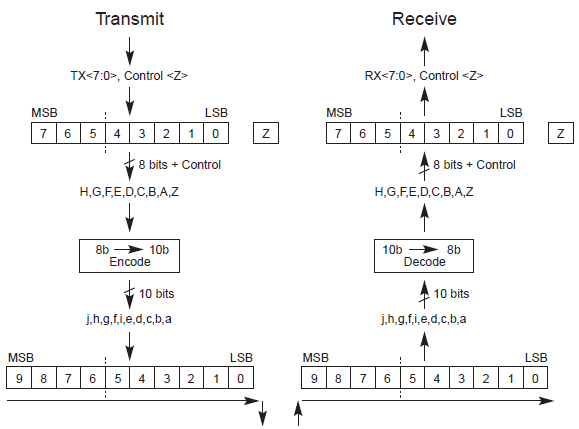

8b/10b编码在物理层的实现如下图所示,在发送过程中数据链路层的8bit数据转换为10bit数据输出在链路上;在接收侧将链路上接收到的10b数据转换为8bit后上传到数据链路层。

图2 8b/10b编码

来回转换的过程并非直接增加两个bit,而是根据ANSI X3.230-1994标准中规定的表格实现的,其中一个8bit数据对应两个10bit数据。所对应的10bit数中已经排除了其中包含连续的“0”或 “1”,因此经过编码后可以保证链路上不会出现连续的“0”或 “1”,从而实现上述目的。

PCIe链路在进入L0(正常工作状态)后就会启用8b/10b编码,因此在链路上无法像IIC总线一样看出链路传输的数据,而需要通过协议分析仪解码后再进行分析。再进入L0状态之前(即训练过程中),链路上的数据未使用8b/10b编码,在此阶段可以通过示波器进行观察其链路状态。

- 链路初始化和训练

PCIe链路需要通过链路初始化和链路训练的过程来建立连接,同时决定链路的宽度、链路速率、链路翻转和链路极性。

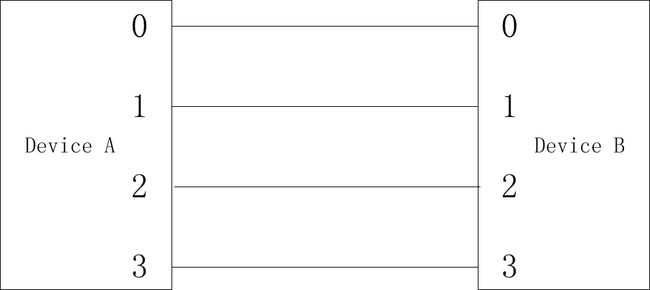

PCIe标准支持X1、X2、X4、X8等链路宽度,需要注意的是如果在X4链路中Lane0链路出问题,剩余3条Lane均正常,该链路并不能协商成X2链路或X1链路。除非两侧设备均支持Lane翻转。

链路速率由两个设备所支持的最高速率决定,在Polling阶段两个设备分别将速率信息写入TS1数据包中进行协商。

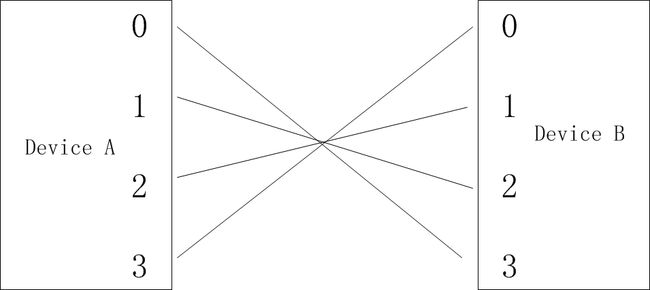

链路翻转的意义如下图所示,其目的在于便于链路的PCB走线。

链路极性翻转即差分信号中的正负信号反接,其目的也是在于方便PCB走线。需要注意的是无论是链路翻转还是极性翻转都建议尽量不要使用,原因在于不同厂家对这些功能的支持情况不同,可能导致设计失败的后果。

- LTSSM

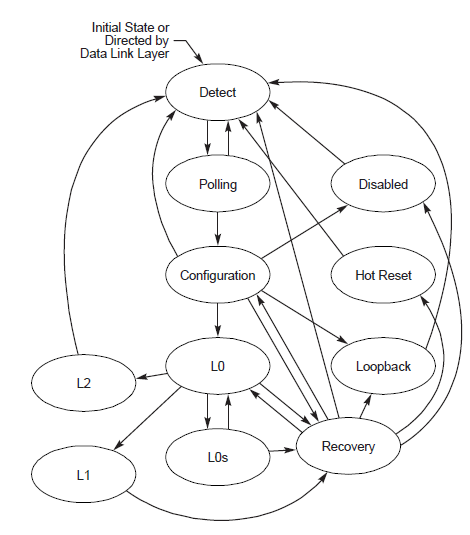

LTSSM意思是链路训练和状态状态机,控制链路建立、链路参数协商以及电源模式等。LTSSM是理解PCIe链路训练过程的关键,也是解决PCIE链路速率、宽度错误以及连接无法建立问题的重要依据。

正常的训练过程是Detect->Polling->Configuration->L0,其中L0即正常工作状态,而L0s、L1、L2均为不同等级的低功耗状态,Detect为检测在位,Polling阶段协商链路参数和锁定Symbol,Configuration阶段确认链路参数。

PCIe物理层及链路训练之二

http://www.bnc.com.cn/gygj/xwzx/493.html

上篇文章介绍了PCIe物理层和链路训练的基础,本章将详细介绍LTSSM(链路训练和状态的状态机)的第一个子状态——Detect。链路训练主要完成链路数据速率和链路宽度协商、Bit锁定与Symbol锁定、链路编号与对齐等,Detect作为LTSSM的第一个子状态,是完成这些功能的基础。

如果Detect环节出现错误,即使可以运行的之后的子状态也还会出现其他问题,最终都会导致链路不能正常工作。因此在PCIe链路异常时,应该首先考虑是否与Detect环节有关。

- Detect原理

Detect通过集成在发送器(Transmitter)中的接收器检测(Receiver Detection)电路实现,电路的功能在于检测接收器内的等效对地阻抗ZRX是否在40 Ω-60 Ω之间。PCIe总线支持热插拔,因此当对端设备没有插入时其ZRX为开路,则检测电路可以据此判断出对端无设备;而板内PCIe链路的芯片在复位状态或未上电等异常状态下其阻抗也会呈开路状态,。检测到对端没有设备的后续操作请见后文对Detect子状态状态机的介绍。

在位检测步骤如下:

- 发送器的输出保持在稳定的共模电平上;

- 发送器对共模输出差分对的D+和D-充电;

- 检测电路通过线路上电平变换的速率来判断接收器是否在位。

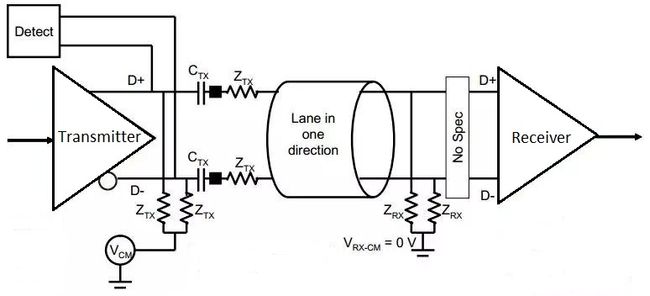

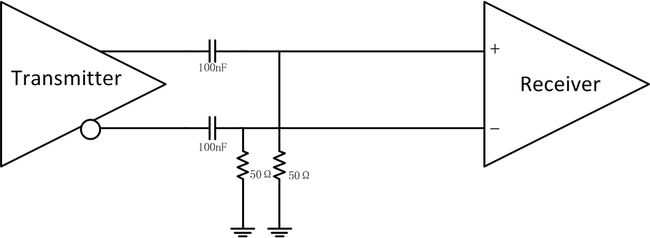

由图1可知若对端设备不在位,则CTX之后的电路不存在,此时的充电时间常数为ZTX (CTX + Cpad + Cinterconnect),其中CTX为发送器内阻,约为50Ω,Cpad为芯片引脚的寄生电容,Cinterconnect为链路的寄生电容,这两个参数都极小(pF级别)因而此时充电时间常数较低。

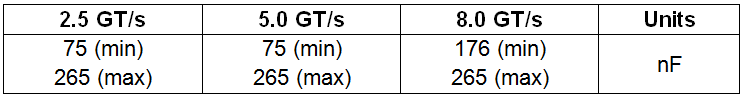

若对端设备在位,则充电时间常数约为ZTX (CTX + Cpad + Cinterconnect),其中CTX为耦合电容的容值,由表1可知其取值在75nF至265nF,远大于对端设备不在位时的两个电容参数(1nF=1000pF)。因而在位时充电时间常数较大。

表1 PCIe耦合电容要求

在实际的电气信号中,充电时间常数的测量是通过发送器输出共模的脉冲信号,当对端接收器不在位时发送器可以检测到脉冲信号的幅度几乎没有衰减;而当对端接收器在位时,脉冲信号需要对链路的耦合电容充电,因而幅度会明显降低。接收器在位检测电路通过脉冲幅度来判断充电时间常数的大小,进而得出接收器是否在位的结论。

- Detect子状态机

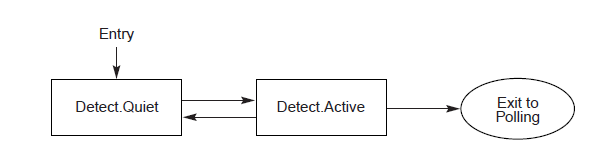

Detect状态主要有两个子状态Detect.Quiet、Detect.Active,其子状态机框图如图2所示。

1、Detect.Quiet

当设备冷启动、复位或从Polling、L2等其他状态进入Detect状态时,首先进入Detect.Quiet状态。

在此状态下,发送器处在电气闲(Electrical Idle)状态。电气闲状态是指发送器的D+和D-保持在同一恒定电平下,主要用于节点状态和非活动状态。发送器和对端的接收器之间通过电容串联耦合,因此在电气闲状态下接收器端差分信号两端都是0V电平。

Detect.Quiet在12ms超时后会进入下一子状态Detect.Active,或者检测到退出电气闲也会进入到Detect.Active状态。

2、Detect.Active

进入Detect.Active状态后立即进行接收器在位检测,如果所有的未配置Lane都检测到了接收器在位,则设备进入Polling状态;如果所有Lane都没有检测到接收器在位则进入Detect.Quiet状态。一个Lane指的是一组发送差分信号和一组接收差分信号。

其余情况为至少有一个Lane检测到了设备在位,但也有未配置的Lane未检测到接收器在位。此情况下回首先等待12ms,然后再次进行接收器在位检测。

- 如果检测结果与上次一致,且检测到在位的Lane可以组成1个或多个Link,则设备进入Polling状态。

- 否则设备进入Detect. Quiet。

那么如何判断能否组成Link呢?

这主要看设备的特性。Link指的是设备到设备的一个链接,一个Link可以是X4链路宽度,则指的是4个Lane组成该链路。如果一个设备有4个Lane,那么一种可能其只支持1个Link,即只有一个控制器,此时若只有Lane 0检测到接收器在位,那么可以形成一个X1宽度的Link,而若只有Lane 1检测到接收器在位,那么久无法形成Link,设备就会退回到Detect.Quiet子状态。如果这个设备支持4个Link,那么设备就可以协商成4个X1的链路,此时只有Lane 1检测到接收器在位也可行形成1个Link,设备会进入Polling状态。

链路两端的设备LTSSM是独立运行的,所以有时两端设备所处的状态会出现不一致的现象。例如上文的例子,链路两侧的设备都是X4且都检测到了Lane 1接收器在位,但是一个只支持1个Link而另一个可以支持4个Link,此时现象回事一个回到Detect.Quiet子状态而另一个会进入Polling状态。两个设备的训练状态机会独立运行同时又互相影响,因此常常需要从两个角度去分析才能找到定位问题的线索。

- Detect可能遇到的问题

由于各种原因导致连接断开或连接不良会导致Detect出现异常,使链路卡在Detect状态。体现到链路上的现象可能是发送信号线上都是0V电平或者24ms间隔的脉冲信号。24ms是由Detect.Quiet子状态的12ms超时和Detect.Active状态中等待12ms组成。

1、物理连接问题

这种情况多数是电容失效导致的,失效后短路、断路或容值偏移都会导致检测不到对端在位;另外连接器装配、芯片焊接不良也有可能出现此现象。

2、设置问题

对端设备处在复位或断电状态下,或是PCIe控制器未配置或使能,则会检测不到接收器在位。

在FPGA使用PCIe IP核的情况下,大量配置需要编程人员调整。其中检测接收器在位的阈值寄存器在默认值不合理的情况下则会导致误判为接收器不在位。默认值是经过大量验证的,一般情况下不会出现这种情况。

当出现链路Detect相关问题时,首先应该排查对端设备电源、复位和时钟状态,其次排查链路是否有失效器件或连接器问题。当难以判断是可以尝试在耦合电容连接接收器的一侧接50Ω电阻到GND,若此时设备可以通过Detect到达Polling状态或之后的状态,则基本可以确定问题在对端设备或是耦合电容之后的链路中,如图3所示。

在耦合电容后接电阻到GND后,可以保证在位检测电路可以正常检测到接收器在位,因此若设备正常则会进入到下一个状态。反之如果操作之后还是卡在Detect状态,则需要仔细排查本端设备的问题。

链路两端的设备训练状态机独立运行有相互影响,同时又常常涉及多个子状态,例如Detect、Polling,因此熟练掌握各个状态的进入条件和退出条件,再结合状态寄存器、链路信号的观察才可以找到能够帮助定位问题的线索。