乐鑫 SoC 内存映射入门

微控制器 (MCU) 的性能和内存能力逐步提升,其复杂度也随之加大。特别是当用户需要配置内存管理单元来映射外部存储器芯片 (Flash/SPIRAM) 时,这种现象尤其明显。

开始在乐鑫 SoC 上运行 Zephyr RTOS 时,会发现这些 SoC 与 ARM 架构的 MCU 相比,完全是不同的世界。ARM Cortex-M 基于冯-诺伊曼内存架构,而乐鑫 SoC 使用哈佛内存架构。架构不同,使用复杂度也有差异。

乐鑫为用户提供了很多开源文档,如《技术规格书》或《技术参考手册》是获取 SoC 技术信息的第一手资料。但这些内容对于一些用户来说,读起来颇具挑战,因为有一部分重要的信息被隐藏在冗长的文字描述中,用户很难快速获取核心重点。

本文将从《技术参考手册》中提取重要信息,并绘制成视觉丰富,内容详实的描述性文档。将本文与 SoC《技术规格书》和《技术参考手册》搭配使用,用户可以更好地理解乐鑫 SoC 的内部结构。这在系统开发和驱动开发过程中,例如在移植到 Zephyr RTOS 等其他系统时,尤其重要。

目录

ESP32

- ROM

- SRAM

- RTC-SRAM

- 指令 Cache & 数据 Cache

- 外设

- eFuse 块

ESP32-S2

- ROM

- SRAM

- RTC-SRAM

- 指令 Cache & 数据 Cache

- 外设

- eFuse 块

ESP32-S3

- ROM

- SRAM

- RTC-SRAM

- 指令 Cache & 数据 Cache

- 外设

- eFuse 块

ESP32-C3

- ROM

- SRAM

- RTC-SRAM

- 指令 Cache & 数据 Cache

- 外设

- eFuse 块

ESP32-C6

- ROM

- SRAM

- 指令 Cache & 数据 Cache

- 外设

- eFuse 块

资料下载

结语

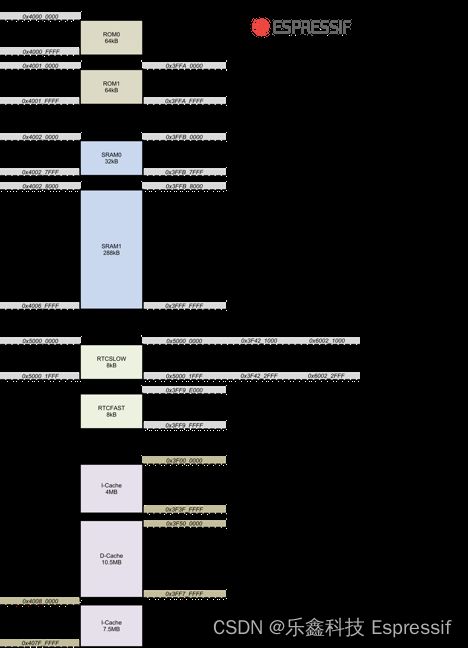

ESP32

ESP32 采用 Xtensa LX6 双核微处理器,是 ESP32 系列中最先发布的 SoC 产品。

此款 SoC 可使用 SPI 接口访问外部 flash 存储器。也可以访问外部 SPIRAM,但仅限通过数据总线访问。

点击链接可查看 Zephyr-RTOS 已支持的 ESP32 开发板。

-

ROM

ROM 用于存储主引导加载程序代码和其他用户可使用的库函数。ROM 中存储的内容已在生产过程中固化,不可更改。请参考《ESP32 系列芯片勘误表》查看更多 ECO 版本信息。TLDR 使用最新的 ECO v3 及之后的 ESP32 芯片版本。

-

SRAM

ESP32 内置三个 SRAM 模块。SRAM0 大小为 192 KB,头 64 KB 可配置为 MMU Cache,用于外部存储器访问。不作为 Cache 使用时,头 64 KB 可以被两个 CPU 通过指令总线读写。

内部 SRAM1 大小为 128 KB。既可以被两个 CPU 通过数据总线读写,也可以被两个 CPU 通过指令总线读写。

指令总线地址和数据总线地址访问的 word 是逆序的。

-

RTC-SRAM

RTC-FAST 内存仅能被 PRO_CPU 通过数据总线固定地址或指令总线固定地址访问。与其他内存不同,该内存不可通过 APP_CPU 访问。

RTC-SLOW 内存可以被两个 CPU 通过数据总线和指令总线读写。

RTC 内存可在 Deep-sleep 期间保存数据。

-

指令 Cache & 数据 Cache

指令和数据 Cache 地址空间为虚拟地址空间,指令或数据总线可以在其中访问 flash 或 SPIRAM 等外部存储器。

-

外设

ESP32 集成了 41 个外设。除 PID 控制器之外,其余外设都可以被两个 CPU 用相同地址访问。系统中有两个 PID 控制器分别服务于 PRO_CPU 和 APP_CPU。PRO_CPU 和 APP_CPU 都只能访问自己的 PID 控制器,不能访问对方的 PID 控制器。

-

eFuse 块

eFuse 内存为一次性可编程 (OTP) 内存,可用于存储硬件和加密配置参数。作为一种非易失性存储单位,eFuse 的 bit 一旦被烧写为 1,不可再恢复为 0。

请参考最新版《ESP32 技术参考手册》查看更多信息。

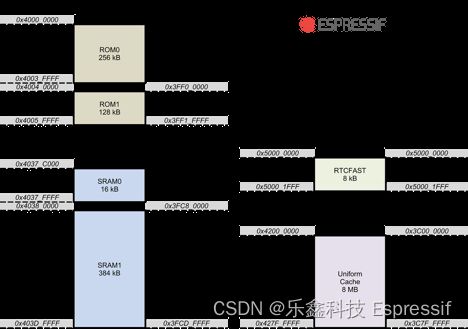

ESP32-S2

ESP32-S2 是基于 ESP32 的一款 SoC,与 ESP32 非常相似。但 ESP32-S2 属于单核 SoC,且内存组成略有不同。

与 ESP32 相比,ESP32-S2 可以通过数据总线和指令总线访问外部 SPIRAM,可以运行程序和访问数据。

点击链接可查看 Zephyr-RTOS 已支持的 ESP32-S2 开发板。

-

ROM

ROM 用于存储主引导加载程序代码和其他用户可使用的库函数。ROM 中存储的内容已在生产过程中固化,不可更改。

-

SRAM

ESP32-S2 的 SRAM0 可以配置为硬件 Cache,用于访问外部存储器。CPU 可以通过数据或指令总线同序进行读写访问。

-

RTC-SRAM

RTC-SLOW 内存可以被 CPU 通过数据总线和指令总线读写,也可以通过 PeriBus1 和 PeriBus2 访问。

-

指令 Cache & 数据 Cache

CPU 通过 Cache 访问外部存储器。通过 I-Cache 访问的地址空间可达 7.5 MB。通过 I-Cache 访问的只读数据总线地址空间可达 4 MB。可访问的外部 flash 或 SPIRAM 地址空间可达 10.5 MB。

-

外设

ESP32-S2 的外设可通过两个外设总线 PeriBus1 和 PeriBus2 进行访问。 每个外设总线在数据总线上都有自己的地址空间。

PeriBus1 具有预测性读的功能,可提高性能。但不能保证每次的读访问都有效。因此,在使用 PeriBus1 时需要使用易失性声明。但在访问特殊寄存器如 FIFO 时,必须使用 PeriBus2,访问速度虽然慢,但可以确保安全访问。

-

eFuse 块

eFuse 内存为一次性可编程 (OTP) 内存,包含 4096 个 bit,可用于存储硬件和加密配置参数。作为一种非易失性存储单位,eFuse 的 bit 一旦被烧写为 1,不可再恢复为 0。

请参考最新版《ESP32-S2 技术参考手册》查看更多信息。

ESP32-S3

ESP32-S3 是最新一款 Xtensa LX7 双核设计 SoC。除了两个主处理器外,ESP32-S3 还集成了两个超低功耗 RISC-V 协处理器。ESP32-S3 集成了一个 JTAG 调试器,可通过 USB 接口进行通信。ESP32-S3 还可以通过数据总线和指令总线访问外部 SPIRAM,可以运行程序和访问数据。

点击链接可查看 Zephyr-RTOS 已支持的 ESP32-S3 开发板。

-

ROM

ROM 用于存储主引导加载程序代码和其他用户可使用的库函数。ROM 中存储的内容已在生产过程中固化,不可更改。

-

SRAM

ESP32-S3 内置三个 SRAM 模块。SRAM0 可配置为 I-Cache buffer,用来访问外部存储器的指令。SRAM0 也可用作静态内存由指令总线使用。SRAM1 可以通过数据总线和指令总线进行读写访问。SRAM2 可以配置为 D-Cache,也用作静态内存,可以通过数据总线进行读写访问。

-

RTC-SRAM

RTC-SLOW 内存可以通过数据总线和指令总线读写。RTC-FAST 内存可以通过数据总线和指令总线固定地址进行读写访问。

-

指令 Cache & 数据 Cache

两个 CPU 可以通过缓存的 MMU 地址空间访问外部存储器。I-Cache 和 D-Dache 可通过指令总线或数据总线分别访问存储器。

-

外设

外设模块可使用数据总线或指令总线通过固定地址段进行访问。每个外设模块的基地址和地址空间大小,决定了其边界地址。外设地址空间大小一般为 4 KB。更多信息,请查看设备的技术参考手册。

-

eFuse 块

eFuse 内存为一次性可编程 (OTP) 内存,包含 4096 个 bit,可用于存储硬件和加密配置参数。作为一种非易失性存储单位,eFuse 的 bit 一旦被烧写为 1,不可再恢复为 0。

请参考最新版《ESP32-S3 技术参考手册》查看更多信息。

ESP32-C3

ESP32-C3 是一款 32 位 RISC-V SoC,自带 “IMC” 扩展。与 Xtensa SoC 相比,ESP32-C3 地址空间极其简单。ESP32-C3 支持 JTAG 调试,可通过片上 USB 接口进行通信。

点击链接可查看 Zephyr-RTOS 已支持的 ESP32-C3 开发板。

-

ROM

ROM 用于存储主引导加载程序代码和其他用户可使用的库函数。ROM 中存储的内容已在生产过程中固化,不可更改。

-

SRAM

ESP32-C3 有两个 SRAM 模块。SRAM1 可以配置为 I-Cache buffer,也用作静态内存。SRAM1 属于通用内存,可以通过数据总线和指令总线进行读写访问。

-

RTC-SRAM

RTC-FAST 内存可以通过 CPU 数据总线和指令总线读写。

-

指令 Cache & 数据 Cache

ESP32-C3 支持以 SPI、Dual SPI、Quad SPI、QPI 等接口形式访问片外 flash。ESP32-C3 还支持手动加密和自动解密。I-Cache 和 D-Dache 可通过指令总线或数据总线分别访问外部 flash。

-

外设

CPU 可通过数据/指令总线的固定地址空间访问外设模块。每个外设模块的基地址和地址空间大小,决定了其边界地址。地址空间大小一般为 4 KB。更多信息见技术参考手册。

-

eFuse 块

eFuse 内存为一次性可编程 (OTP) 内存,包含 4096 个 bit,可用于存储硬件和加密配置参数。作为一种非易失性存储单位,eFuse 的 bit 一旦被烧写为 1,不可再恢复为 0。

请参考最新版《ESP32-C3 技术参考手册》查看更多信息。

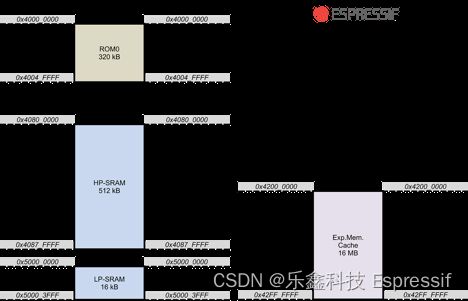

ESP32-C6

ESP32-C6 是一款 32 位 RISC-V SoC,自带 “IMAC” 扩展。与 Xtensa SoC 相比,ESP32-C6 地址空间极其简单。ESP32-C6 支持 JTAG 调试,可通过片上 USB 接口进行通信。

Zephyr-RTOS 对 ESP32-C6 开发板的支持正在开发中。

-

ROM

ROM 用于存储主引导加载程序代码和其他用户可使用的库函数。ROM 中存储的内容已在生产过程中固化,不可更改。

-

SRAM

ESP32-C6 有两个 SRAM 模块。

HP-SRAM 属于静态内存,HP CPU 和 LP CPU 可以通过数据总线或指令总线同序读写访问这部分内存。

LP-SRAM 属于静态内存,HP CPU 和 LP CPU 可以通过数据总线或指令总线读写访问这部分内存。可使用高速模式或低速模式访问 LP-SRAM。

-

指令 Cache & 数据 Cache

ESP32-C3 支持以 SPI、Dual SPI、Quad SPI、QPI 等接口形式访问片外 flash。ESP32-C6 还支持手动加密和自动解密,从而保护开发者片外 flash 中的程序和数据。

-

外设

CPU 可通过数据/指令总线的固定地址空间访问外设模块。每个外设模块的基地址和地址空间大小,决定了其边界地址。地址空间大小一般为 4 KB。更多信息见技术参考手册。

-

eFuse 块

eFuse 内存为一次性可编程 (OTP) 内存,包含 4096 个 bit,可用于存储硬件和加密配置参数。作为一种非易失性存储单位,eFuse 的 bit 一旦被烧写为 1,不可再恢复为 0。

请参考最新版《ESP32-C6 技术参考手册》查看更多信息。

资料下载

PDF 格式的图片可通过以下途径下载:

- ESP32

- ESP32-S2

- ESP32-S3

- ESP32-C3

- ESP32-C6

结语

有时候,当我们想要深入了解某些内容时,需要首先深入研究一些技术文档,然后再用我们自己的方式将有用信息提取出来,消化吸收。技术文档可能很难理解,如果不熟悉涉及的一些体系结构或特定领域,则更加难读懂技术文档。希望这篇博客可以让你轻松理解乐鑫 SoC 的内存映射。或者在你需要深入研究技术参考手册或技术规格书时,作为辅助参考使用。