高性能自动驾驶域控制器的关键要素设计

作者 | Jessie

出品 | 焉知

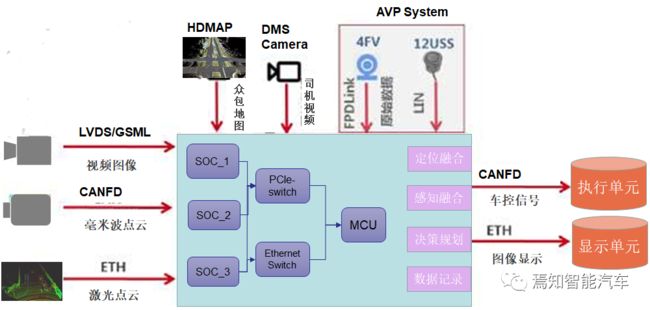

下一代自动驾驶系统设计中的迭代更新呈现巨大的变化,主要体现在功能上将不断迭代出更多新功能,如将原始L2.5或准L3级自动驾驶只能实现在高速路或快速路上的脱手驾驶(这里一般称之为高速路自动驾驶HWP或交通拥堵自动驾驶TJP功能),逐渐转变为适用在更广范围内的脱手驾驶(这里我们称之为点对点自动驾驶NGP或基于导航的点对点自动驾驶NOP),而后者则可以更多的适用在经过匝道的自动驾驶过程中。

此外,下一代自动驾驶在其性能上也出现了质的飞跃,如L2.5或准L3无法实现的脱眼驾驶将在下一代自动驾驶系统中被完美解决,更多地,下一代自动驾驶将实现诸如紧急转向自动避撞,恶劣天气状态下的长时间自动驾驶,突发状况下的紧急自动刹车等功能。要实现如上功能,除了在自动驾驶传感器上需要增加更多的盲区覆盖传感单元(如增加多个侧视摄像头、后视摄像头、前向或侧向激光雷达等),更需要在控制器端增加满足性能要求的域控制器单元,用于处理由于如上传感器递增所带来的巨大数据量。

如上数据处理的过程包含几个较大的方面,一般的对于下一代自动驾驶域控制器设计中主要关心如下文所述的几个基本需求。

感知数据输入与处理策略

1、摄像头视频/图像数据输入及处理策略

“车载摄像头”硬件需求一般常用MIPI摄像头作为对视频分辨率输入要求较高的场景中,他可以支持500万像素以上高清分辨率,对于下一代自动驾驶来说往往要求其摄像头分辨率至少在200w以上,这一需求对于MIPI接口来说完全足够。它的全称为“Mobile Industry Processor Interface”,分为MIPIDSI和MIPICSI,分别对应于视频显示和视频输入标准。

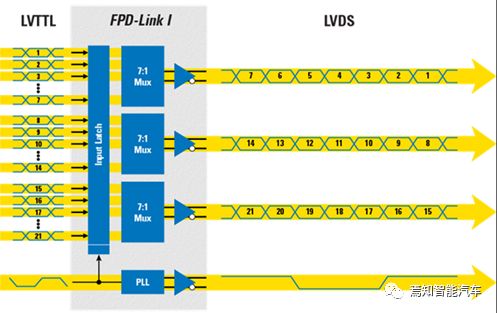

“车载摄像头”接口协议需求一般采用FPDLink或GMSL两种形态。其中,FPDLink是在LVDS基础之上建立起来的通信标准,也是第一次对LVDS规范的应用,FPD Link包括SERIALIZER和DESERIALIZER端。由于FPDLink更加适用于高速数字视频接口,因此,在下一代自动驾驶域控制芯片外围接口中应用更加广泛。GMSL是Maxim公司推出的一种高速串行接口,适用于视频、音频和控制信号的传输,使用50Ω同轴电缆或100Ω屏蔽双绞线(STP)电缆时的距离可达15m或更长。FPDLink与GMSL在视频传输上实际没有明显的区别,关键还是看定点的摄像头供应商是否支持该接口协议。

此外,对于面向下一代自动驾驶系统的图像处理技术,也会需要在如下相应的方面做出较大的提升。

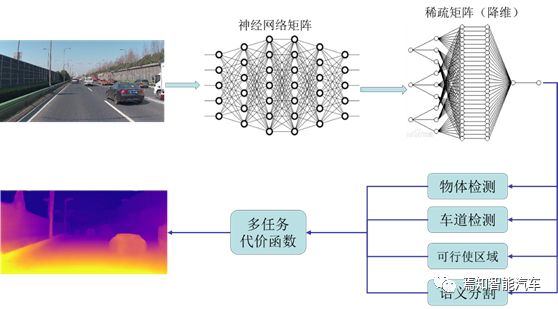

①差异化的应用:即图像处理将面对不同的应用场景,如包含目标对象的实际检测、可行驶区域检测、场景语义分割、驾驶员监控、视觉SLAM等。

②高算力和高计算性能:即图像处理过程中需要系统具备足够的算力将数万亿次的深度学习算法数据运行起来,同时需要确保该原酸效力能够达到最优。

③神经网络加速能力:网络加速即包含对相关处理单元(如CPU、GPU、TPU、FPGA、DSP等)的最大性能、灵活性、功耗及嵌入式代价问题的实际处理能力。

这里我们需要重点讲一下关于网络阵列最优化过程能力。该过程主要是通过将转换张量划分为3-D切片来实现。具有数百甚至数十亿参数的深度网络,传统 CPU 对如此庞大的网络一筹莫展,只有具有高计算能力的 GPU 才能让网络得以相对快速训练。在自动驾驶感知数据处理过程中,对于具有更多层和节点的更大的神经网络,减少其存储和计算成本变得至关重要,在深度学习的另一端,即移动车端,如何让深度模型在域控制器上有效运行,也是模型压缩加速的一大重要目标。网络模型的压缩和加速的最终实现需要多学科的联合解决方案,除了压缩算法,数据结构、计算机体系结构和硬件设计等也起到了很大作用。

除开如上视频数据信息处理策略外,在视频接口输入输出时还需要重点考虑自动驾驶视频图像得串/并行数据转化终端,在通用场景中,自动驾驶系统的设计师们会采用串行器/解串器(SERDES)技术的高速串行接口来取代传统的并行总线架构。串/并数据转化接口一般采用SERializer/DESerializer对其输入(信号)进行串并行(解串)转换。基于SERDES的设计增加了带宽,减少了信号数量,同时带来了诸如减少布线冲突、降低开关噪声、更低的功耗和封装成本等许多好处。而SERDES技术的主要缺点是需要非常精确、超低抖动的元件来提供用于控制高数据速率串行信号所需的参考时钟。即使严格控制元件布局,使用长度短的信号并遵循信号走线限制,这些接口的抖动余地仍然是非常小的。

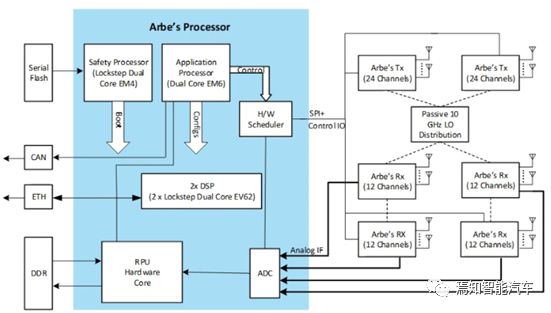

2、雷达数据输入及处理策略

在自动驾驶域控制器设计过程中,其雷达数据的连接口通常采用CANFD或ethernet模式进行接入。

对于毫米波雷达而言,下一代自动驾驶系统即便是集中式控制方案仍旧按照探测结果数据进行处理,因此还是采用CANFD接入数据。而对于激光雷达而言,则是直接对原始点云数据的处理,则通常采用ethernet进行数据接入。这里我们需要注意几个比较重要的设计策略,其一是对CAN唤醒的数量需要根据实际功能需求来定。其二是CAN接口分配需求需要充分考虑MCU算力承载能力,是否能够确保将传感数据融合算法纳入进来,融合这一部分算法的数据量相对于MCU传统的车控算力是比较大的,一般的MCU无法承载该算力需求。因此很多情况下,传感数据融合算法通常是放到SOC中间的。对于激光雷达而言采用以太网的传输方式,则需要充分考虑到原始数据源的数据量,目前看来,主流的百兆激光雷达能承载的数据量相对较少,而对于高线束的激光雷达则需要千兆以太网进行数据输入。而ethernet接口通常采用Broad-R-Reach能达到车规级,也可在量产开发中预留RJ45接口作为调试接口。

此外,自动驾驶中的通常会采用多路毫米波雷达介入相关感知数据。一般采用至少五组毫米波雷达进行感知输入,正常情况下则至少需要5个以上的CANFD连接端。在一般的SOC芯片设计中不会设置如此多的CAN通道数,正常情况下设置4路CANFD是比较常见的。因此,毫米波雷达量产的时候可通过CAN ID号区分雷达的不同位置,因此只要带宽足够,多个雷达可以同时挂到一个CAN总线上,这样可以节省不少CAN接口。

3、高精定位输入及处理策略

对于高精定位输入接口设计而言,在下一代自动驾驶系统的输入接口也通常沿用当前的状态,采用ethernet进行输入,而原始地图众包或点云数据通常出现较大的数据量,这就要求以太网升级为至少1000M/s以太网,以确保数据量的无疏漏且实时的传输。同时高精定位源会实时接入外围感知定位数据端,包括IMU、RTK甚至轮速信息等,因此设计过程中需要预留更多的以太网接口。

而在高精定位处理策略中,则是将原始的分布式数据处理方式变更为集中式数据处理方式。即,原始地图定位端只提供地图众包数据,上层ADS域控制器处理的信息则更多的需要融合IMU、轮速、RTK等数据信息。这使得整个定位融合算法会较多的占用MCU芯片的算力,一般情况下这种数据融合会放置到SOC中进行,这样可以再确认定位信息无疏漏的情况下,大大减少MCU的算力负担。

车载SOC芯片数据存储

首先我们需要讲解SOC的数据存储和交换问题。以上问题涉及到关于AI芯片的外围接口或外置存储器到底能够执行怎样的任务。一般的,外围存储器应该具备的如下的功能项,运算数据临时存储单元,算法程序临时存储单元,较大容量临时存储单元。

一般的,主流的SOC存储及交换单元主要包含LDDR、Flash及eMMC;内存是SOC中数据与CPU进行沟通的桥梁,SOC中的所有程序的运行都是在内存中进行的,因此内存的性能对计算机影响非常大。LPDDR作为面向低功耗而指定的通信标准,以低功耗和小体积著称,可专门用于移动式车载芯片控制端。面向车载移动平台的LPDDR4,其能够在带来等效的性能(速度)的同时,兼顾更少的能源消耗。因此LPDDR4从成熟度和应用广泛性上目前是主流SOC芯片主要的内存平台,不过LPDDR5的兴起也将有逐渐代替LPDDR4的整体趋势。

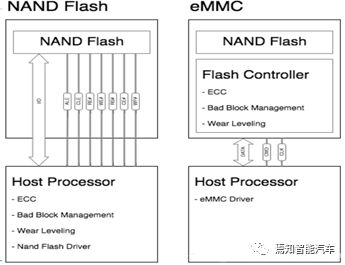

除开LDDR这种内存形式外,为了允许在操作中多次擦除或写入相关数据,以及在SOC与其他数据输入输出端交换临时传输数据,可以增加一定数量的快闪存储器。NAND Flash具有较快的抹写时间,而且每个存储单元的面积也较小,这让NAND Flash相较于NOR Flash具有较高的存储密度与较低的成本,同时它的可抹除次数也高出NOR Flash十倍。因此,在SOC芯片外围一般采用NAND Flash闪存。

此外,SOC芯片在通常设计外围接口存储器eMMC(embedded Multi Media Card)将NAND Flash芯片(Flash内存阵列)、Device Controller芯片封装到一块。Flash控制器负责管理内存,并且提供标准接口,使得eMMC能够自动调整主机与从机的工作方式,没有位数限制,不需要处理其他繁杂的NAND Flash兼容性和管理问题。从而大幅降低多芯片的空间占用和布线难度问题。对于自动驾驶芯片来说,应用eMMC来存放处理程序是一个非常常用的方式。

多芯片数据交互

对于下一代自动驾驶系统架构设计而言,往往不是一块或两块SOC芯片能够解决其数据交互问题的,常有的情况是采用2-4片SOC进行AI数据处理。对于双芯片设计时可直接通过连接中介交互信息,而当设计多于2路芯片时,通过这些芯片发送出来的数据信息应该至少有数十路的信息交互。因此,多芯片交互信息需要加入数据交换单元Switch进行数据交互。一般大数据传输采用的数据传输PCIe,一般的数据传输采用ethernet、GPIO。因此,对于数据交换单元Switch而言,主要包括ethernet Switch、PCIe Switch的数据中转单元作为数据交换及数据管理的中介。

Ethernet Switch的工作基础是Ethernet信息包结构。Ethernet信息包为固定格式,但长度可变,在信息包头中带有目的MAC地址、源MAC地址、信息长度等若干内容。Ethernet 交换机是根据Ethernet包中的源MAC地址来更新“MAC地址—端口号表”的,每一台计算机打开后,其上面的NIC会定期发出空闲包或信号,Ethernet 交换机可据此得知其存在及MAC地址。若一定时间内未见已出现的MAC地址发出包,则将此MAC地址从“MAC—端口号表”中清除,此MAC地址重新出现时将会被当作新地址处理。

SOC的外围存储控制器之间需要做各种数据交换和同步,一般都是采用PCI-E,这将增加其连接上对通道数量的消耗。对于一般的车载域控制器端,普遍都是采用的多路存储配置,去掉一些用于管理、内部嵌入式PCI-E设备的通道占用之后,需要的PCIe通道数也是相当可观的,因此将多个独立的控制器芯片连接到同一片Switch上,可以进行有效的信息交互。并可以覆盖几乎所有应用场景。当然需要在PCI-E Switch内部将对应的数据包进行地址映射翻译进行Partition, 以便确保数据交互的有效性。

如上两种数据连接Switch的作用主要有三个方面,其一是确保自动驾驶系统架构有效的实现双冗余控制,其二是通过如上两种线路Switch可以更好地实现时钟同步,其三是通过线路可确保数据传输的带宽足够支撑整个自动驾驶数据的传输。

总结

自动驾驶高端域控制器的设计过程中需要涉及多个方面的内容,其中包含的硬件部分就有芯片、外围存储器、MCU车端逻辑控制、数据传输控制中介等方面。软件部分更多的涉及如何在各个芯片内部放置不同的软件算法模块,以便在达到预期功能设定的同时更能提升软件性能要求(这部分主要指软件功能安全要求)。这两方面设计要求系统工程师、软件工程师、硬件工程师相互同理配合才能确保在设计之初能够尽可能多的满足后期开发需求。

欢迎加入智能交通群!加微信号automan332,标注”加群“。