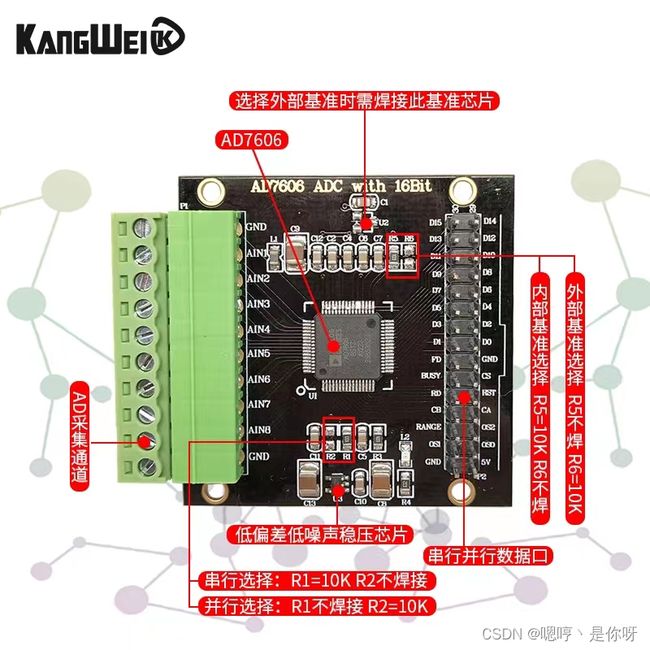

AD7606数据采集模块使用方法

1. 简介

AD7606是一块八通道,双极性输入,同步采样16位ADC。内置2.5V基准电压。由于AD7606没有内部的寄存器,需要直接利用引脚配置ADC的模式,所以AD7606的控制原理也是很简单,但是需要占用的I/O口的资源很多。

- 输入箝位保护,以承受最高达±16.5V的电压

- 16 位电荷再分配逐次逼近型 ADC内核

- 数字滤波器

- 2.5V基准电压源及缓冲

- 高速串行和并行接口(SPI/QSPI/DSP等兼容)

- 5V单电源供电

- 支持真正±10V 或±5V 的双极性信号输入

- 所有的通道均能以高达 200 kSPS 的速率进行采样

- 内置低噪声、高输入阻抗的信号调理电路,其等效输入阻抗完全独立于采样率且固定为 1MΩ

- 内置2.5V 带隙电压基准和基准缓冲电路,其温度系数典型值为±10ppm/℃,使用内部基准和外部基准可选

- 过采样和数字滤波功能

2. 引脚功能

D0-D7 并行数据接口

D8-D15 串行数据接口

VCC 电源

GND 电源地

OS0:LSB控制位

OS2 OS1 OS2 : 的组合状态选择过采样模式。

000表示无过采样,最大200Ksps采样速率。

001表示2倍过采样, 也就是硬件内部采集2个样本求平均

010表示4倍过采样, 也就是硬件内部采集4个样本求平均

011表示8倍过采样, 也就是硬件内部采集8个样本求平均

100表示16倍过采样, 也就是硬件内部采集16个样本求平均

101表示32倍过采样, 也就是硬件内部采集32个样本求平均

110表示64倍过采样, 也就是硬件内部采集64个样本求平均

过采样倍率越高,ADC转换时间越长,可得到的最大采样频率就越低。

RANGE:采样范围,±10V 或±5V

CA、CB:转换开始输入A和转换开始输入B。逻辑输入。这些逻辑输入用来启动模拟输入通道转换。要对所有输入通道同时采样,可以将他们短接在一起,并施加一个转换开始信号。

- CVA,CVB : 启动AD转换的控制信号。CVA决定1-4通道,CVB决定5-8通道。 2个信号可以错开短暂的时间。一般情况可以将CVA,CVB并联在一起。

RST:复位输入,当为高电平1时,RESET上升沿复位AD7606。期间应该在上电后收到一个RESRT脉冲。RESET高脉冲宽度典型值为50ns。如果在转换期间施加RESET脉冲,转换将中断。如果在读取期间施加RESET脉冲,输入寄存器内的内容将复位至全0.

RD:选择并行接口时为并行数据读取控制输入(RD),选择串行接口时为串行时钟输入(SCLK)。在并行模式下,如果CS和RD同时处于低电平0时,则会启用输出总线。在串行模式下,此引脚用作数据传输的串行时钟输入。CS下降沿使数据输出线路DoutA和DoutB脱离三态,并逐个输出转换结果的MSB。SCLK上升沿将随后的所有数据位逐个送至串行数据输出DoutA和DoutB。

BUSY:输出繁忙。CA和CB都到达上升沿后,此引脚变为1,表示转换过程已经开始。BUSY保持1,知道所有通道转换过程完成。BUSY下降沿表示转换数据正在被锁存至输出数据寄存器,经过时间t后便可供读取。在BUSY为高电平1时执行数据读取操作应当在下降沿之前完成。当BUSY为高电平1时,CA或CB的上升沿不起作用。

CS:片选。低电平输入使能数据帧传输。在并行模式下,如果CS和RD同时处于低电平1,则会使能输出总线D0-15,使转换结果输出在并行数据总线上。

在串行模式下,利用CS使能串行数据帧传输,并逐个输出串行输出数据的最高有效位(MSB)

FD:FRSTDATA 数字输出,第1个通道样本的指示信号片选信号。它输出信号用来指示何时在并行、字节或串行接口上回读第一通道V1.当CS输入为高电平时,FD输出引脚处于三态。CS下降沿使FD脱离三态。 在并行模式下,与V1结果相对应的RD下降沿随后将FD引脚设为高电平1,表示输出数据总线可以踢动V1的结果。。在RD的下一个下降沿之后,FD输出恢复逻辑低电平0. 在串行模式下,FD在CS下降沿变为高电平1,因为此时将在DoutA上输出V1的MSB。。在CS下降沿之后的第16个SCLK下降沿,它恢复低电平0.。

D7: DoutA 并行数据位或者串行接口数据输出引脚

D15: BYTE SEL 并行数据位或者并行字节模式选择。

3. 说明

(1)AD7606提供了三种接口选项【参考】:并行接口、高速串行接口和并行字节接口。

(2)AD7606的BUSY引脚电平为高时表示AD正在进行转换,变低表示转换完成。将BUSY引脚接到STM32的外部中断引脚并配置为下降沿触发,这样可以在AF转换完成后及时读取数据。

(3)OS[0..2]为过采样配置引脚,通过控制STM32相关GPIO的电平可以是AD7606工作在不同的过采样状态。

(4)CONVST_A,CONVST_B为转换触发信号,上升沿触发。对于每一个AD7606来说,CONVST_A控制模拟通道1~4,CONVST_B控制模拟通道5~8。由于需要对所有通道同步采样,因此将CONVST_A,CONVST_B引脚同时连接在一个触发信号引脚上以实现同步采样。

(5)REFOUT引脚为外部基准电压输入引脚。AD7606可以配置为使用内部基准电压或外部基准电压。当两片AD7606同时工作时,使用外部基准电压可以保证所有输入通道转换精度的一致性。外部基准电压源选择ADR421,ADR421为2.5V基准电源,具有出色的噪声性能、稳定性和精度【参考】,可以满足AD对基准电压源的精度要求。

(6)模数转换的数据对应

(7)串行传输过程分析

- CAB正跳变>ts,开始转换,BUSY变高电平。busy由高到低,完成一次转换。BUSY为低时,拉低CS,可以读取数据,读取完成,拉回高电平。

- 一个数据16位,先高八位,后低八位。读取一个完整的字节,需要连续读取两次。

- 总共8个通道,从1到8,连续顺序传输。所以,通道n的高八位就是第2(n-1)+1次读取,低八位是2(n-1)+2次读取。

- spi传输函数每次读8位。

4. 应用

AD7606模块一般搭配单片机使用(51单片机、STM32等),单片机采集到数据后可考虑使用串口将数据发送至PC端显示。

(1)程序思路: