24Bit Σ-Δ ADC——AD7124的多通道初始化配置

24Bit Σ-Δ ADC——AD7124的多通道初始化配置

- 一、前言

- 二、ADC寄存器介绍

-

- 1. 配置寄存器

- 2. 滤波寄存器

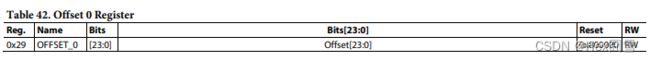

- 3. 偏置寄存器

- 4. 增益寄存器

- 5. 诊断寄存器

- 三、通道与CONFIG_x的映射

-

- 多对1映射

- 1对1映射

- 混合映射

- 四、实验数据

一、前言

AD7124是目前常用的一种24位ADC,在全功率模式、9.4SPS的速率、gain = 128的状态运行,均方根(rms)可达到23nV;信号误差在±10uV左右,单片价格在¥135~150,对于测控仪器中采集芯片的选型来说,该芯片价位处于中端层面,性价比较高。

AD7124的引脚排布、硬件SPI的驱动方式我已经在上一篇文章发布过,这里不再做过多赘述,链接如下:

使用stm32的硬件SPI驱动AD7124的方法

二、ADC寄存器介绍

首先介绍一下AD7124几个常用寄存器的基本功能。我们以AD7124-4BRUZ为例,它有8个独立的设置,每个设置都包含了如下寄存器:

- 配置寄存器(Configuration register)

- 滤波寄存器(Filter register)

- 偏置寄存器(Offset register)

- 增益寄存器(Gain register)

1. 配置寄存器

配置寄存器允许用户选择ADC设置为双极性或单极性模式时的输出编码。

在双极性模式下,ADC可以采集到负电压,输出编码为偏移二进制(offset binary),采集范围是-VREF/gain ~ +VREF/gain

在单极性模式下,ADC只能采集正电压,输出编码为标准二进制(straight binary),采集范围是0 ~ +VREF/gain

在这两种情况下, 输入电压必须包含AVDD和AVSS。用户可以使用这些寄存器选择参考源,四个选项都是可用的:

1个内部2.5V参考源、1个连接REFIN1(+)和REFIN1(-)的外部参考源、1个连接REFIN2(+)和REFIN2(-)的外部参考源或以AVDD-AVSS作为参考。PGA提供了1、2、4、8、16、32、64和128倍增益。模拟输入缓存(buffer)和参考输入缓存都可以用寄存器使能。

下图为滤波寄存器0的寄存器位,Bit[15:12]是保留位,默认0;Bit11 =0为单极性,为1双极性;

2. 滤波寄存器

是一个24bit寄存器,滤波寄存器下选为数字滤波器被用于ADC调制器的输出。滤波器型号和数据输出速率在设置寄存器位时被选择。

最高3位是滤波器组数,可以用000-111代表Filter0-7;REJ60为60Hz开启数字抑制器位,写1开启,默认为50Hz抑制器;高8位的Bit[3:1]设置前置滤波器,Bit0为1开启单循环;中8位的Bit[7:4]为保留位,默认0,FS[10:8]至FS[7:0]是过滤器寄存器中要写进去的的十进制数,可以从1到2047。

不同的设置会影响输出数据速率、处理时间。

3. 偏置寄存器

增益寄存器是保持ADC增益校准系数的24位寄存器。增益寄存器是读/写寄存器。在gain=1时增益系数被校准;因此,默认值因设备而异。如果一个内部或系统全范围校准被用户初始化,默认值被自动覆写。更多信息,请看偏置滤波器部分。

4. 增益寄存器

AD7124-4有八个增益寄存器,从GAIN_0到GAIN_7。每个增益寄存器都与一个设置相关联,GAIN_x与设置x相关联。增益寄存器是24位寄存器,并保存ADC的满量程校准系数。AD7124-4的出厂校准增益为1。增益寄存器在上电和复位后包含这个工厂生成的值。

增益寄存器是读/写寄存器。

然而,当写入寄存器时,ADC必须处于待机模式或空闲模式。如果用户发起内部或系统满量程校准,则默认值将自动覆盖

或者写入满量程寄存器。

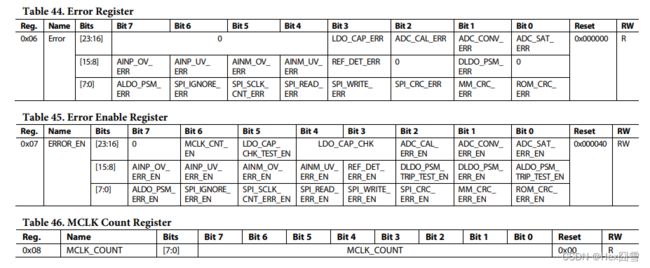

5. 诊断寄存器

又叫ERROR Registers,ERROR_EN寄存器可以使能或失能AD7124的众多诊断程序。默认下,SPI_IGNORE功能是使能的,这个位可以指示写ADC时不恰当的次数(例如,在上电和复位期间)其他诊断包括:

- SPI读和写检查,确保只有合法的寄存器才能被访问

- SCLK计数器,确保正确的SCLK脉冲数被使用

- SCLK CRC校验

- 内存分布 CRC校验

- LDO检查

当一个诊断被使能,在错误寄存器内包含相应的标志位。所有的使能标志位在状态寄存器内被命令去控制ERR flag。因此,如果发生一个错误(例如,SPI CRC校验检测到1个错误),在错误寄存器中有关的标志位会被设置(例如SPI_CRC_ERR标志位)。在状态寄存器中ERR标志位总是被置位的。ERR位表示是否发生错误。用户可以读取错误寄存器以获得关于错误源的更多信息。

三、通道与CONFIG_x的映射

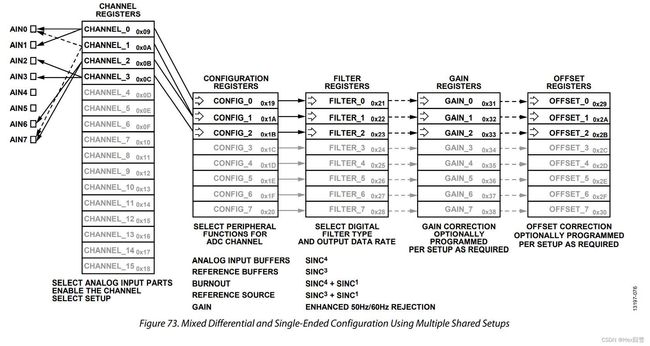

图70是ADC配置寄存器与滤波、增益和偏置寄存器的关系,按照逻辑来说需要一步步地去配置,且他们之间存在几种不同的对应关系,不同的配置组合会对采样造成不同的影响,首先我们需要理解配置的灵活性(Flexibility)。

多对1映射

图71展示了CH0~CH3的通道配置,被称为Single Setup用灰色字体显示的寄存器暂时用不上。这4个差分通道均采用同一组配置寄存器,CONFIG_0的配置被4个通道共用。

Single Setup适合单通道采集,若不同的通道均采集同一范围的信号,也适用Single Setup。

下列代码展示了如何配置Single Setup:

void AD7124_Multiple_INIT(uint8_t SamHz)//多通道初始化函数

{

AD7124_Reset();

AD_Delay(500);

//写AD7124 控制寄存器

AD7124_Write_Reg(AD7124_ADC_CTRL_REG,2,AD7124_ADC_CTRL_REG_REF_EN | AD7124_ADC_CTRL_REG_POWER_MODE(3) | AD7124_ADC_CTRL_REG_MODE(0) | AD7124_ADC_CTRL_REG_CLK_SEL(0) | AD7124_ADC_CTRL_REG_CS_EN);

AD7124_Write_Reg(AD7124_CH0_MAP_REG,2,AD7124_CH_MAP_REG_CH_DISABLE | AD7124_CH_MAP_REG_SETUP(0) | AD7124_CH_MAP_REG_AINP(0) | AD7124_CH_MAP_REG_AINM(1));

AD7124_Write_Reg(AD7124_CH1_MAP_REG,2,AD7124_CH_MAP_REG_CH_ENABLE | AD7124_CH_MAP_REG_SETUP(0) | AD7124_CH_MAP_REG_AINP(2) | AD7124_CH_MAP_REG_AINM(3));

AD7124_Write_Reg(AD7124_CH2_MAP_REG,2,AD7124_CH_MAP_REG_CH_ENABLE | AD7124_CH_MAP_REG_SETUP(0) | AD7124_CH_MAP_REG_AINP(4) | AD7124_CH_MAP_REG_AINM(5));

AD7124_Write_Reg(AD7124_CH3_MAP_REG,2,AD7124_CH_MAP_REG_CH_ENABLE | AD7124_CH_MAP_REG_SETUP(0) | AD7124_CH_MAP_REG_AINP(6) | AD7124_CH_MAP_REG_AINM(7));

//写AD7124 配置0寄存器

AD7124_Write_Reg(AD7124_CFG0_REG,2,AD7124_CFG_REG_UNIPOLAR | AD7124_CFG_REG_AIN_BUFP | AD7124_CFG_REG_AINN_BUFM | AD7124_CFG_REG_REF_SEL(2) | \

AD7124_CFG_REG_PGA(7));

//单极性 | 打开ADC+缓冲 | 打开ADC-缓冲 | REF_SEL(x) x=0 REFIN1(+)/REFIN1(-) x=1 REFIN2(+)/REFIN2(-) x=2 内部基准电压源 x=3 AVDD

//REG_PGA(x) 0-7对应增益1(±2.5V) 2(±1.25V) 4(± 625mV ) 8(±312.5 mV ) 16(±156.25 mV) 32(±78.125 mV) 64(±39.06mV) 128(±19.53mV)

Samprate=SamHz;

switch(SamHz)

{

case Samprate_2Hz:

AD7124_Write_Reg(AD7124_FILT0_REG,3,AD7124_FILT_REG_FILTER(0) | AD7124_FILT_REG_REJ60 | \

AD7124_FILT_REG_POST_FILTER(0) | AD7124_FILT_REG_FS(384));

break;

case Samprate_5Hz:

AD7124_Write_Reg(AD7124_FILT0_REG,3,AD7124_FILT_REG_FILTER(0) | AD7124_FILT_REG_REJ60 | \

AD7124_FILT_REG_POST_FILTER(0) | AD7124_FILT_REG_FS(200));

break;

case Samprate_10Hz:

AD7124_Write_Reg(AD7124_FILT0_REG,3,AD7124_FILT_REG_FILTER(0) | AD7124_FILT_REG_REJ60 | \

AD7124_FILT_REG_POST_FILTER(0) | AD7124_FILT_REG_FS(100));

break;

case Samprate_20Hz:

AD7124_Write_Reg(AD7124_FILT0_REG,3,AD7124_FILT_REG_FILTER(0) | AD7124_FILT_REG_REJ60 | \

AD7124_FILT_REG_POST_FILTER(0) | AD7124_FILT_REG_FS(50));

break;

case Samprate_50Hz:

AD7124_Write_Reg(AD7124_FILT0_REG,3,AD7124_FILT_REG_FILTER(0) | AD7124_FILT_REG_REJ60 | \

AD7124_FILT_REG_POST_FILTER(0) | AD7124_FILT_REG_FS(22));

break;

case Samprate_100Hz:

AD7124_Write_Reg(AD7124_FILT0_REG,3,AD7124_FILT_REG_FILTER(0) | AD7124_FILT_REG_REJ60 | \

AD7124_FILT_REG_POST_FILTER(0) | AD7124_FILT_REG_FS(11));

break;

case Samprate_200Hz:

AD7124_Write_Reg(AD7124_FILT0_REG,3,AD7124_FILT_REG_FILTER(0) | AD7124_FILT_REG_REJ60 | \

AD7124_FILT_REG_POST_FILTER(0) | AD7124_FILT_REG_FS(5));

break;

case Samprate_500Hz:

AD7124_Write_Reg(AD7124_FILT0_REG,3,AD7124_FILT_REG_FILTER(0) | AD7124_FILT_REG_REJ60 | \

AD7124_FILT_REG_POST_FILTER(0) | AD7124_FILT_REG_FS(2));

break;

case Samprate_1kHz:

AD7124_Write_Reg(AD7124_FILT0_REG,3,AD7124_FILT_REG_FILTER(2) | AD7124_FILT_REG_REJ60 | \

AD7124_FILT_REG_POST_FILTER(0) | AD7124_FILT_REG_FS(1));

break;

}

}

1对1映射

//函数: 多通道初始化函数,初始1号AD7124的1-3通道

//变量: 无

//返回值: 无

void AD7124_Multiple_INIT(void)//多通道初始化函数

{

AD7124_Reset();

AD_Delay(500);

//写AD7124 控制寄存器

AD7124_Write_Reg(AD7124_ADC_CTRL_REG,2,AD7124_ADC_CTRL_REG_DATA_STATUS | AD7124_ADC_CTRL_REG_REF_EN | AD7124_ADC_CTRL_REG_POWER_MODE(3) | AD7124_ADC_CTRL_REG_MODE(0) | AD7124_ADC_CTRL_REG_CLK_SEL(0) | AD7124_ADC_CTRL_REG_CS_EN);

//通道指示 | 内部参考打开 | POWER_MODE(x) x=0 低功耗 x=1 中功率 x=2、3全功率 | CTRL_REG_MODE(x) x=0 连续转换模式 x=1 单次转换模式 其他模式请看手册 | CLK_SEL(x) x=0 内部 x=2 外部

//写AD7124 通道0寄存器,0号通道不开启

//使能通道0 | 用配置0 | AINP(x) ADC+选择 0-15对应通道0-15 | AINM(x) ADC-选择 0-15对应通道0-15 其他通道请查看手册

AD7124_Write_Reg(AD7124_CH0_MAP_REG,2,AD7124_CH_MAP_REG_CH_DISABLE | AD7124_CH_MAP_REG_SETUP(0) | AD7124_CH_MAP_REG_AINP(0) | AD7124_CH_MAP_REG_AINM(1));

//写AD7124 通道1寄存器

//使能通道1 | 用配置1 | AINP(x) ADC+选择 0-7对应通道0-7 | AINM(x) ADC-选择 0-7对应通道0-7 其他通道请查看手册

AD7124_Write_Reg(AD7124_CH1_MAP_REG,2,AD7124_CH_MAP_REG_CH_ENABLE | AD7124_CH_MAP_REG_SETUP(1) | AD7124_CH_MAP_REG_AINP(2) | AD7124_CH_MAP_REG_AINM(3));

//写AD7124 通道2寄存器

//使能通道2 | 用配置2 | AINP(x) ADC+选择 0-7对应通道0-7 | AINM(x) ADC-选择 0-7对应通道0-7 其他通道请查看手册

AD7124_Write_Reg(AD7124_CH2_MAP_REG,2,AD7124_CH_MAP_REG_CH_ENABLE | AD7124_CH_MAP_REG_SETUP(0) | AD7124_CH_MAP_REG_AINP(4) | AD7124_CH_MAP_REG_AINM(5));

//写AD7124 通道3寄存器

//使能通道3 | 用配置3 | AINP(x) ADC+选择 0-7对应通道0-7 | AINM(x) ADC-选择 0-7对应通道0-7 其他通道请查看手册

AD7124_Write_Reg(AD7124_CH3_MAP_REG,2,AD7124_CH_MAP_REG_CH_ENABLE | AD7124_CH_MAP_REG_SETUP(0) | AD7124_CH_MAP_REG_AINP(6) | AD7124_CH_MAP_REG_AINM(7));

//写AD7124 配置1寄存器

AD7124_Write_Reg(AD7124_CFG1_REG,2,AD7124_CFG_REG_UNIPOLAR | AD7124_CFG_REG_AIN_BUFP | AD7124_CFG_REG_AINN_BUFM | AD7124_CFG_REG_REF_SEL(2) | \

AD7124_CFG_REG_PGA(7));

//单极性 | 打开ADC+缓冲 | 打开ADC-缓冲 | REF_SEL(x) x=0 REFIN1(+)/REFIN1(-) x=1 REFIN2(+)/REFIN2(-) x=2 内部基准电压源 x=3 AVDD

//REG_PGA(x) 0-7对应增益1(±2.5V) 2(±1.25V) 4(± 625mV ) 8(±312.5 mV ) 16(±156.25 mV) 32(±78.125 mV) 64(±39.06mV) 128(±19.53mV)

//写AD7124 配置2寄存器

//单极性 | 打开ADC+缓冲 | 打开ADC-缓冲 | REF_SEL(x) x=2 内部基准电压源 | REG_PGA(6) 6对应增益64(±39.06mV)

AD7124_Write_Reg(AD7124_CFG2_REG,2,AD7124_CFG_REG_UNIPOLAR | AD7124_CFG_REG_AIN_BUFP | AD7124_CFG_REG_AINN_BUFM | AD7124_CFG_REG_REF_SEL(2) | \

AD7124_CFG_REG_PGA(6));

//写AD7124 配置3寄存器

//单极性 | 打开ADC+缓冲 | 打开ADC-缓冲 | REF_SEL(x) x=2 内部基准电压源 | REG_PGA(5) 5对应增益32(±78.125 mV)

AD7124_Write_Reg(AD7124_CFG3_REG,2,AD7124_CFG_REG_UNIPOLAR | AD7124_CFG_REG_AIN_BUFP | AD7124_CFG_REG_AINN_BUFM | AD7124_CFG_REG_REF_SEL(2) | \

AD7124_CFG_REG_PGA(5));

//写AD7124 滤波寄存器1 500Hz

//FILTER(x)x=0 sinc4 x=2 sinc3 x=7 后置滤波器 其他请查看手册 | 打开60Hz陷波 | POST_FILTER(x) 后置滤波器设置查看手册 | FS(x)具体滤波配置查看网址

AD7124_Write_Reg(AD7124_FILT1_REG,3,AD7124_FILT_REG_FILTER(2)|AD7124_FILT_REG_REJ60|AD7124_FILT_REG_POST_FILTER(0) | AD7124_FILT_REG_FS(2));

//写AD7124 滤波寄存器2 500Hz

//FILTER(x)x=0 sinc4 x=2 sinc3 x=7 后置滤波器 其他请查看手册 | 打开60Hz陷波 | POST_FILTER(x) 后置滤波器设置查看手册 | FS(x)具体滤波配置查看网址

AD7124_Write_Reg(AD7124_FILT2_REG,3,AD7124_FILT_REG_FILTER(2)|AD7124_FILT_REG_REJ60|AD7124_FILT_REG_POST_FILTER(0) | AD7124_FILT_REG_FS(2));

//写AD7124 滤波寄存器3 500Hz

//FILTER(x)x=0 sinc4 x=2 sinc3 x=7 后置滤波器 其他请查看手册 | 打开60Hz陷波 | POST_FILTER(x) 后置滤波器设置查看手册 | FS(x)具体滤波配置查看网址

AD7124_Write_Reg(AD7124_FILT3_REG,3,AD7124_FILT_REG_FILTER(2)|AD7124_FILT_REG_REJ60|AD7124_FILT_REG_POST_FILTER(0) | AD7124_FILT_REG_FS(2));

}

混合映射

配置原理和上述相同,不同的是AIN6/AIN7可以被配置到CHANNEL2,也就是说3号通道可以被被知道通道1的寄存器上,

四、实验数据

下列是几个不同通道,设置不同组Config后采集的数据(照片拍得有点糊,见谅……),2通道使用CINFIG_1的配置,3通道使用CONFIG_2,而PT1000的通道采用CONFIG_0。

在实际应用中,不同的通道应配置不同的组数,以防配置信息代码产生耦合。