嵌入式培训-Linux系统及C编程高级-DAY19~21-make file

Makefile概述

Makefile的重要性

会不会写makefile,从一个侧面说明了一个人是否具备完成大型工程的能力

如果不用makefile,也可以用gcc命令编译,但是文件多的时候,gcc很长,不便使用,所以要用makefile

Makefile概述

make是一个命令工具,是一个解释makefile中指令的命令工具,一般来说,大多数的IDE(集成环境)都有这个命令,比如:Delphi的make,Visual C++的nmake,Linux下GNU的make。可见,makefile都成为了一种在工程方面的编译方法。

“自动化编译”:一旦写好(指的是makefile 文件),只需要一个make命令,整个工程完全自动编译,极大的提高了软件开发的效率 (makefile文件的m可以大写也可以小写,但程序优先访问小写的)

提升编译效率:再次编译,只编译修改的文件

Makefile基本语法

target... : prerequisites ...

command (注意command前边有个tab)

target(目标)也就是一个目标文件,可以是Object File,也可以是执行文件。还可以是一个标签(Label),对于标签这种特性,在后续的“伪目标”章节中会有叙述。

prerequisites(依赖,多个文件以空格隔开)就是,要生成那个target所需要的文件或是目标。

command也就是make需要执行的命令。(任意的Shell命令)

(先创建一个叫makefile的文件,文件内容按上面写的来。完成之后,在linux下直接打make命令,就自动编译了。makefile文件默认识别第一个目标,如果有多个目标,要理顺先后顺序,让第一个目标的依赖里包含后面的目标)

Makefile创建变量的目的

用来代替一个文本字符串:

1.系列文件的名字

2. 传递给编译器的参数

3. 需要运行的程序

4. 需要查找源代码的目录

5. 你需要输出信息的目录

6. 你想做的其它事情。

自定义变量

x = a 变量在声明时需要给予初值

$(x)或${x} 取值

如果你要使用真实的 $ 字符,那么你需要用 $$ 来表示。

Makefile变量的赋值

自动变量

$* 不包含扩展名的目标文件名称

$+ 所有的依赖文件,以空格分开,并以出现的先后为序,可能包含重复的依赖文件

$< 第一个依赖文件的名称

$? 所有时间戳比目标文件晚的的依赖文件,并以空格分开

$@ 目标文件的完整名称

$^ 所有不重复的目标依赖文件,以空格分开

$% 如果目标是归档成员,则该变量表示目标的归档成员名称

(如果想确认哪个变量具体是什么内容,可以用echo 命令把内容打出来)

Makefile的隐含变量

AR 库文件维护程序的名称,默认值为ar。

AS 汇编程序的名称,默认值为as。

CC C编译器的名称,默认值为cc。 (就是gcc编译的命令里的cc)

CPP C预编译器的名称,默认值为$(CC) –E。

CXX C++ 编译器的名称,默认值为g++。

FC FORTRAN编译器的名称,默认值为f77

RM 文件删除程序的名称,默认值为rm -f

ARFLAGS 库文件维护程序的选项,无默认值。

ASFLAGS 汇编程序的选项,无默认值。

CFLAGS C编译器的选项,无默认值。

LDFLAGS 链接器的选项,无默认值

CPPFLAGS C预编译的选项,无默认值。

CXXFLAGS C++编译器的选项,无默认值。

FFLAGS FORTRAN编译器的选项,无默认值

(如果程序在别的平台上跑,需要别的编译器来编译,那就用这些命令)

Makefile的条件判断

ifeq 判断是否相等 ifeq(a,b)

ifneq 判断是否不相等

ifdef 判断是否定义过 (后面可以接变量。只有在makefile文件里赋值过的变量才算定义过,返回true。)

ifndef 判断是否未定义过

Makefile常用函数

基本语法:

$(

或是

${

多个参数用逗号隔开

Makefile函数

$(wildcard PATTERN)

功能:列出当前目录下所有符合模式“PATTERN”格式的文件名。

返回:空格分割的、存在当前目录下的所有符合模“PATTERN”的文件名。

说明:“PATTERN”使用shell可识别的通配符,包括“?”(单字符)、“*”(多字符)等。

示例:$(wildcard *.c)返回值为当前目录下所有.c源文件列表。

$(patsubst

名称:模式字符串替换函数。

功能:查找

返回:函数返回被替换过后的字符串。

示例: $(patsubst %.c,%.o,x.c.c bar.c) 把字串 x.c.c bar.c 符合模式 %.c 的单词替换成 %.o ,返回结果是 x.c.o bar.o

Makefile自定义函数

示例:

$(call

define 定义

endef 结束定义

make的使用

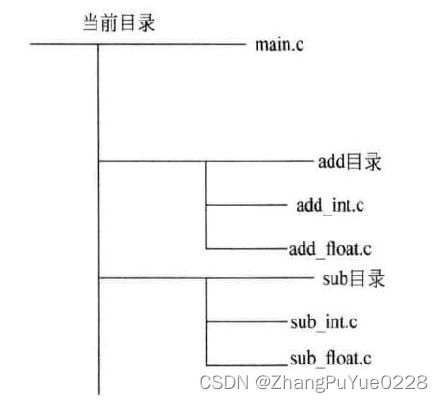

-C dir读入指定目录下的Makefile

-f file读入当前目录下的file文件作为Makefile

-i 忽略所有的命令执行错误

-n 只打印要执行的命令,但不执行这些命令

-s 在执行命令时不显示命令

-w 如果make在执行过程中改变目录,打印当前目录名

其他命令可以man make查看手册