CPU控制硬件原理

本地开发和交叉开发

- 本地开发:本地编写代码,本地编译代码,本地运行代码

- 交叉开发:本地编写代码,本地编译代码,开发板运行代码

- PC中Linux下,程序也能执行,但不是仿真。他是真正的运行。但你移植到ARM平台就不一定能执行,需要转化代码的指令。这个转换过程你可以当成是交叉编译。

交叉编译工具链

交叉编译工具链的安装

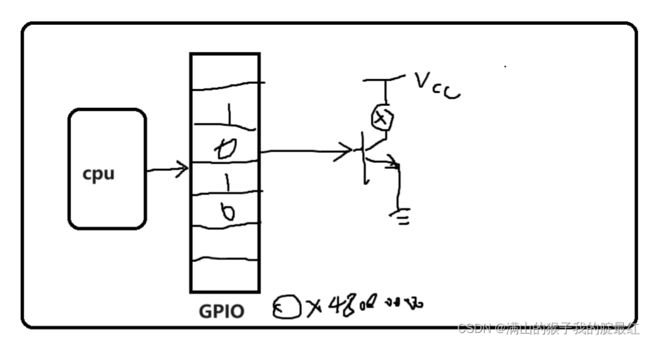

cpu控制硬件原理

我们学习的所有指令,六大指令里边,只有内存访问指令(ldr/str)能访问cpu之外的内容。那cpu如何控制硬件?

load/store指令 --》操作外设寄存器

芯片有一个地址映射表。告诉你地址空间是如何映射的,便于我们找到对应的硬件地址。

我们的SoC型号是S5P6818,对应的芯片用户手册为:S5P6818X用户手册V0.00

S5P6818X用户手册V0.00

其中一章是:Memory map或Memory Controller中的一张表中可以看地址隐射关系。

硬件控制原理:

CPU不能直接控制硬件,硬件是由其对应的外部寄存器(存储器)来控制的

每个外部寄存器(存储器)都会映射到CPU寻址范围内的一段空间

CPU通过对寄存器(存储器)的读和写实现对硬件间接的控制

LED实验

- 查看电路原理图

FS6818底板原理图

FS6818核心板原理图

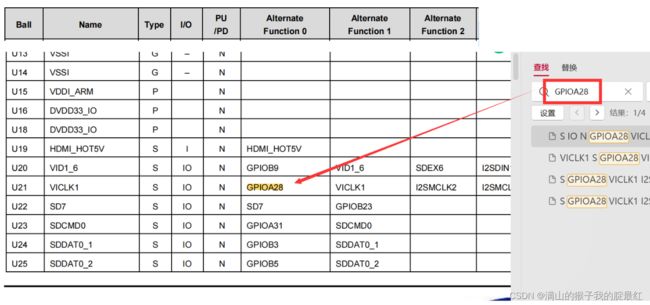

根据引脚追连线电路。最终追到核心板cpu引脚GPIOA28 (引脚复用多个功能)。

引脚是芯片里外交流的载体。名字反映功能,多个名字多个功能。

- 查看用户芯片手册

第二章介绍了每个IO引脚的作用。---》function Table查看功能(重点看:function 0-3)

找到引脚根据自己的情况选择对应功能。

GPIO:通用的输入输出接口。 一共160个,ABCDE每组32个。

CPIOA28:A组的第28个

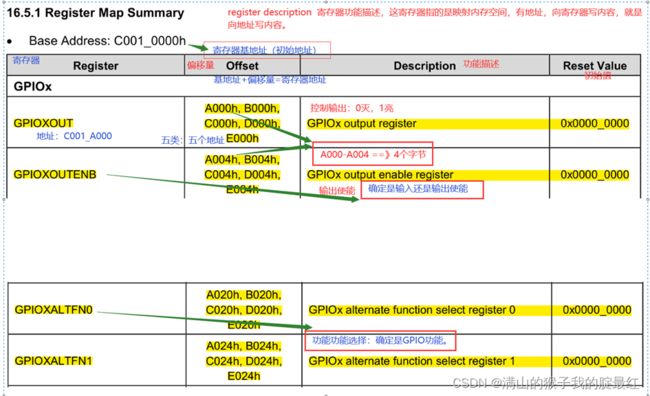

- 查看对应GPIO硬件映射的地址(寄存器:这将能控制硬件的空间叫寄存器,在cpu外,有地址)--》找到寄存器描述(Register Description)

引脚是硬件,硬件控制都会隐射到内存的一个地址。所以操作硬件就是操作内存。

每个寄存器怎么控制实现不同功能:

1.GPIOxALTFN0和GPIOxALTFN1两个寄存器:控制一个GPIO引脚功能,A类GPIO有32个引脚,即需要八个字节管理A类GPIO引脚。 ‘x’--》ABCDE

2.GPIOxOUTENB寄存器:

- GPIOxOUT寄存器:

- 实验步骤简写

1.分析电路原理图得出LED的控制方法----》高电平亮/低电平灭

2.分析电路原理图得出LED与SOC的连接关系 - GPIOA28

3.分析芯片手册,找到对应的寄存器将GPIOA28设置成GPIO功能->GPIOAALTFN1(0xC001A024)

4.分析芯片手册,找到对应的寄存器将GPIOA28设置成OUTPUT功能->GPIOAOUTENB(0xC001A004)

5.分析芯片手册,找到对应的寄存器将GPIOA28设置输出高/低->GPIOAOUT(0xC001A000)

- 汇编代码实现

1》控制led灯亮代码

.text

.global _start

_start:

/*

GPIOAALTFN1

地址:0xC001A024 数据:0x00000000

GPIOAOUTENB

地址:0xC001A004 数据:0x10000000

GPIOAOUT

地址:0xC001A000 数据:0x10000000/0x00000000

*/

@ 设置GPIOA28为GPIO功能

LDR R1,=0x00000000

LDR R2,=0xC001A024

STR R1,[R2]

@ 设置GPIOA28为OUTPUT功能

LDR R1,=0x10000000

LDR R2,=0xC001A004

STR R1,[R2]

@ 设置GPIOA28输出低电平(因为本来就是亮的,这里让他熄灭)

LDR R1,=0x00000000

LDR R2,=0xC001A000

STR R1,[R2]

STOP:

B STOP @死循环

.end

虚拟机中编译生成的二级制文件.bin 如何在板子上运行:参考文档如下。

超级终端的使用

系统移植实验手册

LED灯闪烁

/*

硬件控制原理:

CPU不能直接控制硬件,硬件是由其对应的控制器(寄存器)来控制的

每个控制器(寄存器)都会映射到CPU寻址范围内的一段空间

CPU通过对控制器(寄存器)的读和写实现对硬件间接的控制

*/

.text

.global _start

_start:

/*

实验步骤

1)分析电路原理图,得出LED的控制方式 -> 高电平亮,低电平灭

2)分析电路原理图,得出LED与SOC的连接关系 -> GPIOA28

3)分析芯片手册,找到对应的寄存器将GPIOA28设置成GPIO功能->GPIOAALTFN1(0xC001A024)

4)分析芯片手册,找到对应的寄存器将GPIOA28设置成OUTPUT功能->GPIOAOUTENB(0xC001A004)

5)分析芯片手册,找到对应的寄存器将GPIOA28设置输出高/低->GPIOAOUT(0xC001A000)

*/

/*

GPIOAALTFN1

地址:0xC001A024 数据:0x00000000

GPIOAOUTENB

地址:0xC001A004 数据:0x10000000

GPIOAOUT

地址:0xC001A000 数据:0x10000000/0x00000000

*/

MAIN:

BL LED_CONFIG

LOOP:

BL LED_ON

BL DELAY @延时 通过执行多条汇编指令延时

BL LED_OFF

BL DELAY

B LOOP

LED_CONFIG:

@ 设置GPIOA28为GPIO功能

LDR R1,=0x00000000

LDR R2,=0xC001A024

STR R1,[R2]

@ 设置GPIOA28为OUTPUT功能

LDR R1,=0x10000000

LDR R2,=0xC001A004

STR R1,[R2]

MOV PC,LR @将链接寄存器中跳转前下条指令的地址给pc回去

LED_OFF:

@ 设置GPIOA28输出低电平

LDR R1,=0x00000000

LDR R2,=0xC001A000

STR R1,[R2]

MOV PC,LR

LED_ON:

@ 设置GPIOA28输出高电平

LDR R1,=0x10000000

LDR R2,=0xC001A000

STR R1,[R2]

MOV PC,LR

DELAY:

LDR R1,=100000000

T:

SUB R1,R1,#1 @R1=R1-1

CMP R1,#0 @R1 是否和0想等

BNE T @不相等继续跳到T执行

MOV PC,LR

.end