PIPE Interface解析之信号解析(SerDes&Original共有)

Data Interafce

PHY的input信号

TxData

1 Original架构:

TxData[31:0]/[15:0]/[7:0]分别对应32/16/8bits的interface,低位的symbol先发送出去。

2 SerDes架构:

TxData[79:0]/[39:0]/[19:0]/[9:0]分别对应80/40/20/10bits的interface,在Gen1和Gen2的时候,80/40/20/10bits分别对应8/4/2/1个Symbol,每一个bit都被使用到;在Gen3和Gen4和Gen5的时候,80/40/20/10bits分别对应8/4/2/1个Symbol,每一个Symbol的高2bit不用。

TxDataValid

1指示PHY该数据可以使用,0指示PHY该数据不可以使用。

Rx+,Rx-

PHY的差分输入信号。

PHY的output信号

Tx+,Tx-

PHY的差分输出信号。

RxData

1 Original架构:

RxData[31:0]/[15:0]/[7:0]分别对应32/16/8bits的interface,低位的symbol先接收。

2 SerDes架构:

RxData[79:0]/[39:0]/[19:0]/[9:0]分别对应80/40/20/10bits的interface,在Gen1和Gen2的时候,80/40/20/10bits分别对应8/4/2/1个Symbol,每一个bit都被使用到;在Gen3和Gen4和Gen5的时候,80/40/20/10bits分别对应8/4/2/1个Symbol,每一个Symbol的高2bit不用。

Command Interafce

PHY的input信号

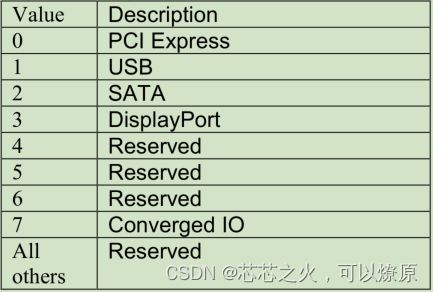

PHY Mode[3:0]

具体的含义如下:(该信号在PHY仅仅支持一种模式的时候可以不需要)

SerDesArch

1代表是SerDes PIPE架构,0代表是Original PIPE架构。

SRISEnable

该信号用于告诉PHY去支持SRIS。MAC必须在第一次终端检测(Receiver Detection)之前设置该信号。

注:在PCLK作为PHY的输出模式时,必须在配置PLL之前设置SRISEnable。

TxDetectRx/Loopback

该信号高电平有效,用于告诉PHY去开始做终端检测或者开始Loopback操作。

注:当做终端检测的时候,如果此时PHY的电源状态的PCLK是可以被门控的,则此时该信号是异步的,在其他状态下,该信号都是同步到PCLK上的。

TxElecIdle[3:0]

该信号高电平有效,用于强制Tx进入电气空闲状态除了在Loopback模式下。

注:MAC必须始终拉高TxDataValid信号不管TxElecIdle信号是否有效。

1 Original架构:

该信号仅仅使用bit[0],其他三个bits不用。

2 SerDes架构:

一个bit对应2个Symbol的数据,例如80bit位宽的interface,TxElecIdle[0]对应该位宽下的Symbol0和Symbol1。对于位宽更小的interface,则对应高位可以不被使用。

Reset#

该信号低位有效,异步复位信号,用于复位Tx和Rx。

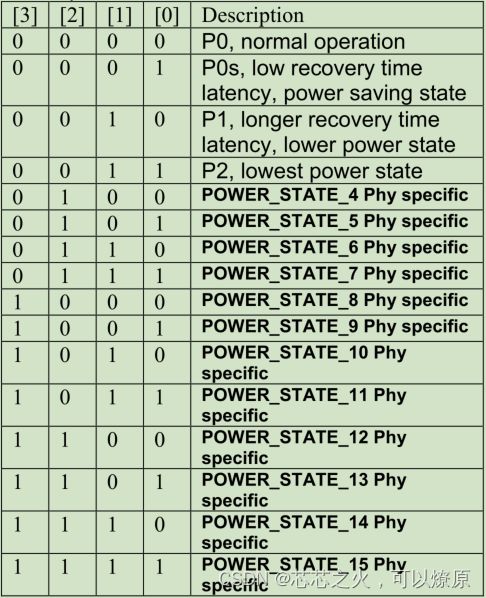

PowerDown[3:0]

该信号用于指示当前PHY的电源状态,具体如下:

注:在PCLK作为PHY的输出模式下,当PHY从P2切换到P1的时候,该信号是异步的(因为此时PCLK是不工作的)。

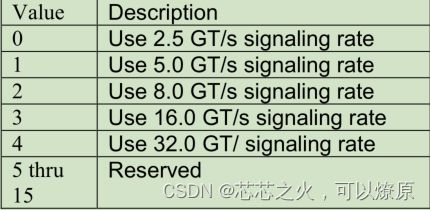

Rate[3:0]

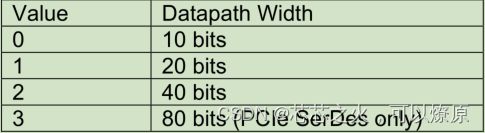

Width[1:0]

该信号用于控制PIPE数据的位宽,具体如下:

1 Original架构:

如果EncodeDecodeBypass为0,则:

2 SerDes架构:

如果EncodeDecodeBypass为1或者在SerDes架构,则:

注:对于SerDes架构,Width[1:0]仅仅用于Tx这边的数据,Rx这边的数据有RxWidth[1:0]控制。

PCLK Rate[4:0]

RxStandby

该信号低电平有效,当PHY处于P0或者P0s状态时,用于控制PHY的Rx是否active,0代表active,1代表standby。

PHY的output信号

RxStandbyStatus

该信号低电平有效,用于指示PHY的RxStanby的状态,0代表active,1代表stanby。RxStandbyStatus反映了高速Rx此时的状态。

注:当PHY处于P1或者P2状态时,RxStandbyStatus是没有定义的。

Status Interface

PHY的input信号

PclkChangeAck

该信号高电平有效,仅仅用于PCLK作为PHY的输入模式,MAC在PCLK rate改变或者rate改变的时候拉高该信号,此时要求width改变已经完成而且width稳定。

MAC拉高PclkChangeAck之后,PHY会拉高一个cycle的PhyStatus并且同时拉低PclkChangeOk信号作为响应,当Controller采样到PclkChangeOk为低,则拉低PclkChangeAck信号。

AsyncPowerChangeAck

该信号高电平有效,仅仅用于没有PCLK存在的两个电源状态之间的转换,具体如下:

PHY通过拉高PhyStatus去指示power state转换完成后,MAC通过拉高AsyncPowerChangeAck信号直到PhyStatus为低去响应。

注:该信号仅仅用在PHY支持PCIe L1 Substate的时候。

PHY的output信号

RxValid

该信号高电平有效,用于指示Symbol Lock,RxDataK和RxData上的有效数据。

PhyStatus

该信号高电平有效,用于指示PHY成功的完成了某些行为,例如电源管理和终端检测等行为,需要PHY拉高一个cycle的PhyStatus信号。

RxElecIdle

该信号高电平有效,用于指示Rx电气空闲状态,用于5/8/16/32GT/s速率下。

RxStatus[2:0]

改信号用于指示PHY接收数据的状态,具体如下:

3‘b000:接收到的数据是OK的

3’b001:添加了一个SKP

3’b010:移除了一个SKP

3’b011:Tx检测到了对端的终端设备

3’b100:8b/10b或者128b/130b编码错误或者Disparity错误

3’b101:Elastic Buffer Overflow

3’b110:Elastic Buffer underflow

3’b111:Receive Disparity Error

PclkChangeOk

该信号高电平有效,仅仅用于PCLK作为PHY的输入模式下。当MAC要求改变PCLK的速率或者改变width的时候,PHY会拉高该信号。

参考书籍

- PHY Interface For the PCI Express, SATA, USB 3.1, DisplayPort, and Converged IO Architectures 5.2

- PCI Express® Base Specification Revision 5.0 Version 1.0

- PCI Express Technology Comprehensive Guide to Generations 1.x, 2.x, 3.0