FPGA设计时序约束十四、Set_External_Delay

一、序言

在时序约束中对clock的约束还存在一种特殊的延时约束set external delay。set external delay如字面含义,设置外部的时延值,但这个外部时延主要是指反馈时延,即信号从FPGA的output端口输出后经过外部电路回到输入端口的时延值。

二、Set External Delay

2.1 设置界面

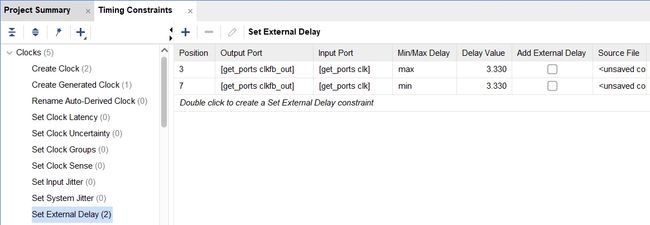

进入Timing Constraints界面,在左侧Clock栏中选中Set External Delay,右侧即显示Set External Delay

设置界面中需设置反馈路径中的输出端口output port和输入端口input port,delay value为设置的时延值。勾选“Specify min/max values”后可设置max和min,即指进行setup或hold分析,“Add to existing external delay”勾选后对于约束的端口如果存在其他的外部时延约束,则会将其覆盖。

2.2 命令语法

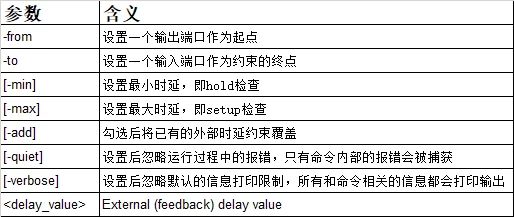

命令格式

set_external_delay ‑from ‑to [‑min] [‑max] [‑add] [‑quiet] [‑verbose] 参数含义

三、工程示例

3.1 工程代码

设计中以PLL的反馈时钟输入输出为例设置set_external_delay

module set_external_delay(d1,rst,clk,clkfb,clkfb_out,out);

output out;

input d1,rst;

input clk,clkfb;

output clkfb_out;

reg ff1,ff2;

wire feedback,clk1;

PLLE2_BASE #(

.BANDWIDTH("OPTIMIZED"), // OPTIMIZED, HIGH, LOW

.CLKFBOUT_MULT(5), // Multiply value for all CLKOUT, (2-64)

.CLKFBOUT_PHASE(0.0), // Phase offset in degrees of CLKFB, (-360.000-360.000).

.CLKIN1_PERIOD(0.0), // Input clock period in ns to ps resolution (i.e. 33.333 is 30 MHz).

// CLKOUT0_DIVIDE - CLKOUT5_DIVIDE: Divide amount for each CLKOUT (1-128)

.CLKOUT0_DIVIDE(1),

.CLKOUT1_DIVIDE(1),

.CLKOUT2_DIVIDE(1),

.CLKOUT3_DIVIDE(1),

.CLKOUT4_DIVIDE(1),

.CLKOUT5_DIVIDE(1),

// CLKOUT0_DUTY_CYCLE - CLKOUT5_DUTY_CYCLE: Duty cycle for each CLKOUT (0.001-0.999).

.CLKOUT0_DUTY_CYCLE(0.5),

.CLKOUT1_DUTY_CYCLE(0.5),

.CLKOUT2_DUTY_CYCLE(0.5),

.CLKOUT3_DUTY_CYCLE(0.5),

.CLKOUT4_DUTY_CYCLE(0.5),

.CLKOUT5_DUTY_CYCLE(0.5),

// CLKOUT0_PHASE - CLKOUT5_PHASE: Phase offset for each CLKOUT (-360.000-360.000).

.CLKOUT0_PHASE(0.0),

.CLKOUT1_PHASE(0.0),

.CLKOUT2_PHASE(0.0),

.CLKOUT3_PHASE(0.0),

.CLKOUT4_PHASE(0.0),

.CLKOUT5_PHASE(0.0),

.DIVCLK_DIVIDE(1), // Master division value, (1-56)

.REF_JITTER1(0.0), // Reference input jitter in UI, (0.000-0.999).

.STARTUP_WAIT("FALSE") // Delay DONE until PLL Locks, ("TRUE"/"FALSE")

)

PLLE2_BASE_inst (

// Clock Outputs: 1-bit (each) output: User configurable clock outputs

.CLKOUT0(), // 1-bit output: CLKOUT0

.CLKOUT1(clk1), // 1-bit output: CLKOUT1

.CLKOUT2(), // 1-bit output: CLKOUT2

.CLKOUT3(), // 1-bit output: CLKOUT3

.CLKOUT4(), // 1-bit output: CLKOUT4

.CLKOUT5(), // 1-bit output: CLKOUT5

// Feedback Clocks: 1-bit (each) output: Clock feedback ports

.CLKFBOUT(clkfb_out), // 1-bit output: Feedback clock

.LOCKED(LOCKED), // 1-bit output: LOCK

.CLKIN1(clk), // 1-bit input: Input clock

// Control Ports: 1-bit (each) input: PLL control ports

.PWRDWN(PWRDWN), // 1-bit input: Power-down

.RST(rst), // 1-bit input: Reset

// Feedback Clocks: 1-bit (each) input: Clock feedback ports

.CLKFBIN(clkfb) // 1-bit input: Feedback clock

);

always@(posedge clk1)

begin

if(!rst)

ff1<=1'b0;

else

ff1<=d1;

end

always@(posedge clk1)

begin

if(!rst)

ff2<=1'b0;

else

ff2<=ff1;

end

assign out=ff2;

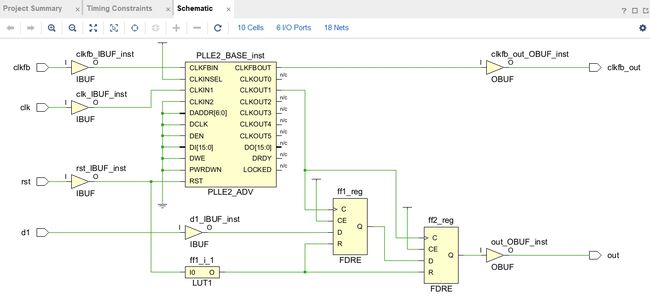

endmodule综合网表连接图如下图所示

输入输出引脚设置set_input_delay/set_output_delay,再是对PLL的反馈时钟输入端口和输出端口设置set_external_delay

create_clock -period 10.000 -name clk -waveform {0.000 5.000} [get_ports clk]

create_generated_clock -name clk1_gen -source [get_pins PLLE2_BASE_inst/CLKIN1] -divide_by 2 -add -master_clock clk [get_pins PLLE2_BASE_inst/CLKOUT1]

create_clock -period 6.000 -name clkfb -waveform {1.000 3.000} [get_ports clkfb]

set_input_delay -clock [get_clocks clkfb] 2.220 [get_ports d1]

set_output_delay -clock [get_clocks -of_objects [get_pins PLLE2_BASE_inst/CLKFBOUT]] 1.110 [get_ports clkfb_out]

set_external_delay -from [get_ports clkfb_out] -to [get_ports clkfb] -min 1.3303.3 时序报告

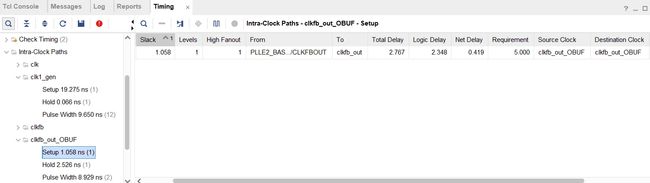

查看时序报告结果,会查找不到设置的约束值,因为该反馈路径时延值需在有外部逻辑时才会进行分析

四、参考资料

用户手册:ug903-vivado-using-constraints-en-us-2022.2.pdf

链接:https://pan.baidu.com/s/17AK_-J4wRXiFLtLTorlrwg?pwd=mylt

提取码:mylt