Xilinx DMA的几种方式与架构

DMA是direct memory access,在FPGA系统中,常用的几种DMA需求:

1、 在PL内部无PS(CPU这里统一称为PS)持续干预搬移数据,常见的接口形态为AXIS与AXI,AXI与AXI;

2、 从PL与PS之间搬移数据,对于ZYNQ就比较好理解,属于单个芯片内部接口,对于PCIe等其它接口,会稍微复杂一些,属于多个芯片之间的接口;

探索DMA 方式的目的:

1、 了解芯片内部数据搬移的方法,DMA的常用接口、实现方式;

2、 了解芯片之间的数据搬移方法,DMA常用接口、实现方式;

通过这些了解,可以建立一个系统数据搬移的框架结构,那么出现类似的需求,实际上就只要做的就是调用已有的模块去实现它。

本文从Xilinx的各个DMA IP着手介绍,主要从接口的角度来着眼。

1 AXI4 TO AXI4

1.1 AXI Central DMA Controller

The AXI CDMA provides high-bandwidth Direct Memory Access (DMA) between a memory-mapped source address and a memory-mapped destination address using the AXI4 protocol. An optional Scatter Gather (SG) feature can be used to offload control and sequencing tasks from the system CPU. Initialization, status, and control registers are accessed through an AXI4-Lite slave interface, suitable for the Xilinx MicroBlaze™ processor.

为啥叫CDMA,实际上是为了处理CPU挂载的AXI 接口内存内部的数据传输,典型的场景是MicroBlaze,为啥不说ZYNQ呢?ZYNQ的AXI 内部是直接挂载在CPU内部的,不需要一个DMA去控制,需要的话直接软件copy,copy的动作就会内部发起一次AXI DMA的操作。但是如果ZYNQ想要用PL侧的DDR,那么就得用CDMA去操作,因为ZYNQ没有AXI Master的接口,只有SLAVE(这里说的都是高性能HP接口,不是GP低速接口)。

图 1‑1 AXI CDMA接口与参数选项,其中S_AXI_LITE连接到主控CPU,M_AXI连接到存储器,M_AXI_SG连接到存储器(用于存储SG DMA模式下的dma descriptor)

图 1‑2 CMDA内部结构框图

图 1‑3 ZYNQ框图,只有高性能的AXI SLAVE,没有MASTER

我们来看看内部寄存器,这个实际上更加直观,告诉了用户使用该模块的配置方法,从配置方法可以简单估计使用该模块的复杂程度。从寄存器定义来看,控制、状态检测,SG DMA的descriptor指针,简单DMA的起始地址,目标地址,长度,使用起来并不复杂。那么对应的软件代码建议直接copy xilinx的ZYNQ侧driver代码,然后自己稍微改一改就可以用起来。

最后再来看看资源占用情况,资源占用与位宽成正比,典型的在64bit数据位宽下,占用大约1500个LUT,2500个FF,从我的角度看,这个资源相当不错。

图 1‑4 资源占用

图 1‑5 传输效率、带宽

2 AXI Stream to AXI4

2.1 AXI DataMover

The AXI Datamover is a key Interconnect Infrastructure IP which enables high throughput transfer of data between AXI4 memory mapped domain to AXI4-Stream domain. The AXI Datamover provides MM2S and S2MM AXI4-Stream channel which operate independently in a full duplex like method. The AXI Datamover is a key building block for the AXI DMA core and enables 4 kbyte address boundary protection, automatic burst partitioning, as well as providing the ability to queue multiple transfer requests using nearly the full bandwidth capabilities of the AXI4-Stream protocol. Furthermore, the AXI Datamover provides byte-level data realignment allowing memory reads and writes to any byte offset location.

AXI Datamover是一个重要的基础IP,Xilinx 所有的DMA IP基本都包含这个模块,该模块可以将AXIS与AXI格式的数据进行转换。

类似XDMA,VDMA, AXI DMA, AXI MCDMA等几乎所有DMA IP均包含该模块,如果xilinx的这些已有DMA不能满足需求,那么用户就可以自行设计1各DMA控制器完成DMA操作。

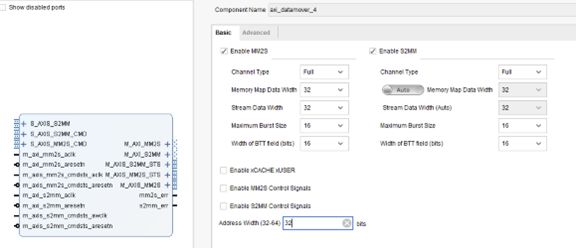

图 2‑1 AXI Datamover 接口与配置项

图 2‑2 MM2S读数据通道,读取AXI4接口数据,转换成AXIS数据输出

图 2‑3 S2MM写数据通道, AXIS数据输入,转换成AXI4数据写到到AXI4接口存储器

图 2‑4 资源占用

2.2 AXI DMA Controller

The AXI Direct Memory Access (AXI DMA) IP provides high-bandwidth direct memory access between memory and AXI4-Stream-type target peripherals. Its optional scatter gather capabilities also offload data movement tasks from the Central Processing Unit (CPU) in processor based systems. Initialization, status, and management registers are accessed through an AXI4-Lite slave interface.

简而言之,AXI DMA Controller为AXIS和AXI4接口的转换(数据存储)提供了一个可由软件控制(通过AXI Lite接口实现)的简单方式。

图 2‑5 AXI DMA内部框图

这里需要说明一下:如果选择不使能SG DMA模式,而是单纯的寄存器控制模式,对于AXI DMA这个IP来说,资源占用会减少,性能会降低(Xilinx其它的DMA IP也是类似的),为什么性能会降低呢?这是因为寄存器模式不支持预先设定传输指令,只能等一次传输结束后开启下一次传输,这就降低了带宽,增加了CPU的干预。不过这种模式也最为简单,还是要看设计中的传输要求。

我们来看一眼寄存器表格,表格列出了SG DMA和寄存器DMA 2种方式下的寄存器,从表中可以看出,要实际使用AXI DMA并不复杂,不过我还是建议直接抄Xilinx SDK的驱动代码,裸机驱动、example就可以,简单直接、易用。

图 2‑6 表中给出了SG模式和寄存器模式下的相关寄存器及其含义

图 2‑7 资源占用上来看,还是不少的

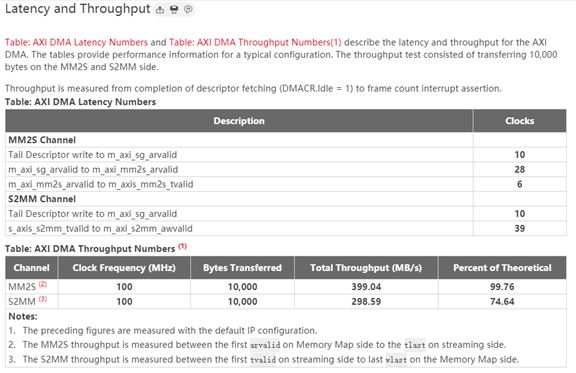

图 2‑8 延迟、性能、带宽数据,带宽数据还不错,一般来说能做到80%是很好的,读比写快,因此MM2S的带宽接近100%,S2MM只有75%

2.3 AXI Multichannel DMA

简单来说,就是AXI DMA的多通道版本,是为了应对多通道、低速的数据传输,AXI MCDMA最多支持双向各16通道,且各个通道间相互独立,允许单独配置,这个给很多低速、多功能的应用提供了一个小面积FPGA的解决方案。

由于AXI MCDMA是AXI DMA的多通道版本,因此不做过多介绍。

The AXI MCDMA facilitates large data migration, offloading the task from the embedded processor. It sits as an intermediary between an AXI Memory-Mapped embedded subsystem an AXI Streaming subsystem. The MCDMA IP is full-duplex, scatter-gather, and supports up to 16 channels. It may be configured as weighted round robin or strict priority

图 2‑9 AXI MCDMA结构框图

2.4 AXI Video DMA

The AXI Video Direct Memory Access (AXI VDMA) core is a soft Xilinx IP core that provides high-bandwidth direct memory access between memory and AXI4-Stream type video target peripherals. The core provides efficient two dimensional DMA operations with independent asynchronous read and write channel operation. Initialization, status, interrupt and management registers are accessed through an AXI4-Lite slave interface.

为什么有了AXI DMA还要由AXI VDMA呢?从下面这段话可以看出原因,Xilinx的video处理,多用AXIS格式,而实际应用中很多需要改变帧速率、缓存帧的需求,直接用AXI DMA不是不可以,只是不能很好的和其它AXIS接口的Video IP匹配,因此专门开发了AXI VDMA,主要是为了缓存图像帧,有朋友要问,不能用BRAM缓存嘛?不能,因为图像对应的1各frame可能很大,用BRAM资源不够。

AXI VDMA的使用方式与其它DMA IP大同小异,这里不做更多介绍,要用的可以直接查看官方手册。

3 PCIe DMA

Xilinx 为PCIe接口也推出了AXI DMA接口,对应为Xilinx DMA for PCIe,同理,类似USB, SRIO等其它接口,用户也可以设计出类似的DMA解决方案,构建高可靠、灵活的系统内部架构。

The Xilinx® LogiCORE™ DMA for PCI Express® (PCIe) implements a high performance, configurable Scatter Gather DMA for use with the PCI Express Integrated Block. The IP provides an optional AXI4-MM or AXI4-Stream user interface

图 3‑1 XDMA接口与参数配置项

图 3‑2 XDMA内部框图

那么XDMA可以做什么事情呢?那可多了,有了这个模块,你的PCIe Endpoint设备就可以构建在AXI总线的基础之上,就有了1个灵活、可靠、高性能的片上系统架构。

4 启发

用户可以根据Xilinx DMA的框图架构,在AXI, AXIS接口的互联下,构建灵活可靠的FPGA系统,如果这些IP无法满足要求,还可以模仿PCIe XDMA等IP的架构方式,搭建属于自己的片上系统架构。