XXB作业复习第五弹

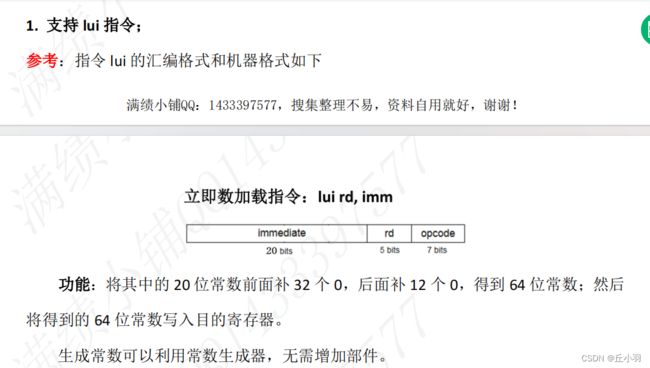

lui指令的作用是将立即数写入寄存器的前二十位,然后将后十二位补0,将其扩展为64位。

lui指令的作用是将立即数写入寄存器的前二十位,然后将后十二位补0,将其扩展为64位。

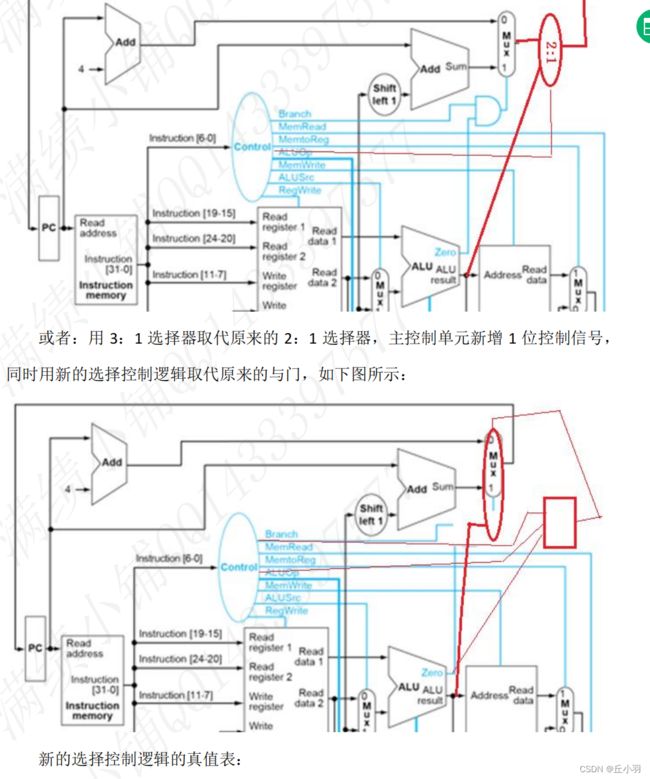

为此需要将写入目的寄存器源增加一个2:1选择器,同时主控制单元为其增加一个选择控制信号。

当然也可以用3:1选择器取代原来的2:1选择器,主控制单元用2位选择控制信号取代原来的1位控制信号。注意:选择器中不能有两个控制信号。

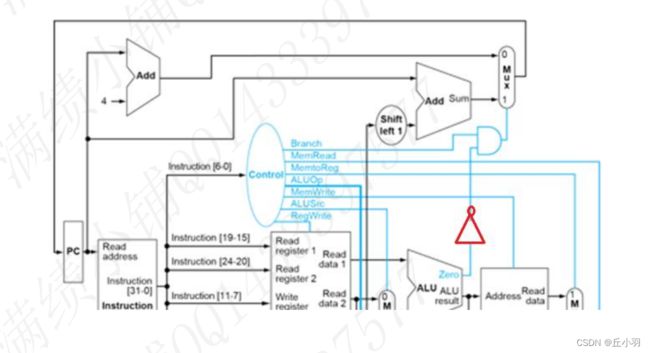

在ALU的zero输出端增加一个反相器(非门):

方案一:同时保存bne指令的功能和beq指令的功能。增加额外的分支,即zero信号额外分支出一个进入反相器作为输入,而与之共同构成选择信号(同时进入与门的)的控制信号是新增的控制信号。经beq选择器后进入bne选择器。

方案二:两个控制信号经处理后变成一个新的控制信号,逻辑门的输入包括branch控制信号,新增的控制信号和zero信号。输出作为选择控制信号输入。选择地址。

很显然,beq指令和bne指令只是zero信号的输入不同,可以增加一个控制信号,来决定是选择zero信号,还是zero经过反相器之后的信号作为输入。

很显然,beq指令和bne指令只是zero信号的输入不同,可以增加一个控制信号,来决定是选择zero信号,还是zero经过反相器之后的信号作为输入。

立即数进行扩展在ImmGen就已经实现,所以不用加入进行立即数扩展的部件,注意:不用往立即数生成器(IMmGen)里面加入控制信号,他自己不用接受控制信号就知道要怎么办。

立即数进行扩展在ImmGen就已经实现,所以不用加入进行立即数扩展的部件,注意:不用往立即数生成器(IMmGen)里面加入控制信号,他自己不用接受控制信号就知道要怎么办。

要在地址选择器中更换控制限号,对jal控制信号和(branch信号与zero信号的输出)输入逻辑门。

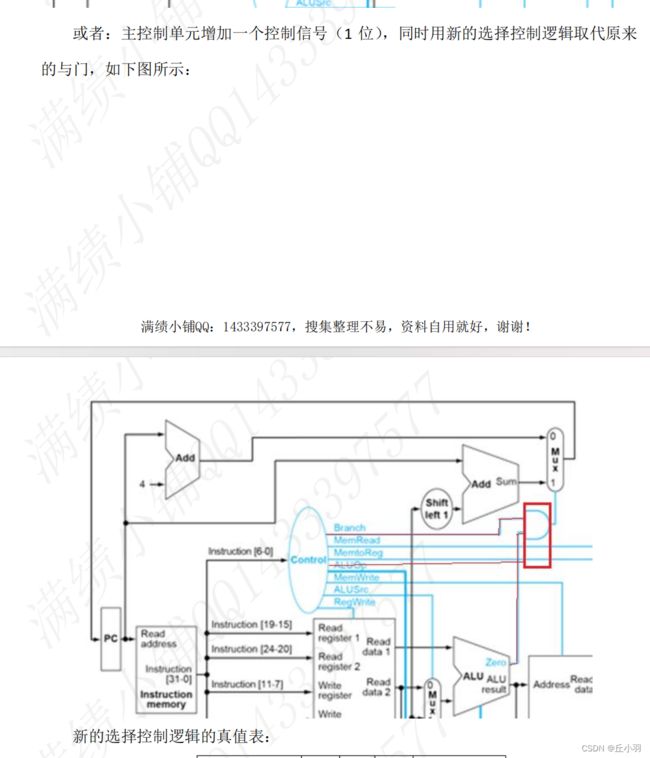

最好写上新的选择控制逻辑的真值表:

或者为写PC时的地址源增加一个2:1选择器,同时主控制单元增加一个2:1选择控制信号。

值得注意的是:这里的rd被赋值为PC+4,这是独一无二的,所以往写入目的寄存器的数据源增加一个2:1选择器,同时主控制单元为其增加一个2:1选择控制信号。

值得注意的是:这里的rd被赋值为PC+4,这是独一无二的,所以往写入目的寄存器的数据源增加一个2:1选择器,同时主控制单元为其增加一个2:1选择控制信号。

当然也可以在原写入目的寄存器数据源选择器里面增加一个输入,主控制单元用两位选择信号取代原来的一位选择控制信号。即对MemtoReg信号进行扩展。

总的来说要加两个选择控制信号或者加一个并对MemtoReg信号进行扩展。

支持jalr指令,立即数扩展不用管他,IMmGen会自己解决的。修改PC的方法和jal相同,有用的方法是在原本的PC选择器的输出后连接一个新的选择器,另一个输入是64位偏移量和源寄存器1的内容相加得到的目标地址。所以要新加一个2:1控制信号。写入目的寄存器源的输入增加一个PC+4,对MenToReg信号进行扩展,由一位扩展为两位。

新的指令,当然要有新的控制信号了,在ALU的输出ALU Result后加一个加法器,另一个输入是rs2,即寄存器堆的输出Read data2,输出与原ALU Result进入2:1选择器,增加一个2:1选择控制信号选择输出,进入数据存储器的Address。

新的指令,当然要有新的控制信号了,在ALU的输出ALU Result后加一个加法器,另一个输入是rs2,即寄存器堆的输出Read data2,输出与原ALU Result进入2:1选择器,增加一个2:1选择控制信号选择输出,进入数据存储器的Address。

当然我觉得也可以修改ALU的内部结构,同时修改ALUOP控制信号。(不可以,有结构显示,rs2和imm只能有一个进入ALU)。

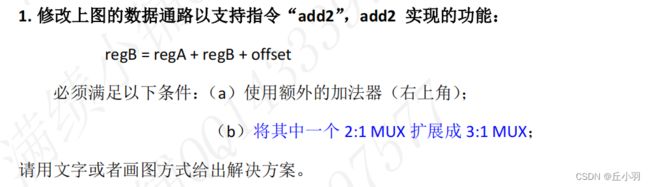

将ALU的输出和B(即rs2)共同作为输入进入一个额外加法器,输出作为写入目的寄存器源的一个输入,将写入目的寄存器控制信号扩展为两位,扩展为3:1MUX。

将ALU的输出和B(即rs2)共同作为输入进入一个额外加法器,输出作为写入目的寄存器源的一个输入,将写入目的寄存器控制信号扩展为两位,扩展为3:1MUX。

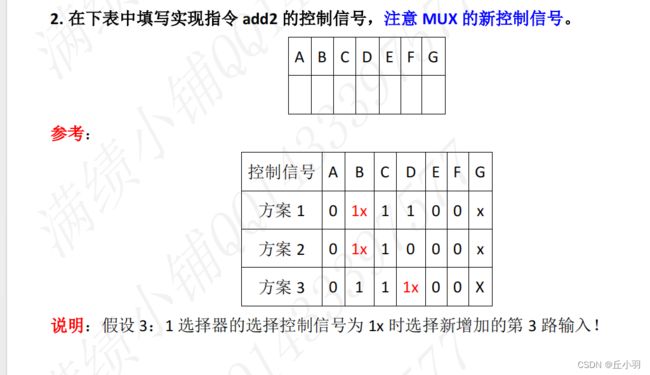

我们采用的是方案1,选择rs1+rs2是ALU的结果,所以A是0,B是1x(选择加法器的输出作为写入目的寄存器的输入),RF正常工作啊,C=1,D=1,选择下面的控制信号,E=0,做加法运算,F=0,正常工作其实不必要,G随便了,反正数据存储器是否正常工作都无所谓了。

我们采用的是方案1,选择rs1+rs2是ALU的结果,所以A是0,B是1x(选择加法器的输出作为写入目的寄存器的输入),RF正常工作啊,C=1,D=1,选择下面的控制信号,E=0,做加法运算,F=0,正常工作其实不必要,G随便了,反正数据存储器是否正常工作都无所谓了。

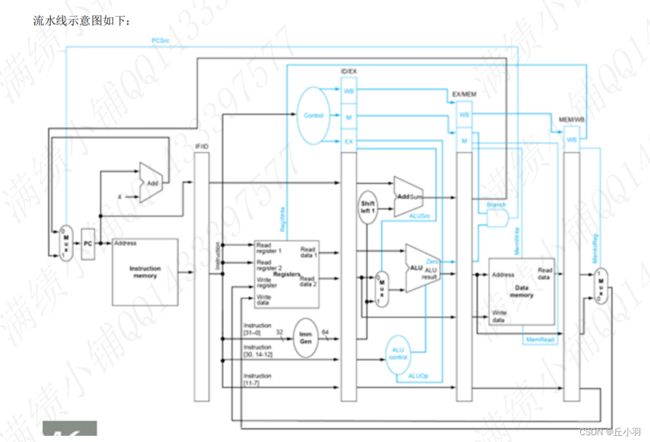

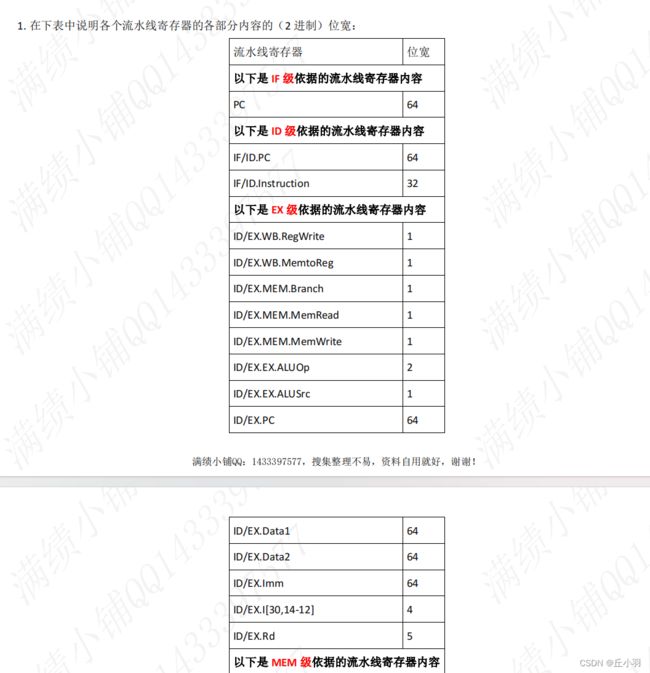

首先,第一条指令的地址是16*4=64位,所以PC的位宽是64位,指令的长度肯定是32位无疑了。控制信号的位宽肯定是1,而ALUOP的控制信号肯定是2,ID/EX.Data1,ID/EX.Data2的位宽一定是64。ID/EX.Rd一定是5位。

首先,第一条指令的地址是16*4=64位,所以PC的位宽是64位,指令的长度肯定是32位无疑了。控制信号的位宽肯定是1,而ALUOP的控制信号肯定是2,ID/EX.Data1,ID/EX.Data2的位宽一定是64。ID/EX.Rd一定是5位。

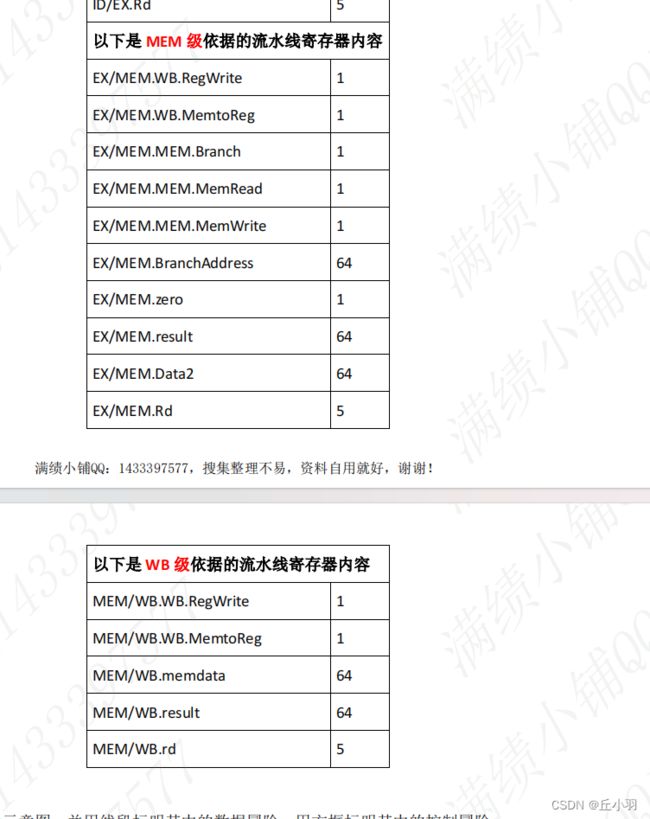

同理控制信号一位,地址64位,Data的运算结果作为result,而Data是64位,所以result是64位。

同理控制信号一位,地址64位,Data的运算结果作为result,而Data是64位,所以result是64位。

可以这样记:所有的data都是64位,所有的rd都是5位。明显rs1,rs2也是五位。

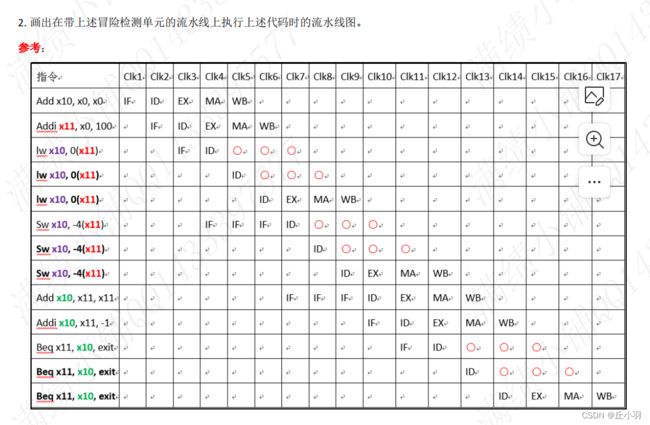

没有任何冒险处理机制。没有任何冒险处理机制的情况下,一个指令的WB阶段对应与之产生冒险的另一个指令的ID阶段,前半周期写后半周期读。或者说,在没有冒险处理机制的情况下,设a和b之间存在冒险,使用阻塞使a的WB阶段的同一时钟周期是b的ID阶段,这样就能消除冒险。???或者说加入阻塞,使任意三个周期内不存在冒险即可,或任一条指令后面两条指令不与这条指令存在冒险。

没有任何冒险处理机制。没有任何冒险处理机制的情况下,一个指令的WB阶段对应与之产生冒险的另一个指令的ID阶段,前半周期写后半周期读。或者说,在没有冒险处理机制的情况下,设a和b之间存在冒险,使用阻塞使a的WB阶段的同一时钟周期是b的ID阶段,这样就能消除冒险。???或者说加入阻塞,使任意三个周期内不存在冒险即可,或任一条指令后面两条指令不与这条指令存在冒险。

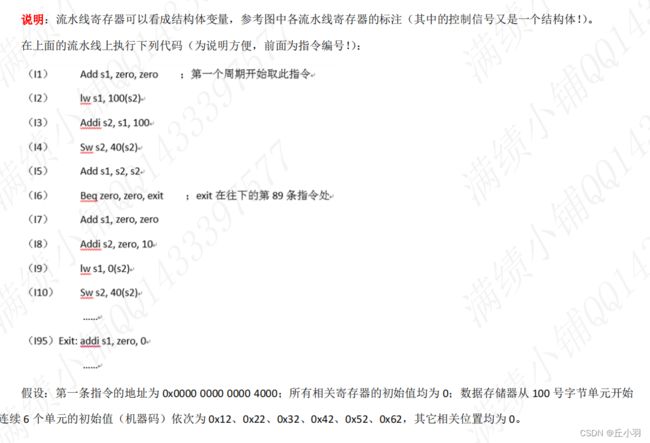

第一个指令的写入目的寄存器是s1,第二个写入目的寄存器也是s1,第三条指令要用s1作为输入,与上条指令之间存在数据冒险,这时有用的方法是在lw指令后面加两个阻塞。第三条指令的写入目的寄存器是s2,第四条指令需要用到s2作为计算地址的寄存器源,这时存在冒险,有用的方法是在addi指令后面加两条阻塞。add s1,s2,s2与上上条指令之间存在冒险,已在addi指令后面加入两个阻塞。已经不需要再加阻塞。beq后面的指令add,addi,lw是误入流水线的指令,但是在没有任何冒险处理机制的情况下还需要执行。目标地址在beq指令的WB取。即在没有任何冒险处理机制的情况下有三条误入流水线的指令。

在内存地址是100的地方连续6个字节单元的内容是12,22,32,42,52,62,0x省略,采用小端模式。

lw是取字,一个字是4个字节,所以取4个字节单元的内容,分别是:12,22,32,42。采用小端模式得到s1是0x0000 0000 4232 2212。因为是有符号扩展,符号位是0,进行扩展之后,前面都用0进行补齐。

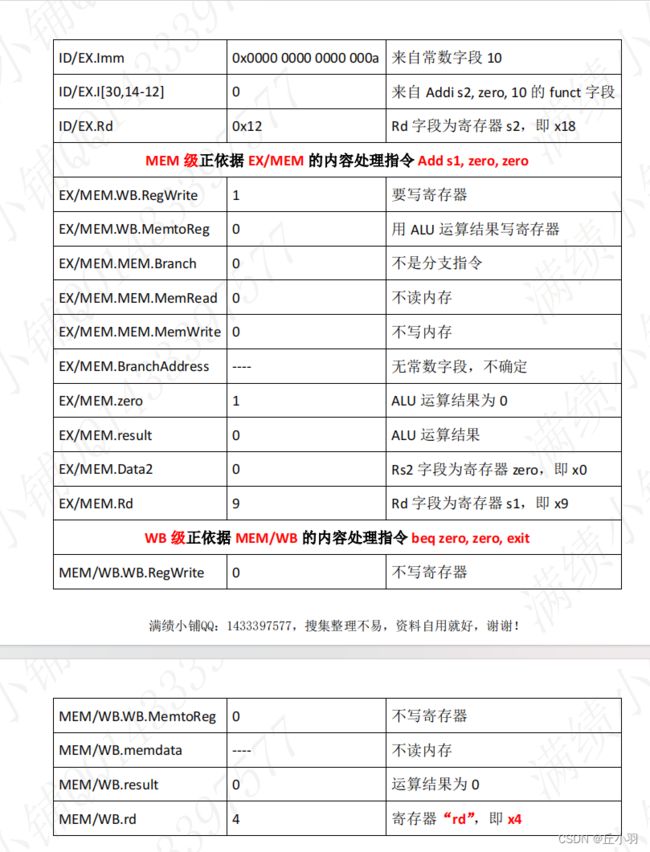

第一条指令的地址是0x4010,第五条指令的地址是0x4020,相比第一条指令加4*4=16=0x1 0000。IF/ID.Instruction表示的是机器码。R类型指令的ALUOP=2。注意imm可不是机器码了,imm是机器码经过64为扩展得到的,至于这么扩展,无常数字段,不好说。所以不确定。BranchAddress同理。zero虽然没用,但是经过ALU(并不一定是减法计算,看操作码)计算了,得到的确实是0,所以zero=1。

第一条指令的地址是0x4010,第五条指令的地址是0x4020,相比第一条指令加4*4=16=0x1 0000。IF/ID.Instruction表示的是机器码。R类型指令的ALUOP=2。注意imm可不是机器码了,imm是机器码经过64为扩展得到的,至于这么扩展,无常数字段,不好说。所以不确定。BranchAddress同理。zero虽然没用,但是经过ALU(并不一定是减法计算,看操作码)计算了,得到的确实是0,所以zero=1。

为什么寄存器s1的编号是9啊?

以以上表格形式说明第五个时钟周期各流水线寄存器的状态:

加载存储类型指令,ALUop=0。

lw指令也会计算出分支地址,但是是作为取数据的地址使用的。

lw指令也会计算出分支地址,但是是作为取数据的地址使用的。 加载存储类指令的ALUOP=0。注意I型指令(包括addi)的ALUSrc=1。imm表示立即数字段进行有符号扩展。

加载存储类指令的ALUOP=0。注意I型指令(包括addi)的ALUSrc=1。imm表示立即数字段进行有符号扩展。

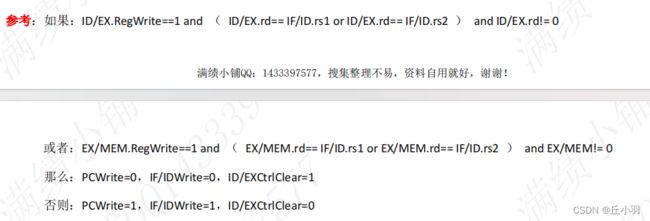

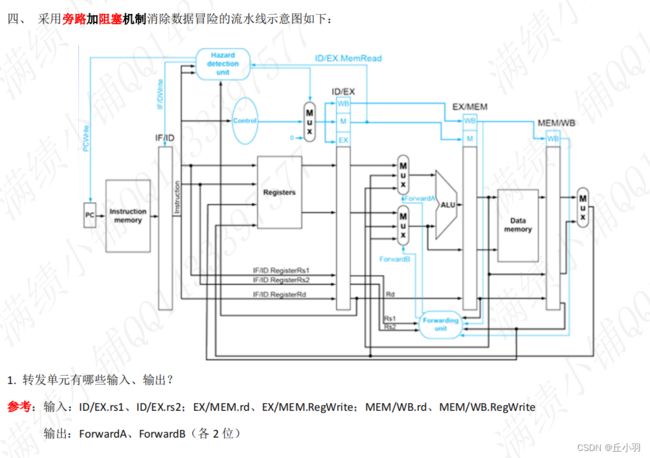

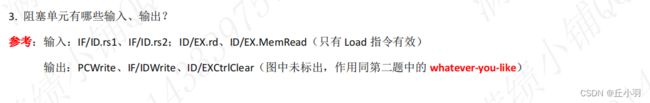

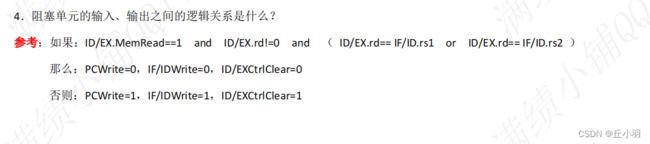

能越早检测越好,所以安排在ID级,需要阻塞的时候阻塞的是后面的指令,故采用向前检测,在ID级判断当前指令与上条指令和上上条指令之间是否存在数据冒险。

检测到冒险时,要做哪些事,为此需要引入 哪些控制信号?

检测到冒险时,阻止修改PC和IF/ID;ID/EX里的控制信号清零。为此,引入:

PCWrite,为0时阻止修改PC;为1时允许修改PC。

IF/IDWrite,为0时阻止修改IF/ID;为1是允许修改IF/ID。

ID/EXClearUp,为1时将ID/EX里面的控制信号清零,为0时正常。

注意:这三个信号都是配合使用,配合的结果是110或001。

ID阶段的rs1,rs2。EX和MEM阶段的rd和RegWrite。

利用冒险检测单元的输入输出写出冒险检测单元的控制逻辑。

ID阶段进行检测,存在冒险就是001,不存在冒险就是110。

会不会误阻塞?举例说明误阻塞的原因,会影响流水线正常工作吗?如果想要消除误阻塞,如何改进?

会,目前的检测单元没有判断当前指令是否真的需要读rs1或者rs2,实际上有些指令根本就没有rs2字段,即使它们在ID级抢先读了rs1或rs2,那也是白读,读出的内容根本用不到。

例如:addi x10,x11,-10的机器指令中的“rs2”字段是22,如果上条指令或者上上条指令要写寄存器x22,就会引起阻塞。

误阻塞会浪费时间,但不会影响流水线正常工作。

改进:增加检测单元的输入,借以判断当前指令是否真正要读rs1或者rs2。

总结:目前的检测单元利用RegWrite对上条指令或上上条指令是否真正需要写rd做了判断,但是没有对当前指令是否真正需要读rs1或rs2进行判断。

不带任何冒险处理机制的流水线上,画出数据冒险是连接两个冒险指令,前者的WB阶段,后者的ID阶段。

不带任何冒险处理机制的流水线上,画出数据冒险是连接两个冒险指令,前者的WB阶段,后者的ID阶段。

利用阻塞来消除冒险:两个阻塞的指令之间至少需要有两个阻塞单元。而根据题设,在EX及其后面的阶段,信号就已经清零,所以流水线图中不显示被阻塞指令的EX,MEM,WB阶段。

在lw的ID阶段判断地址不再更新,但是在IF阶段就已经实现了PC+4,在ID阶段就已经取sw的指令,使地址不再更新,也就是下一时钟周期继续取sw指令。

clk3的EX阶段的rs2是4:100的后五位是4。

clk3的EX阶段的rs2是4:100的后五位是4。

显然,在clk4的ID阶段是lw x10,0(x11),从图中可以看出来,这一指令是被阻塞的。所以在ID阶段的输出是000。

sd rs2 rd(rs1)要格外注意sd指令的rs1和rs2还有rd。

注意这个exit里面的4,exit可以看做是89*4,后5位是4。....(迷迷糊糊,为什么不是半字偏移量了)难不成是看指令格式?

采用旁路加阻塞机制消除数据冒险。

转发单元的输入还是不变的,输出变成了ForwardA和ForwardB。为0时表示从当前寄存器中读出的内容,为1时表示从EX到EX旁路转发过来的内容,为2时表示从MEM到EX旁路转发过来的内容。

但是显然这样是不够的,如果load指令与下一条指令之间存在数据冒险,不能从load的EX阶段到下一条指令的EX阶段之间建立旁路,load指令的MEM阶段才能取到数据。所以需要阻塞单元。但是阻塞单元不需要输入上上条指令的rd和regwrite,load的MEM阶段对应下下条指令ID阶段,所以能够利用从MEM到EX的旁路。

注意:会误转发,而且会误阻塞,原因:转发单元和阻塞单元并未判断当前指令是否真正需要用到rs1和rs2寄存器的内容,此时误转发做无用功,可能会影响流水线的工作。误阻塞浪费一个周期的时间,但不会影响流水线的工作。

注意:会误转发,而且会误阻塞,原因:转发单元和阻塞单元并未判断当前指令是否真正需要用到rs1和rs2寄存器的内容,此时误转发做无用功,可能会影响流水线的工作。误阻塞浪费一个周期的时间,但不会影响流水线的工作。

sw的阻塞过程:在第一次执行sw时,在ID阶段判断上条指令是load指令,并且与sw指令之间存在数据冒险,所以阻塞。

sw的阻塞过程:在第一次执行sw时,在ID阶段判断上条指令是load指令,并且与sw指令之间存在数据冒险,所以阻塞。

不过MEM到MEM的旁路只能在load指令和store指令之间实现。

不过MEM到MEM的旁路只能在load指令和store指令之间实现。

在被阻塞的指令的ID阶段是clk5,阻塞控制单元的输出是000。也就是说clk5周期ID阶段的输出是000(阻塞控制单元在ID阶段进行输出)。

在被阻塞的指令的ID阶段是clk5,阻塞控制单元的输出是000。也就是说clk5周期ID阶段的输出是000(阻塞控制单元在ID阶段进行输出)。

Forward对应的是EX阶段,ForwardA对应的是在该周期,处于EX阶段指令的rs1。注意,在clk6周期,要按输入输出信号逻辑进行填写。

Forward对应的是EX阶段,ForwardA对应的是在该周期,处于EX阶段指令的rs1。注意,在clk6周期,要按输入输出信号逻辑进行填写。