CAN的填充机制解释及其延伸知识

我们都知道CAN的填充机制是从SOF-CRC段内,每遇到5个相同极性位时便填充一位相反极性位。(CANfd也是同样的填充机制)。如下图所示。

我在学习和工作中发现,一些同事和技术人员只知道CAN的位填充机制,却对为何CAN会采用位填充,不明所以。

位填充不是无意义的,任何一种协议中的任何一种方法都是有其特殊的功能的。不然使用位填充的方法,即增加了数据冗成,又使得软硬件的设计变得复杂化。下面介绍位填充的两种意义。

一:避免与CAN错误帧冲突

二:位填充是与位同步机制相配合的

三:实现透明传输(后面不展开说了,最多的一条应用是帧接收界定符是7bit隐性电平,填充机制=避免了在数据传输过程中,被误认为是帧结束界定符)

注意:童鞋们有些认为是,数据链路层以上发出来的数据是 5bit相同+然后数据链路层填充1bit,然后再判断下5bit是不是相同极性。仔细观察上图中我打标记的地方。其实是下一判断周期中已经把填充位也计算进去了。这点需要注意。

一:避免与CAN错误帧冲突

CAN协议的错误帧分为主动错误帧和被动错误帧:具体格式如下

主动错误帧: 6bit 显性+8bit隐形错误界定符

被动错误帧:6bit 隐形+8bit隐形错误界定符

有童鞋会问为什么会产生错误叠加部分,这里原因有点复杂,有时间会另外写一份文章来单独讲。

如有兴趣可以查阅其他同仁的资料freshcoolman的博客_CSDN博客-c语言,AUTOSAR,Python领域博主

CAN协议采用填充位机制,就是为了避免与错误帧处理机制起冲突。如果不采用位填充机制,如果CAN帧数据段发送 0x00或0xFF,就会产生连续6位显性位或显性位。会产生异常错误。

二:CAN特殊的位同步机制

时序同步在通信中的重要性不言而喻。SPI总线、I2C总线是通过单独的时钟线实现同步,LIN总线、以太网是通过帧结构专门的同步段实现同步。

CAN即没有专门的时钟线,帧结构上也没有专门用于同步的段,CAN是如何实现同步的?就不得不提CAN比较特殊的位同步机制:位同步机制!!!

位同步基础知识

CAN总线的位同步,1:硬件同步 2:再同步

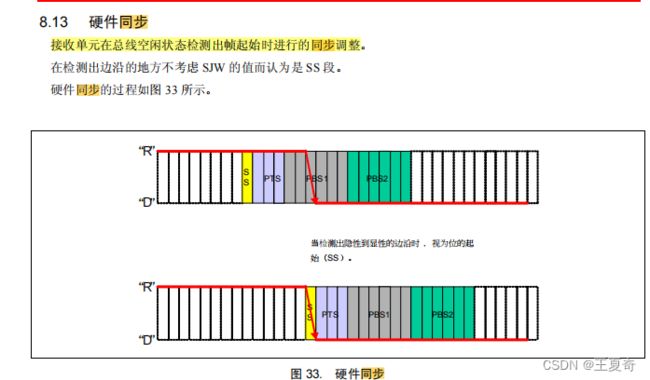

1:硬件同步:比较好理解

需要注意的是硬同步实现的前提:接收单元在总线空闲状态检测出帧起始时进行的同步调整

1:总线需进入空闲状态

2:空闲状态后,需接受到一个隐形到显性的跳变(可以理解为帧的SOF)

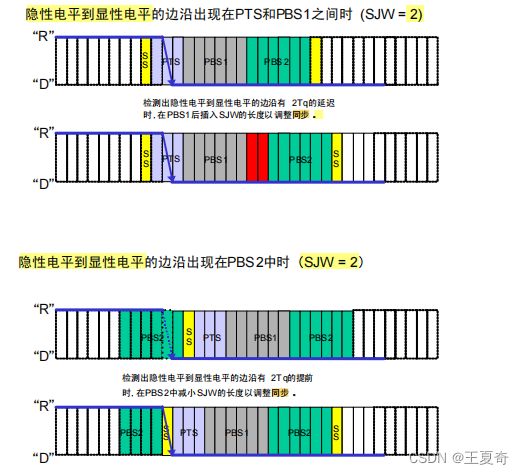

2:再同步

再同步是硬件同步的补充,节点A和B自身的位时序出现了偏差,已经通过硬件同步实现同步了,后续仲裁段+控制段+数据段等如何实现同步?就需要使用到再同步技术

以下是资料中对再同步的描述

回到我们最初的问题,填充机制是如何配合再同步的?

发现没有,再同步实现的方法有一个必要条件,就是总线电平发送跳变,电平跳变就意味着数据发生改变(描述不是很准确,为了理解方便)。当节点A发送0x331 {00,00,00,00,00,00,00,00},数据段全0,给节点B,数据段是不是全部为显形电压,节点B就无法提供电平跳变实现与A的同步。

引入位填充机制后,数据段00发送过程中,节点A每发送5bit显性电平后,插入一位隐性电平。这个电平的跳变使得B可以与A再次实现位同步。