vivado 在非项目模式下使用源、读取各种源文件的非项目模式脚本示例

在非项目模式下使用源

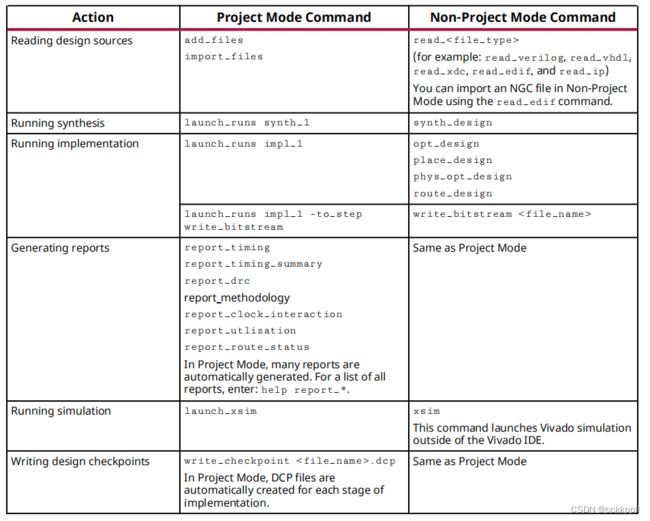

与为您管理源文件的项目模式不同,源文件位于非项目模式下的控制。使用Tcl命令,可以指定要处理和输出的文件要生成的文件,包括网表、位流和报告文件。表1:项目模式和非项目模式命令显示了常用的项目模式命令和相应的非项目模式命令。有关项目模式和非项目模式的更多信息,请参阅Vivado Design Suite用户指南:设计流程概述(UG892)中的此链接。了解更多有关Tcl命令的信息,请参阅Vivado Design Suite Tcl命令参考指南(UG835)。注意:在非项目模式下,文件是按照read_*命令在Tcl中列出的顺序编译的剧本注意:要在当前安装中选择新零件,请关闭当前项目并升级当前安装以添加附加部件。

以下是读取各种源文件的非项目模式脚本示例:

# create_bft_batch.tcl

# bft sample design

# A Vivado script that demonstrates a very simple RTL-to-bitstream batch

flow

#

# NOTE: typical usage would be "vivado -mode tcl -source

create_bft_batch.tcl"

#

# STEP#0: define output directory area.

#

set outputDir ./Tutorial_Created_Data/bft_output

file mkdir $outputDir

#

# STEP#1: setup design sources and constraints

#

read_vhdl -library bftLib [ glob ./Sources/hdl/bftLib/*.vhdl ]

read_vhdl ./Sources/hdl/bft.vhdl

read_verilog [ glob ./Sources/hdl/*.v ]

read_xdc ./Sources/bft_full.xdc

#

# STEP#2: run synthesis, report utilization and timing estimates, write

checkpoint

design

#

synth_design -top bft -part xc7k70tfbg484-2 -flatten rebuilt

write_checkpoint -force $outputDir/post_synth

report_timing_summary -file $outputDir/post_synth_timing_summary.rpt

report_power -file $outputDir/post_synth_power.rpt

#

# STEP#3: run placement and logic optimzation, check against the UltraFast

methodology checks, report utilization and timing estimates, write

checkpoint design

#

opt_design

report_methodology -file $outputDir/post_opt_methodology.rpt

place_design

phys_opt_design

write_checkpoint -force $outputDir/post_place

report_timing_summary -file $outputDir/post_place_timing_summary.rpt

#

# STEP#4: run router, report actual utilization and timing, write

checkpoint design,

run drc, write verilog and xdc out

#

route_design

write_checkpoint -force $outputDir/post_route

report_timing_summary -file $outputDir/post_route_timing_summary.rpt

report_timing -sort_by group -max_paths 100 -path_type summary -file

$outputDir/post_route_timing.rpt

report_clock_utilization -file $outputDir/clock_util.rpt

report_utilization -file $outputDir/post_route_util.rpt

report_power -file $outputDir/post_route_power.rpt

report_drc -file $outputDir/post_imp_drc.rpt

write_verilog -force $outputDir/bft_impl_netlist.v

write_xdc -no_fixed_only -force $outputDir/bft_impl.xdc

#

# STEP#5: generate a bitstream

#

write_bitstream -force $outputDir/bft.bit