数字IC芯片设计实现 | 时序Timing Signoff check_timing检查解析

今天分享在数字IC芯片设计实现做timing signoff阶段必须要看的report。check_timing的报告必须是clean的,否则芯片回来大概率是废片!!!实际上一堆公司的芯片败在不看这个report了。

我们知道primetime(简称PT)做时序检查是基于我们给定的signoff sdc时序约束。所以timing结果的准确性就取决于sdc的完备性。如果sdc有漏洞,自然这个timing结果就不可信。但好在PT会报出当前设计sdc可能存在的问题。

所以我们在跑完pt必须带上check_timing检查下sdc的完备性。如果sdc有问题,工具会报出如下图所示的警告!记住每个警告都必须review一遍。如果认为是假的或无关紧要,请签字画押!

如果是用的cadence的tempus工具检查timing,也会报出类型的警告信息。原理是一样的,只不过叫法可能不太一样。

PT check_timing主要检查以下这些item。

● generated_clocks

检查generated_clocks的定义是否合理,有没有源时钟,是否存在相互循环定义的情况。

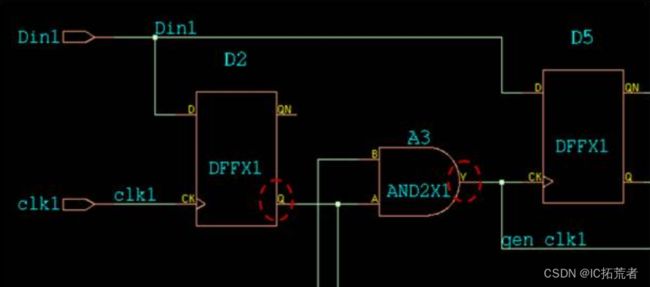

对于如下所示电路施加下面的sdc约束,在check_timing时就会报generated clock定义问题。

数字IC后端设计实现之时序约束generated clock约束

create_clock -name ck1 -period 10 -waveform { 0 5 } [get_ports {clk1}]

create_clock -name ck2 -period 10 -waveform { 0 1 } [get_ports {clk2}]

#create_clock -name ck3 -period 10 -waveform { 0 5 } [get_ports {clk3}]

create_generated_clock -divide_by 2 -name gclk2 -source clk3 divider/Q

set_propagated_clock [get_clocks {ck1}]

set_input_delay 2 -clock [get_clocks {ck1}] [get_ports {in}]

set_output_delay 2 -clock [get_clocks {ck2}] [get_ports {out}]

set_disable_timing -from A -to Y C3

generated clock定义典型错误—source latency 0

还有比如下面这样的电路,我们把分频点定义在AND2的输出端。同样也会报这个时钟定义有问题。

create_clock -name clk1 -period 10 [get_port clk1]

create_generated_clock -name genclk -divide_by 2 -source [get_port clk1] [get_pin A3/Y]

● generic

检查是否存在unmapped的cells,这类generic cell一般是零延时,影响时序检查准确性。这类情况一般比较少见,如果有在逻辑综合或PR阶段就会发现。

● latch_fanout

检查电平触发latch的扇出是不是自身,有没有latch级联的情况

● loops

检查组合逻辑有没有反馈回路,STA对这种反馈回路是不会分析的,需要通过set_disable_timing来打断这种反馈回路

下图所示电路存在timing loops。如果design存在这样的情况,我们必须使用set_disable_timing自己把这个loop断掉,否则工具会自己断,可能会出现工具判断的情况和我们预期不一样的情况。因为工具在分析时序时不支持timing loop!

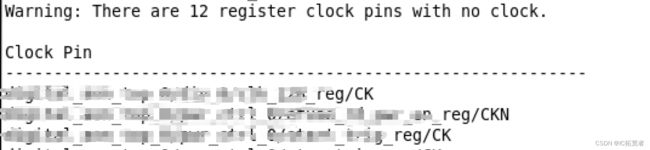

● no_clock

检查是否有时序单元的clock pin不在任何时钟网络上。比如某个寄存器的CK是接到某个data逻辑上或者clock被set_clock_sense(case analysis) 截断导致clock传不过去。

create_clock -name ck -period 10 -waveform { 0 5 } [get_ports {ck}]

create_clock -name ck1 -period 9 -waveform { 0 4.5}

set_input_delay 2 -clock [get_clocks {ck}] [get_ports {in}]

set_input_delay 2 -clock [get_clocks {ck}] [get_ports {in1}]

set_output_delay 2 -clock [get_clocks {ck}] [get_ports {out}]

set_clock_gating_check -setup 0.2 A1

set_clock_gating_check -setup 0.2 O1

set_case_analysis 1 O1/A

● no_input_delay

检查Input Port是否有关联的时钟,否则相关IN2REG路径是unconstrained的。

● partial_input_delay

检查在set_input_delay时,是否存在只指定-min或者-max其中之一的情况

● unconstrained_endpoints

检查时序单元数据Pins或者Output Ports是否没有max delay约束

create_clock -name ck -period 10 -waveform { 0 5 } [get_ports {ck}]

set_propagated_clock [get_clocks {ck}]

set_input_delay 2 -clock [get_clocks {ck}] [get_ports {in}]

set_clock_sense -stop_propagation C1/Y

● unexpandable_clocks

检查相关的clocks之间是否可扩展,在跨两个不同频率的时钟路径上计算时序时,往往需要扩展时钟以计算相应的setup timing

● no_driving_cell

检查Input Port是否定义了驱动单元,工具只会在相连的net有寄生参数存在时才会产生Warning信息