【立创EDA-PCB设计基础】6.布线铺铜实战及细节详解

前言:本文进行布线铺铜实战及详解布线铺铜的细节

在本专栏中【立创EDA-PCB设计基础】前面完成了布线铺铜前的设计规则的设置,接下来进行布线

布局原则是模块化布局(优先布局好确定位置的器件,例如排针、接口、主控芯片)

布线原则是先从复杂的地方开始布线(也就是先从线比较多的地方开始布线,一般是先从主控芯片开始布线(线比较多))

目录

1.主控MCU芯片布线

1.晶振部分布线

2.滤波电容布线

3.排针布线

4.LED走线

2.供电模块布线

1.电源区域放置铺铜

2.差分对步线

3.检查剩余信号线

4.电源和GND布线

1.5v电源布线

2.3v3电源布线

3.GND铺铜

本文布线铺铜后的效果-3D效果

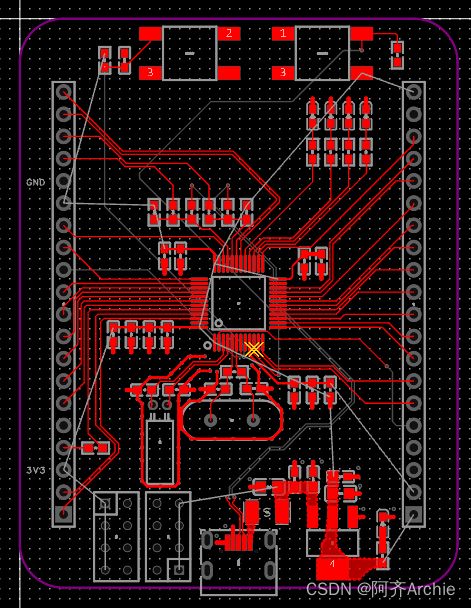

本文布线铺铜后的效果-顶层图

本文布线铺铜后的效果-底层图

布线注意点汇总如下:

1.先顶层走线,当顶层走不了了切换到底层走线(底层最后会铺特别大的一个GND网络的铜皮,原因在于GND网络是我们的最后电源电流的回流路径,电流分散出去最后会汇总到GND,也就是GND上的电流其实也是很大的)。也就是在顶层的GND通过过孔来连入底层,即在顶层时就不考虑导线连接GND了,如下所示

2.进行引脚连接时,可以将其引脚飞线单独打开,便于观察

3.走线尽量横平竖直,尽量选择45度斜角去走线(出现钝角135度),不允许出现直角和锐角

4.焊盘上走线时,走线宽度不能超过焊盘本身的宽度,走线宽度最大和焊盘一样宽

5.对于如下竖型焊盘要如下接触更多焊盘走线,不可侧边走线(其实就是直角了、接触面也少)

6.顶层导线在万不得已的情况下才走底层(底层是备选方案)

7.拐角斜线尽量不要太大也不要太小

8.布线时,左击可暂时确定布线

9.电流部分的过流和过孔要匹配,所以在GND过孔周围再打上一些过孔用来过流/回流,可以再打1/2个(具体多少电流需要计算好,与原理图设计/硬件有关),如下

10.差分信号线长度差应小于等于10mil

11.底层和顶层切换处的夹角可以是90度

12.例如顶层导线有90度夹角,可以做一个圆弧90度过度

圆弧90度过度,选择属性中的移除回路为否

13.在工程设计中,上方栏有图页、网络、元件、对象选项,可以更加方便使用。可以用来检查剩下的未布线的飞线等

1.主控MCU芯片布线

打开实时DRC检测,布线时动态提醒错误

设置单路布线快捷键W,便于后面快捷布线,点击应用,确认,设置完成

按住W,点击焊盘,就会出现红色的线(铜皮)

查看右侧属性栏,首先将单位更换为mil,然后将常见设置中的起始布线宽度设置为跟随规则(也就是本专栏中此文上一篇对布线前的设计规则的设置),然后将起始打孔尺寸也设置为跟随规则,然后布线模式选择为阻挡(常用,就是布线若距离过小会出现白色框提示,会放置不了被阻挡),然后移除回路选择是

1.晶振部分布线

首先开始晶振部分的布线

按住Shift + S ,可以看到颜色变了,红色更凸显,将丝印隐藏

可以看到里面有线头,将其整理一下,删除多余线头

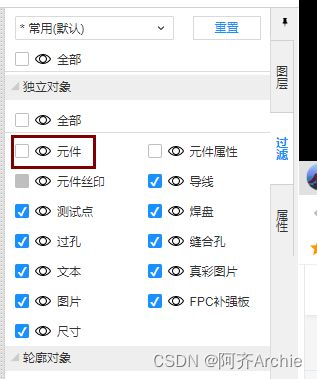

在过滤中将元件取消掉,点击元件内的导线就不会选中元件了

对于晶振部分还要做一个包地处理。就是在晶振周围外部走一圈GND的信号线(12mil,是它普通信号线宽的两倍)。还在包地上放置过孔处理

包地处理的原因:因为晶振是产生脉冲信号的,对于我们这个板子来说8M是很大的速率了,为了防止其它信号来影响晶振的8M的脉冲,会给带来一些纹波等影响,利用包地的方法来隔绝掉外界对晶振的干扰。同时经过包地的方法,去掉它晶振对外面电路的影响,

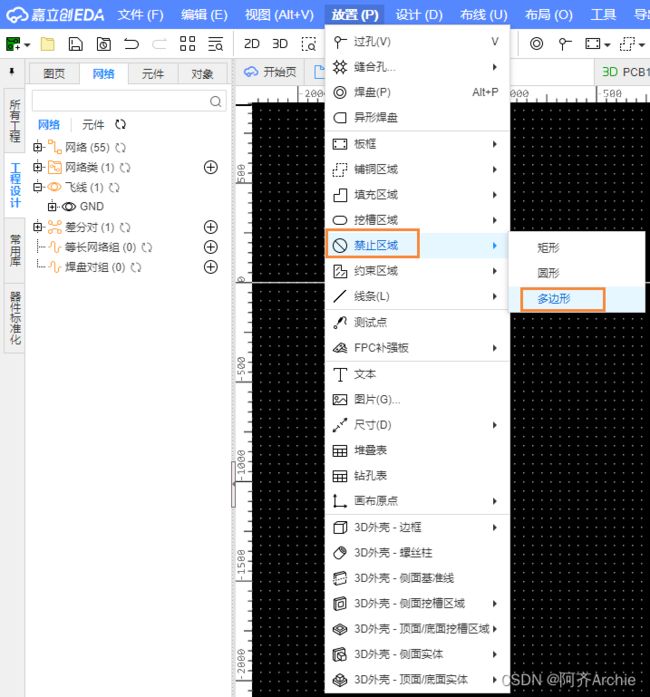

对于晶振部分还要做一个多层禁止铺铜区域的处理。晶振区域顶层和底层或者多层都不能进行铺铜(最后会整体板子铺铜,空的地方都会铺上GND的铜皮,需要将晶振与地平面隔离开,这样子地平面上的干扰就不会传到晶振的信号线,晶振信号线也不好将干扰通过地平面传播出去)

点击放置--禁止区域--多边形

选择图层--多层,禁止选项--铺铜

可以围绕着包底进行绘制区域 ,要将两个信号线完全包里面

另一个晶振的禁止区域绘制

以上,晶振部分(8M和32.768khz)走线就结束了

2.滤波电容布线

接下来对VDDA和VCC_3V3的滤波电容进行布线,如下四个绿框内为滤波电容布线,需要注意的是焊盘走线出去的要接触面要大,不可侧边引出走线,GND直接通过过孔切换到底层。

3.排针布线

接下来对排针部分引脚进行布线,显示排针块的引脚飞线

排针电源和GND先不连,将其飞线隐藏

可以看到目前还有四个引脚没有连接(被其它导线挡住了),下一步进行一些调整

其中右侧排针中顶层被挡着的线,打过孔切换到底层走线

注意:排针上的焊盘是通孔焊盘 (本身就具有过孔的属性、内壁有铜皮)。其它的贴片焊盘是在顶层,只能和顶层的走线进行连接

左排针经过调整,目前除电源和GND引脚只剩一个12NRST没有走线, 进行打过孔切换到底层走线。

对于NRST引脚, 进行打过孔切换到底层走线

使用切换到顶层和切换到底层的快捷键,可以快速切层自动打孔。也可以使用打孔时自动切层功能来快捷打孔切层

4.LED走线

然后将四个led进行走线 (led记得接GND,下图1没加,图2补充),主控MUC走线完成。

2.供电模块布线

电源部分的线宽要大一点以便足够大的电流通过(放置铺铜区域的方式走线可以让载流很大)

使用铺铜代替走线,相比于走线有较大的线宽。铺铜就是直接放一个区域的铜皮

1.电源区域放置铺铜

在设计规则中设置,铺铜单层焊盘和多层焊盘的连接方式为直连(直流与发散的区别见下文)。点击应用,确定。

然后开始放置铺铜区域,选择多边形铺铜

绘制完轮廓后,点击确认

然后进行铺铜区域的调整,调整完的话,点击铺铜区域点击右键,点击重建所选即可重新铺铜该区域,区域完铺铜成。

铺铜单层焊盘和多层焊盘的连接方式为直连(也叫全连接)与发散(也叫十字连接)的区别:

下图为直连方式铺铜的效果

下面看一下发散方式铺铜的效果:

首先在设计规则中修改连接方式为发散,修改变大发散线宽会使得十字连接线宽变大

右键点击铺铜区域,点击重建所选,发散方式效果如下

区别就是:

1.直连是将焊盘也铺上了铜皮,而发散方式是与焊盘十字连接。

2.手工焊接选择发散方式铺铜,机器焊接选址直连方式铺铜(因为:直连方式铺铜散热会很好,不利于热焊盘融化锡,然后锡粘贴元器件)

但是,小块的直连铺铜也不影响手工焊接(因为本身面积小,散热也不会太夸张)

在多边形铺铜区域绘制时,尽量多点几下,会多出几个调节点,便于区域形状的绘制。

绘制铺铜区域时,以包裹性思维去绘制。

然后将电源模块GND打过孔切换到底层

然后电源部分的导线连接,如下部分,导线线宽要大一些(电流也不小的)

需要注意:电流部分的过流和过孔要匹配,所以在GND过孔周围再打上一些过孔用来过流/回流,可以再打1/2个(具体多少电流需要计算好,与原理图设计/硬件有关)

2.差分对步线

然后打开电源模块的飞线,检测还有无需要连接的地方,可以知道下一步需要连接D+ D-差分信号

在本专栏前面文章中我们已经将该D+ D-设置为了差分对了,接下来进行差分对布线

在设计里的差分对管理器中可以查看设置的差分对

该差分对位DPA

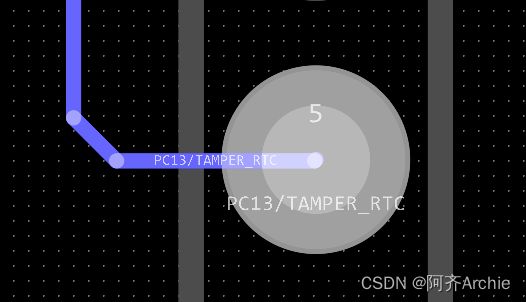

点击布线中的差分对布线, 在差分对信号线就会自动有两个线走出来,保证两条线的长度保持一致,

差分信号对顶层切换到低层再切换到顶层进行连接。

若两条差分信号的长度不一,可点击等长调节来调整

补充:放置铺铜区域与放置填充区域的区别。

如下,进行放置填充区域

如下左侧为填充区域方式铺铜,左侧为放置铺铜区域铺铜

放置填充区域和放置铺铜区域都是进行铺铜

区别:

放置填充区域不会自动避让不是同一网络的焊盘

放置铺铜区域会自动避让不是同一网络的焊盘

例如如下,放置填充区域不会自动避让不是同一网络的$1n2040

例如如下,放置铺铜区域会自动避让不是同一网络的$1n2040

3.检查剩余信号线

全选,然后显示全部飞线

然后去掉电源VCC和GND飞线,可以看到信号线只剩一个没有连接

整理完毕,目前信号线已全部连接

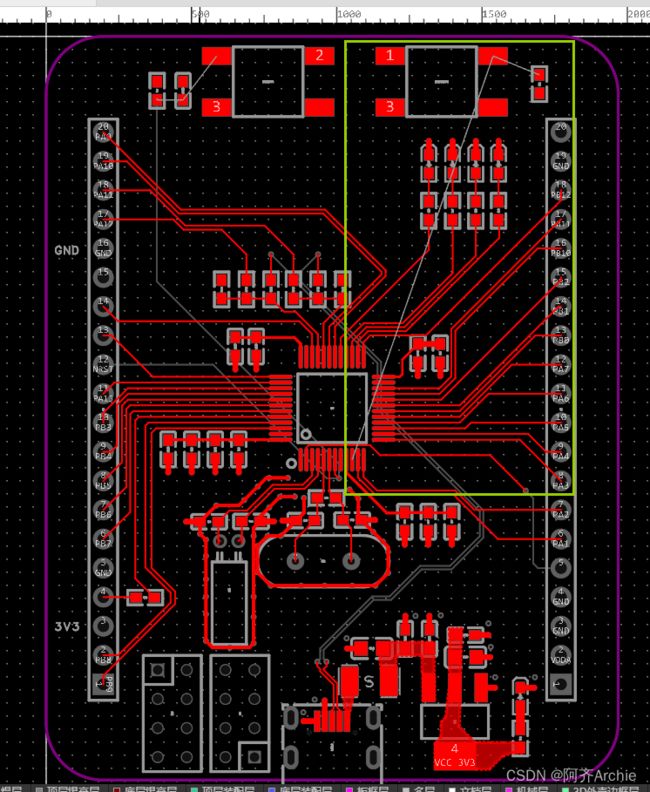

顶层图如下

底层图如下

4.电源和GND布线

1.5v电源布线

首先全选,将所有飞线打开,单独取消GND的飞线,如下图目前显示的是电源的飞线

选中例如5V电源,高亮显示,点击5V电源,右键选中高亮网络显示

那么接下来先连接5v的网络,如下所示,使用30mil的线宽引出过滤后的5v到排针

2.3v3电源布线

3.3v电源是从C17电容滤波后出来的

电源3v3布线完成

顶层图如下

底层图如下

补充:修正垂直90度时,加了圆弧90度过度的线进行修复时,选择属性中的移除回路为否,不会影响修复

3.GND铺铜

1.首先进行底层铺铜

切换到底层

点击放置--铺铜区域--矩形

矩形全选板子

默认点击确认

底层铺铜效果如下。可以看到刚刚禁止的晶振部分没有铺铜 ,会自动避让底层的3v3等电源走线

2.顶层铺铜

切换到顶层

放置矩形铺铜区域,默认选项,点击确认

顶层铺铜效果如下

可以看到左侧工程设计中的飞线数量(GND)没有了 ,证明所有网络都连接好了

以上,布线全部结束。下一步进行DRC检测,详见本专栏中基础文章的下一篇。

铺铜设置相关补充:

1.调整板框与铺铜边界的距离,以及调整铺铜区域与避让网络之间的间距,可以通过如下设计规则中的网络间距等进行调整

2.铺铜区域的填充样式中,还有网格45度和90度, 网格状的铺铜适用于电脑的主板上比较多,韧性比较好,承受压力性强,不易弯曲折断,对PCB有一定韧性要求的情况下可以用网格状填充。一般我们都是用全填充

默认是不保留孤岛,就是移除没有用到的铜皮区域,没有与外界进行连接

如下中间部分就有一个孤岛

移除孤岛如下所示

补充:

在工程设计中,上方栏有图页、网络、元件、对象选项

点击网络,可以方便找到对应的网络 。里面的飞线也可以进行显示或隐藏某个网络的飞线。可以用来检查剩下的未布线的飞线