FPGA原理与结构(8)——块RAM(Block RAM,BRAM)

系列文章目录:FPGA原理与结构(0)——目录与传送门

一、BRAM简介

大家对于RAM应该并不陌生,RAM就是一张可读可写的存储表,它经常被拿来与ROM进行对比,相比之下,ROM只可读。而在FPGA中,RAM一般可以分成两种,一种是使用LUT资源组成的分布式RAM(DRAM),另一种就是块RAM(BRAM),这里我们讨论的是BRAM,关于DRAM的内容,可以阅读:FPGA原理与结构——分布式RAM(Distributed RAM,DRAM)。

BRAM就是嵌入在FPGA中的整块的RAM资源,是FPGA中重要的存储资源。在早期的FPGA架构中,基本上只使用基于查找表和触发器的逻辑块实现用户电路,可用作存储要素的就只有逻辑块中的触发器。因此很难在芯片上保存大量数据,而有这样需求的应用需要在FPGA上连接外部存储器。但是在很多情况下,FPGA和外部存储器的带宽会成为系统的瓶颈,从而限制整体性能。因此商用的FPGA架构在发展中开始集成高效的片上存储器。这就是我们BRAM的由来。

二、BRAM的特性和分布

在xilinx 7系类的FPGA里,一个BRAM的大小是36Kb,它也可以被拆分成2个独立的18Kb BRAM来使用,这就是xilinx 7系类里RAM的最小实现形式了。也就是说使用的BRAM在使用的时候必须是整块进行使用的,一块BRAM最小就是18Kb。举个例子,我们需要存储40Kb的资源,就需要使用:一块36Kb的RAM+一块18Kb的RAM,这样就造成了14Kb的资源浪费。

两个相邻的RAM还可以组合来构成更大的RAM。

每块36Kb的RAM根据深度和位宽的不同,可以配置成如下形式(深度×位宽):32K x 1, 16K x 2, 8K x 4, 4K x 9, 2K x 18, 1K x 36, or 512 x 72(简单双端口模式下,后面会详细说)。

每块18Kb的RAM根据深度和位宽的不同,可以配置成如下形式(深度×位宽):16K x 1, 8K x2 , 4K x 4, 2K x 9, 1K x 18 or 512 x 36(简单双端口模式下,后面会详细说)。

根据FPGA型号的不同,每块FPGA中蕴含的BRAM资源数量也是不一样的,用户可以根据自己的需求和成本选择最适合自己的型号,我们以下图为例,这只是xilinx的一部分型号对应的BRAM资源,可以看到不同的device对应的BRAM数量和分布情况有所不同。

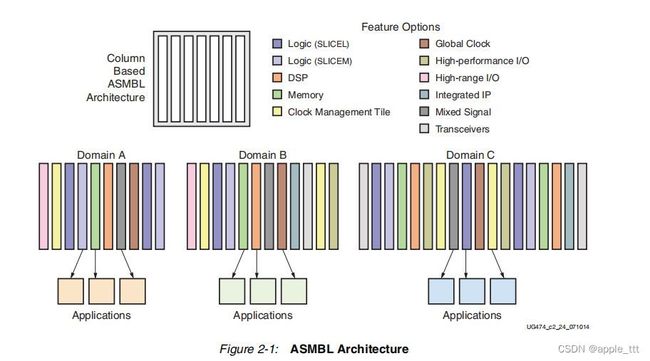

在如今xilinx的FPGA中普遍使用的是ASMBL架构,所以BRAM在FPGA也是按列分布的。

三、BRAM的使用

BRAM的作用是非常巨大的,也是具有一定复杂性的,BRAM可以被配置成RAM,ROM或者FIFO,我们一个一个来讨论。

1、RAM

首先就是最直观的RAM的情况,但是就算是用作RAM,也有着许多不同的工作模式:

(1)Single Port :单口 RAM

读写共用一个地址总线,在同一个端口,但是不能同时进行

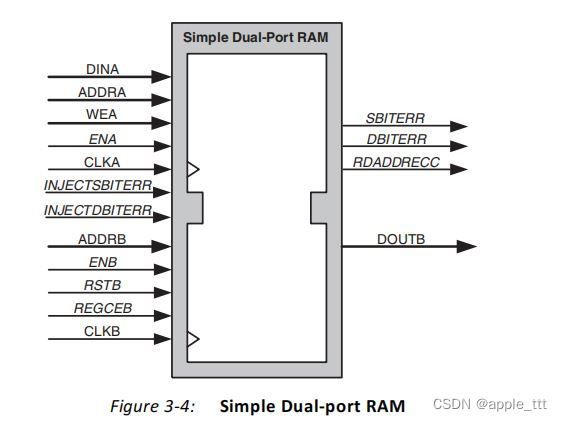

(2)Simple dual port:简单双口 RAM

一个写通道,一个读通道,通过A端口写入数据的同时可以通过B端口读出数据

(3)True Dual Port:真双口 RAM

两个通道都支持读写,互相独立。A端口和B端口可同时读写数据

2、ROM

ROM其实也非常好理解,甚至是BRAM应用中最简单的部分,因为ROM可以理解成只具备读功能,不具备写功能的RAM。

(1)Single Port :单口 ROM

不能写入,只有一个端口用于数据读

![]()

(2)Dual port:双端口 ROM

不可写,但是有2个端口用于读,两个端口读取数据的位宽可以不同,但是必须是整数倍关系

![]()

3、FIFO

FIFO是英文First In First Out 的缩写,是一种先进先出的数据缓存器,与普通存储器的区别是没有外部读写地址线,使用简单,缺点就是只能顺序读、写入数据,其数据地址由内部读写指针自动加1完成,不能像普通存储器那样可以由地址线决定读取或写入某个指定的地址。

FIFO的作用:

(1)不同时钟域之间的数据传输;

(2)对不同宽度的数据位宽转换;

(3)数据缓存

根据FIFO工作的时钟域,可以将FIFO分为:

(1)同步FIFO:读时钟和写时钟为同一个时钟,在时钟沿来临时同时发生读写操作。

作用:位宽转换或数据缓存。

(2)异步FIFO:读写时钟不一致,读写操作是互相独立的。

作用:多比特数据跨时钟域。

四、7系类BRAM的一些额外特性

1、可选输出寄存器

BRAM的输出还内嵌了个寄存器,我们打拍输出的时候可以使用它,这样就能省下SLICE上的寄存器资源,而且就算我们使用SLICE的FF资源,会引入一个较大的时延,这样做还能降低时延问题。

2、BRAM的级联

在xilinx的FPGA里,2块相邻的BRAM可以在不消耗CLB资源的情况下就级联形成更大的RAM。任意两个相邻的BRAM都可以进行级联