数字逻辑Verilog描述电路的方法(2022.3.17)

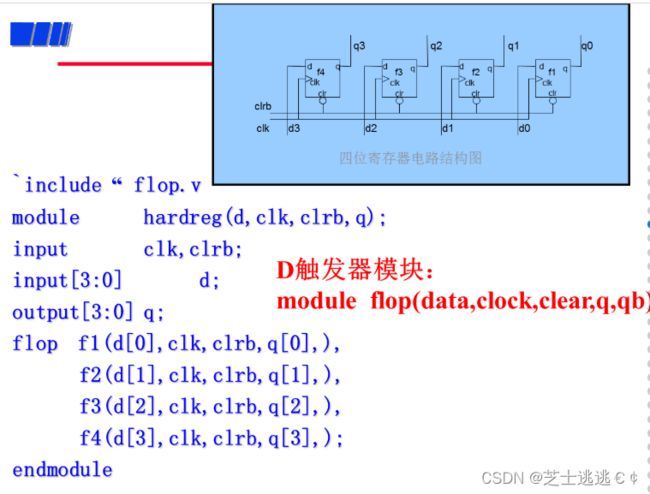

一、结构描述

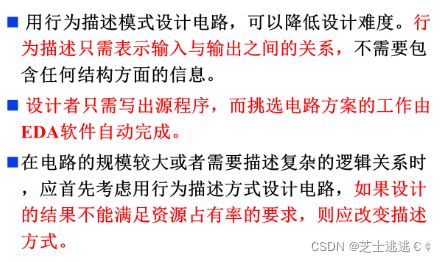

二、用行为描述的方法

1.D触发器有一个异步复位端clrb

module dff(d,clk,clrb,q);

input clk,clrb;

input d;

output q;

reg q;

always@(posedge clk or posedge clkb)

begin

if(clrb)

q<=0;

else

q<=d;

end

endmodule2.采用行为描述时注意事项

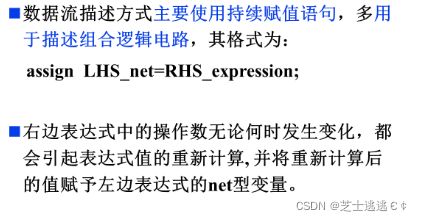

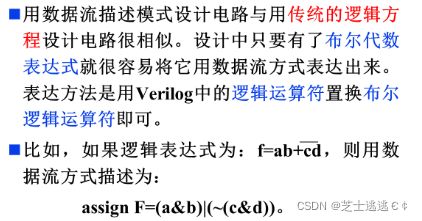

三、数据流描述

![]()

数据流描述的2选1MUX

module MUX3(out,a,b,sel);

output out;

input a,b,sel;

assign out=(a&(~b))|(b&sel);

endmodulemodule MUXS(out,a,b,sel);

output out;

input a,b,sel;

assign out=sel?b:a;

endmodule

三、结构描述

1.结构描述的1位全加器

真值表-->逻辑表达式-->电路结构图-->VerilogHDL

module full_add1(a,b,cin,sum,cout);

input a,b,cin;

output sum,cout;

wire s1,m1,m2,m3;

and m1(m1,a,b);

m2(m2,b,cin);

m3(m3,a,cin);

xor s1(s1,a,b);

sum(sum,s1,cin);

or cout(cout,m1,m2,m3);

endmodule2.数据流描述的1位全加器

方法一

module full_add1(a,b,cin,sum,cout);

input a,b,cin;

output sum,out;

assign sum=a^b^b^cin;

assign cout=(a&b)|(b&cin)|(a&cin);

endmodule方法二

module full_add1(a,b,cin,sum,cout);

input a,b,cin;

output sum,cout;

assign {cout,sum}=a+b+cin;

endmodule3.行为描述

module dull_add1(a,b,cin,sum,cout);

input a,b,cin;

output sum,cout;

reg sum,cout,m1,m2,m3;

always@(a or b or cin)

begin

{cout,sum}=a+b+cin;

end

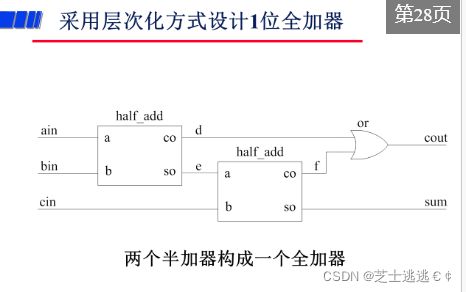

endmodule用模块化方式设计的1位全加器顶层设计

module fuu_add(ain,bin,cin,sum,out);

input ain,bin,cin;

output sum,cout;

wire d,e,f;

half_add u1(ain,bin,e,d);//半加器模块调用

half_add u2(e,cin,sum,f);

or u3(cout,d,f);//或门调用

endmodule【例】半加器定义

module half_add(a,b,so,co);

input a,b;

output so,co;

assign co=a&b;

assign so=a^b;

emdmodule4位加法器

//结构描述

'include "full_add1.v"

module add4_1(sum,cout,a,b,cin);

output[3:0] sum;

output cout;

input [3:0]a,b;

input cin;

full_add1 f0(a[0],b[0],cin,sum[0],cin1);

full_add2 f1(a[1],b[1],cin1,sum[1],cin2);

full_add3 f2(a[2],b[2],cin2.sum[2],cin3);

full_add4 f3(a[3],b[3],cin3,sum[3],cout);

endmodule

//数据流描述

module add4_2(cout,sum,a,b,cin);

output[3:0] sum;

output cout;

input[3:0] a,b;

input cin;

assgin {cout,sum}=a+b+cin;

endmodule

//行为描述

module add4_1(cout,sum,a,b,cin);

output[3:0] sum;

output cout;

input[3:0]a,b;

input cin;

reg[3:0] sum;

reg cout;

always@(a or b or cin)

begin

{cout,sum}=a+b+cin;

end

module

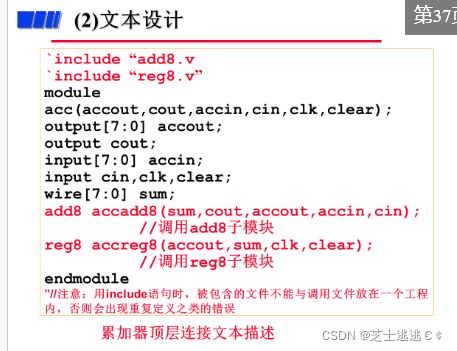

四、多层次结构电路的设计

Top-down 方法

可以采用文本方式,也可以用图形和文本混合设计的方式。