ISE中逻辑分析仪ChipScope的使用

文章目录

- 一、ChipScope介绍

- 二、ChipScope的使用

-

- 设置注意

- Net查找技巧

- 各触发方式对应符号表

- 参考资料

一、ChipScope介绍

ISE 软件的嵌入式逻辑分析仪 ChipScope Pro 基本上采用了典型外部逻辑分析仪的理念和功能,却无需额外的逻辑分析设备、测试 I/O、电路板走线和探点,只要建立一个对应的文件并做相关设置后,与当前工程捆绑编译,用一根 JTAG 接口的下载电缆连接到要调试的 FPGA 器件即可。ChipScope 对 FPGA 的引脚和内部的连线信号进行捕获后,将数据存储在一定的 RAM 块中。因此,用于保存采样时钟信号和被捕获的待测信号的 RAM 块,也会占用逻辑资源(LE)、Memory 资源(Block RAM)和布线资源。占用逻辑资源的多少基于信号或者被监测的通道数量,以及触发条件的复杂程度;所使用的存储器数量取决于被监测的通道数量和采样深度。

二、ChipScope的使用

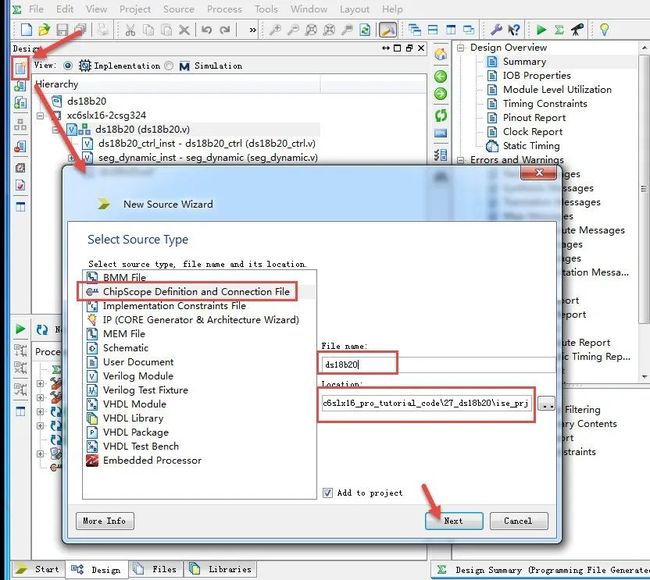

创建ChipScope 核之前,先点击Synthesize-XST把整个工程代码和约束文件综合一遍,之后如图 1 所示,选中“ChipScope Definition and Connection File”来新建一个 ChipScope 核,并将 ChipScope 核命名,将其存储在工程目录下。设置完之后点击 Next。

图 1

接下来出现的页面我们直接点击“Finish”即可,如图 2 所示:

图 2

设置注意

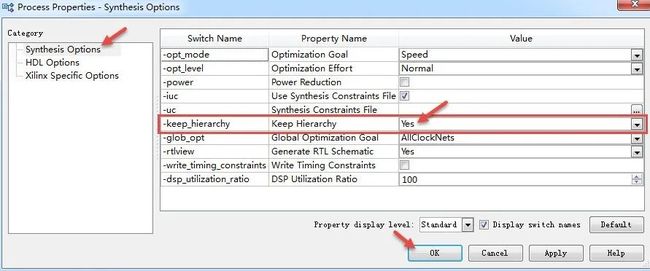

如图 3 所示,生成之后可以看到工程中多了一个xxxx.cdc核文件,双击该文件可以对ChipScope核进行配置,不过在配置之前我们先进行一个较为重要的设置。如图 4 所示,右键“Synthesize – XST”后点击“Process Properties…”,点击后出现如图 5 所示页面,这里我们将keep Hierarchy栏中选择Yes(原默认为No。也有使用soft的,Yes和Soft的区别暂不明确)。**这样设置是方便我们找到所想观察的信号,否则,很多信号会被优化掉,导致ChipScope找不到。**设置完之后,双击工程中的xxxx.cdc文件,进行ChipScope核的配置。

图 3

图 4

图 5

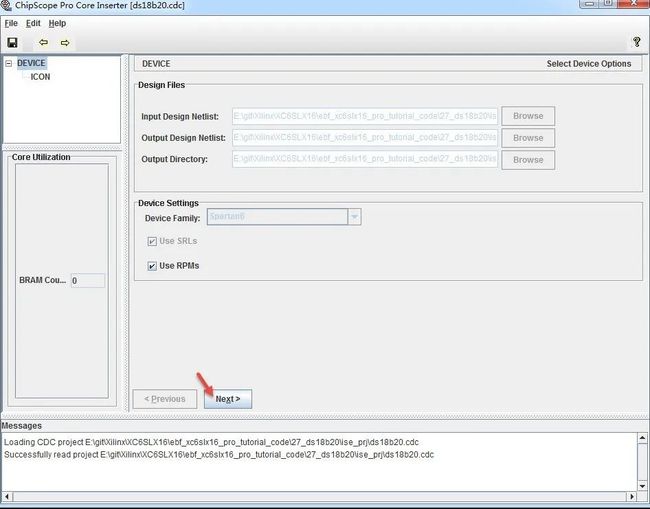

双击工程中的xxxx.cdc文件后出现如图 6 所示页面,该页面我们按默认设置即可,直接点击Next:

如图 7 所示,同样的该页面我们也保持默认设置即可,直接点击Next:

如图 8 所示这里我们先把Trigger Width(触发信号数)选择为最大值256,在我们添加完需要观察的信号后,再根据添加的信号数回来进行更改,这样能有效的节省配置时间,如果事先可以确定观察的信号数也可以直接设置。该页面我们只需将Trigger Width选择为最大值256即可,其他设置不变,点击Next:

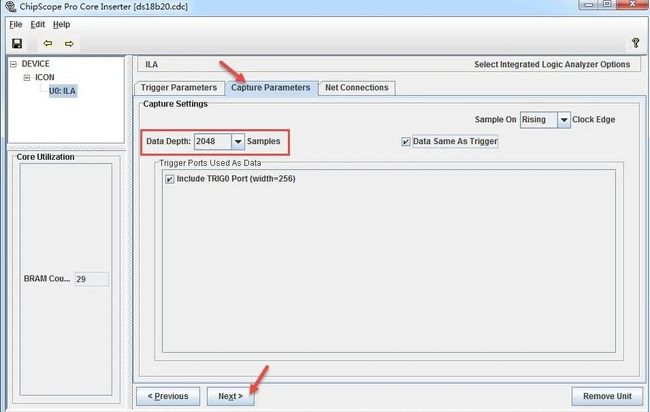

如图 9 所示,在该页面我们将Data Depth(采样深度)设置为2048,在不超过FPGA的存储量内该设置可根据实际抓取情况进行设置,设置的值越大所占的存储空间就越大,其余设置按默认设置即可,点击Next:

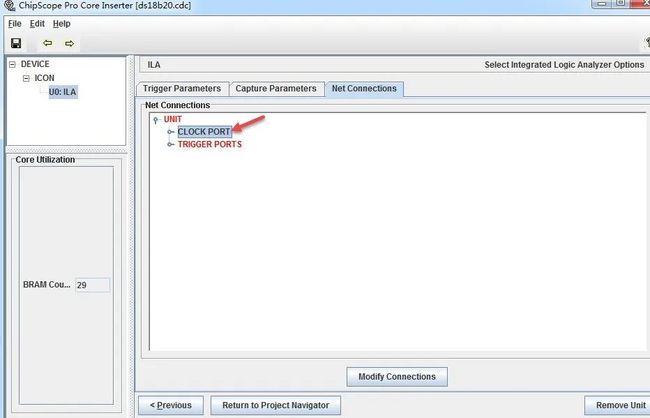

如图 10 所示,双击CLOCK PORT来添加时钟信号。

图 10

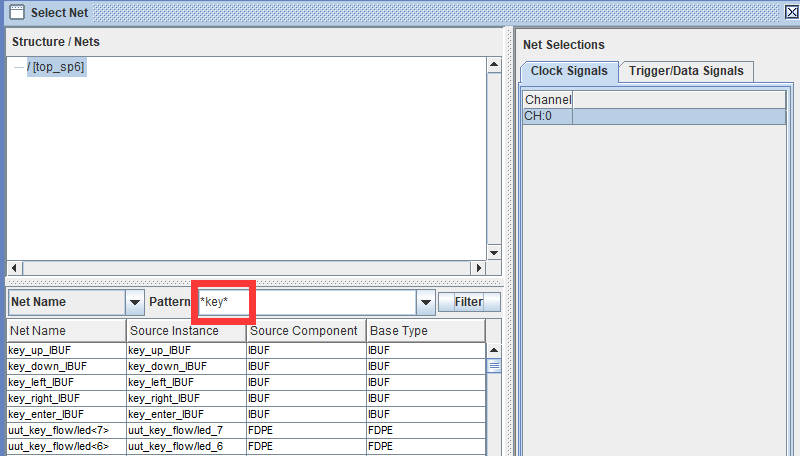

如图 11 所示,我们选择ds18b20_ctrl模块的clk_1us作为采样时钟,选中后点击Make Connections进行添加(这里需要注意的是我们选择的采样时钟信号必须是带有buffer的信号,否则会报错)。时钟信号添加完之后,我们切换到Trigger/Data Signal进行采样信号的添加,如图 12 所示:

图 11

图 12

如图 13 所示,我们添加采样信号(添加的信号越多所占的空间越大),添加完成之后点击OK,点击OK后如图 14 所示,发现TRIGGER PORTS显示为红色,这是因为前面图 8 配置的采样端口数设置的是256,与我们添加的信号数不匹配,这里我们点击Previous回到Trigger Parameters页面将Trigger Width(触发信号数)设置为48,如图 15 所示:

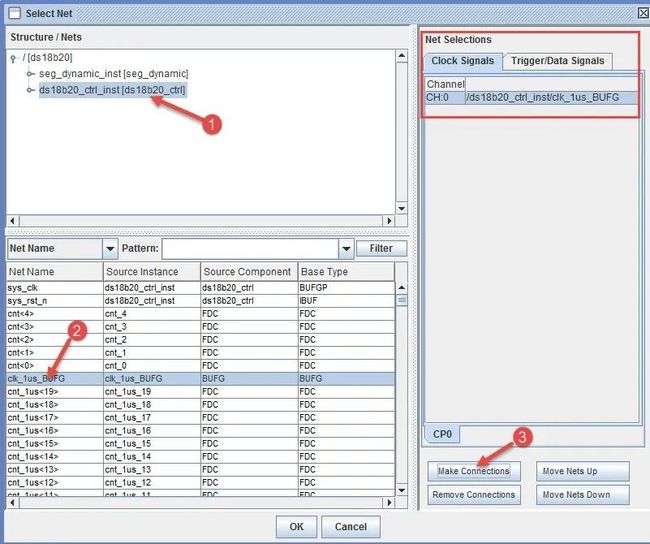

Net查找技巧

这里说一个Net查找技巧。当我们在设置Clock Signals 和 Trigger/Data Signal时由于Net太多难以快速查到需要的。此时可以利用Filter功能过滤,如图 16使用key,即可选出所有带有key的Net。

图 16

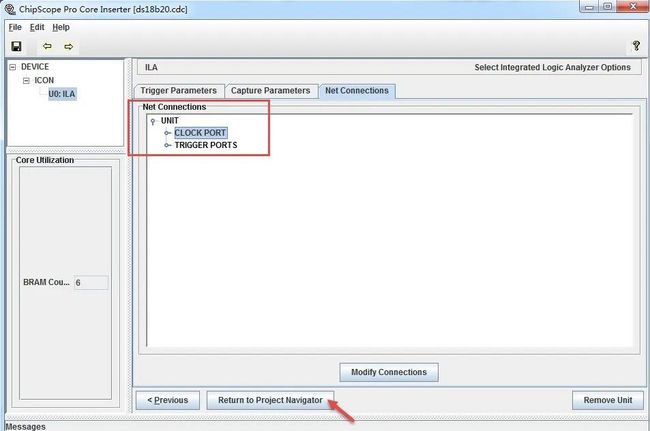

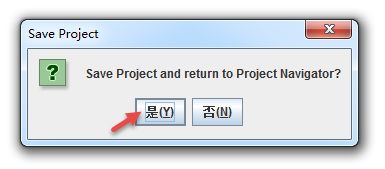

如图 17 所示,设置完之后可以看到TRIGGER PORTS显示为黑色了,说明配置成功了,最后点击Return to Project Navigator完成配置,点击之后出现如图 18 所示,点击“是”。

图 18

配置完成之后就可以进行波形图的查看了,全编译完成之后,将电源与下载线与开发板连接好,连接好上电之后,双击“Analyze Design Using ChipScope”进入ChipScope波形抓取界面,如图 19 所示:

图 19

如图 20 所示,进去之后,首先点击左上角箭头所指图标,跟开发板建立连接。

图 20

如图 21 所示,若开发板和JTAG连接正常的话,则ChipScope就能找到开发板使用的FPGA芯片,可以看到正是我们使用的芯片信号XC6SLX16,直接点击“OK”

图 21

如图 22 所示,连接成功后可以看到左上角P图变为绿色了,说明连接成功了。然后我们右键“DEV:0 MyDevice0(XC6SLX16)”,点击“Configure…”来添加bit文件。

图 22

如图 23 所示,其中1框中是我们连接的bit文件信息,包括文件名以及存储位置(检查是否是该工程的bit文件),如果不是我们也可以通过点击“Select New File”来添加新的bit文件,勾选Import Design-level CDC File和Auto-create Buses两个选项,完成后点击“OK”。

图 23

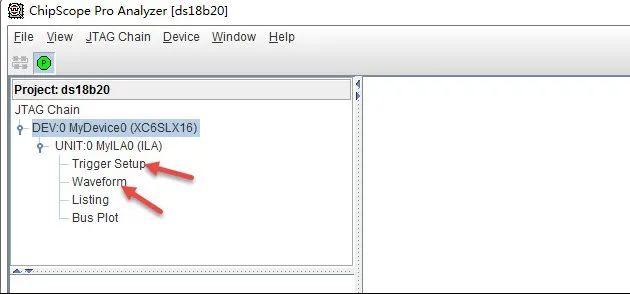

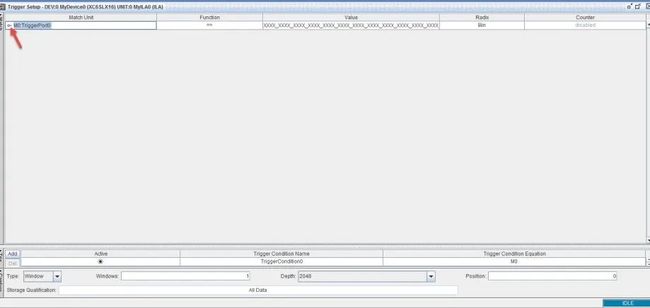

如图 24 所示,我们分别双击“Trigger Setup”和“Waveform”,点击后界面如图 25 所示。其中“Trigger Setup”为触发设置窗口,“Waveform”为波形图窗口。

图 24

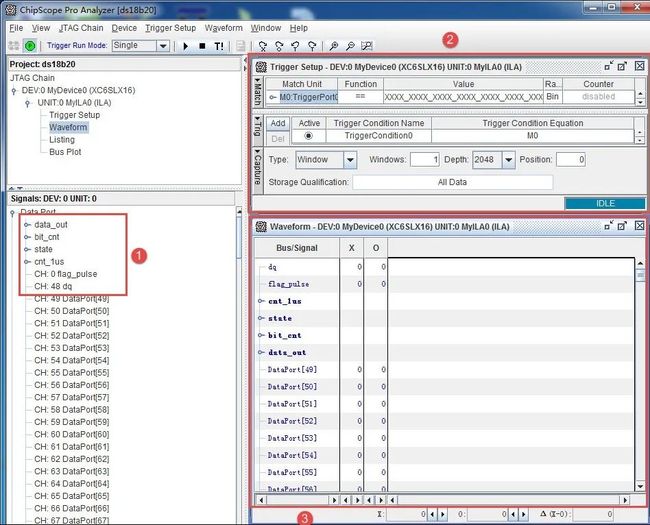

如图 26 所示,可以在界面中看到我们之前加入的一些信号。有些被识别出为总线并在波形窗口显示。

图 26

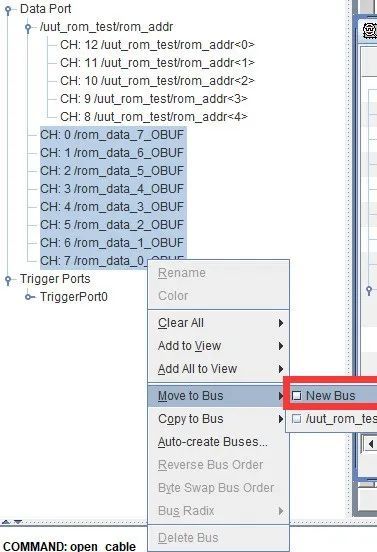

若有部分信号为多位宽信号,那么我们可选中对应的端口(按住ctrl可选择多个,或者按住shift后点第一个和最后一个可以进行连续选中),通过右键点击Move to bus -> New Bus将这些信号进行设置,如图 27 所示。同时信号也被增加到波形窗口显示了,如图 28 所示。

图 27

图 28

如图 29 所示,其中1框中是端口名;2框中可设置波形图的采样触发信号,触发前波形图的长度等;3框中为波形图显示框。

如图 30 所示,箭头1所指是窗口最小化,箭头2所指是窗口最大化,我们将窗口最大化,来设置触发信号。

图 30

如图 31 所示,点击箭头所指的钥匙形状将信号展开设置触发信号。

图 31

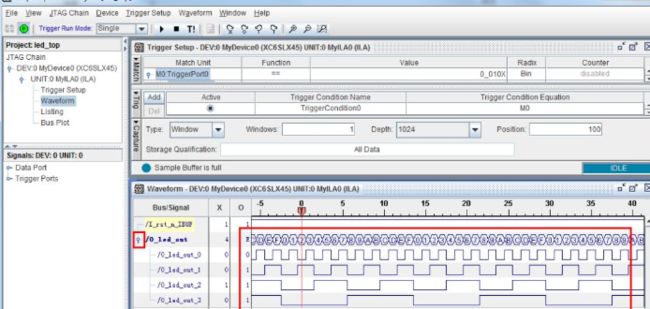

展开后如图 32 所示,其中我们可在1框Value栏设置触发方式;可在2框中设置触发长度,由于我们调用ILA核时设置的采样长度为2048,故这里最大只能设置为2048;3框可设置触发前波形图的显示单位,比如我们设置为100,则波形图则会从触发条件前100个单位开始显示。

图 32

如图 33 所示,这里我们对触发信号设置触发方式(value值),各触发方式所对应的符号详见表格。

各触发方式对应符号表

| 触发方式 | 对应符号 |

|---|---|

| 低电平 | 0 |

| 高电平 | 1 |

| 不定值 | X |

| 上升沿(Rising) | R |

| 下降沿(Falling) | F |

| 双边沿(Both Edge) | B |

| 非边沿(No Edge) | N |

| 等于 | = |

| 不等于 | <> |

| 小于 | < |

| 小于等于 | <= |

| 大于 | > |

| 大于等于 | >= |

如图 34 所示,设置完之后我们点击箭头1就可以进行波形抓取了,若采到你设置的触发,则就会在Waveform串口看到抓取的波形图,我们可点击放大图标进行最大化查看。若你设置的触发不存在,则波形将会抓取不到,这是需重新设置触发,重新进行抓取。

图 34

最大化后波形图如图 35 中 1框中所示,我们可点击2框中的图标进行波形图的放大以及缩小。

在波形窗口处按住鼠标左键画一个矩形框后点Zoom Area可以对框选窗口放大,看到更多的波形细节,如图 36 所示。

图 36

如我们想更改显示信号的进制数,可选择我们需要的更改的信号,右键选择Bus Radix,如图 37 所示,这里我们将data_out改为10进制数显示,只需点击“Unsigned Decimal”即可,点击后出现如图 38 所示界面,点击“OK”即可。

图 37

图 38

如果要查看总线每一个bit的波形情况,可以点击一下图 39 中信号名前面的钥匙形状展开。

图 39

如果需要查看总线的模拟波形,双击Bus Plot,在弹出的界面图 40 中勾选需要查看的总线。

图 40

最后根据抓取的波形图进行分析波形图是否与我们设计的结果一致,若不正确可根据抓取的波形图进行分析问题出在哪里,找出问题,回去更改代码后,重新进行编译,编译完成后需重新配置bit文件,即重复图 23 所示步骤。如此反复直到实现出与实际设计相符的的波形图为止。

参考资料

本文内容参考《FPGA Verilog开发实战指南——基于Xilinx Spartan6》第36章